FFT code bit inverse sequence algorithm vectorization implementation method and device based on shuffling operation

An implementation method and vector technology, which is applied in the field of signal processing, can solve the problems of occupying processor memory space, calculation speed depends on calculation efficiency, and hardware circuit structure realizes single function, so as to speed up, save time and space, and save hardware resources Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0068] The present invention will be further described below in conjunction with the accompanying drawings and specific preferred embodiments, but the protection scope of the present invention is not limited thereby.

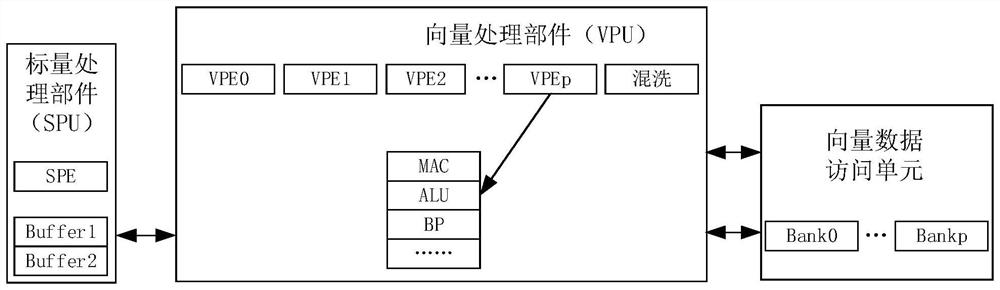

[0069] Such as Figure 4 As shown, in this embodiment, the vectorization implementation method of the FFT code bit reverse order algorithm based on the shuffling operation includes:

[0070] 1) The data that needs to be processed in "code bit reverse order" is loaded into x registers respectively in the p vector processing units VPE of the vector processing unit VPU to form vector data;

[0071] 2) Configure the shuffling mode memory, and write the i-th shuffling rule D containing p-digit values into the i-th address of the shuffling mode memory i , the i-th shuffling rule D i Each digit in indicates the location of the data source of the current location;

[0072] 3) traverse and select a shuffling rule as the current shuffling mode;

[0073] 4) Based on ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More