Delay estimation method and device of programmable logic device, equipment and storage medium

A technology for programming logic and devices, applied in computer-aided design, instrumentation, computing, etc., can solve the problems of high memory overhead of programmable logic devices, impact on performance and efficiency of routing algorithms, and large gap between delay and estimated delay, etc. Achieve the effect of improving the efficiency of routing algorithms, improving the orientation of routing expansion, and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

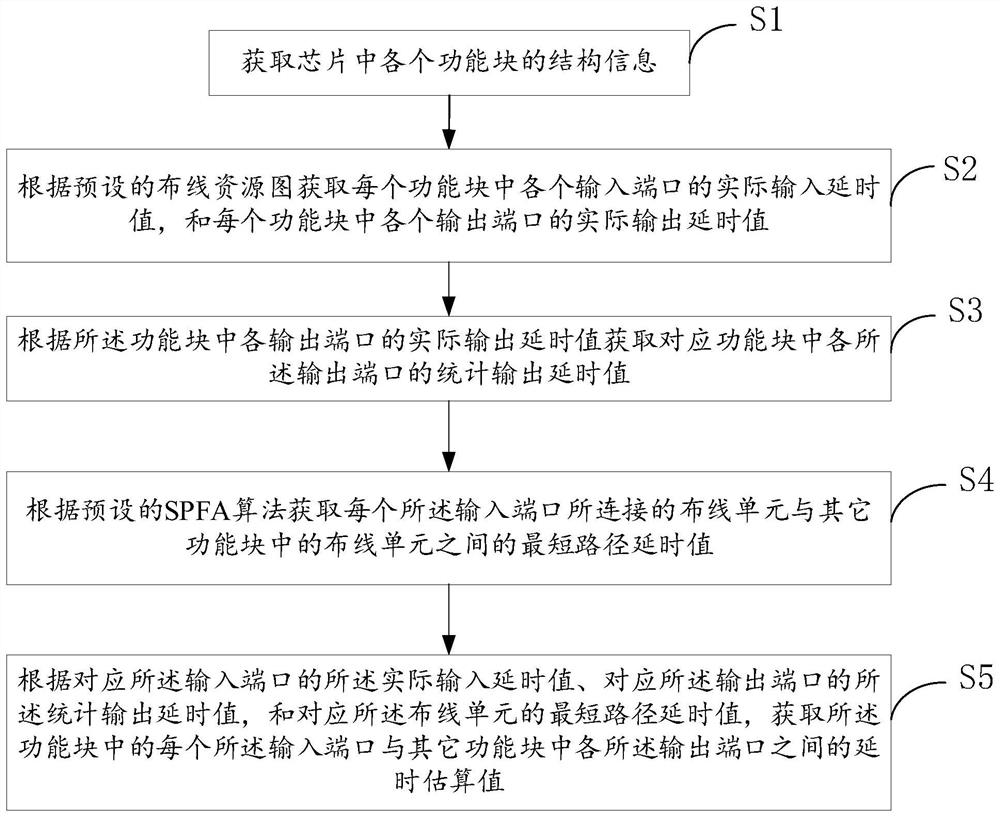

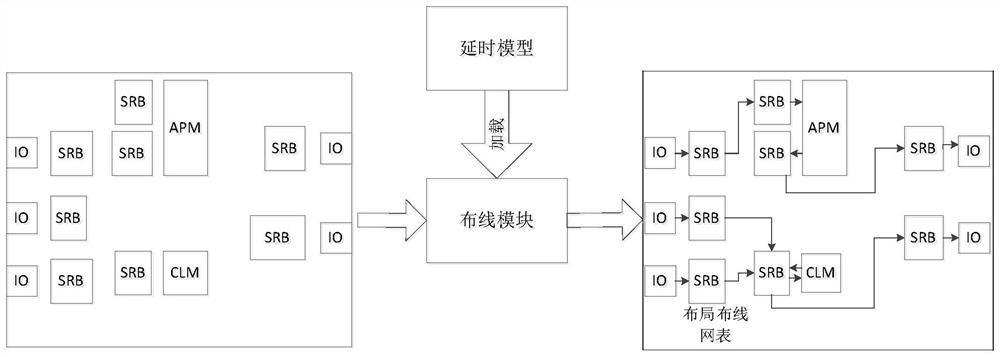

[0040] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0041] The terms "first", "second", and "third" in the present invention are only used for descriptive purposes, and cannot be understood as indicating or implying relative importance or implicitly specifying the quantity of indicated technical features. Thus, features defined as "first", "second", and "third" may explicitly or implicitly include at least one of these features. In the description of the present invention, "plurality" means at least two, such a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More