Three-dimensional chip testing method, device and system

A technology of three-dimensional chips and testing methods, which is applied in the field of semiconductors, can solve the problems of high cost of testing methods, achieve the effects of reducing testing costs and solving short-circuit or leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

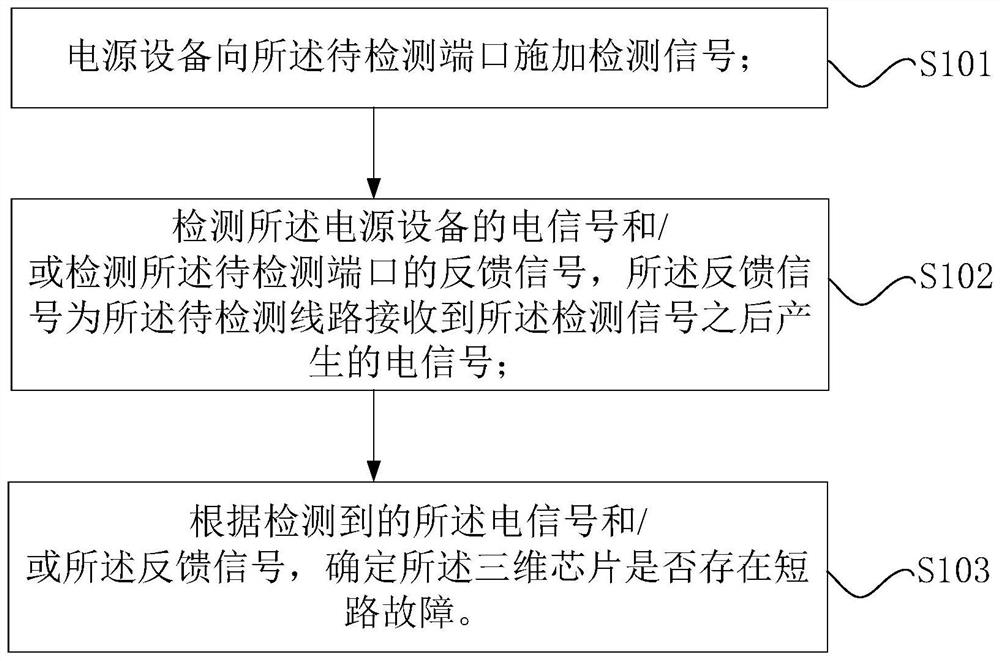

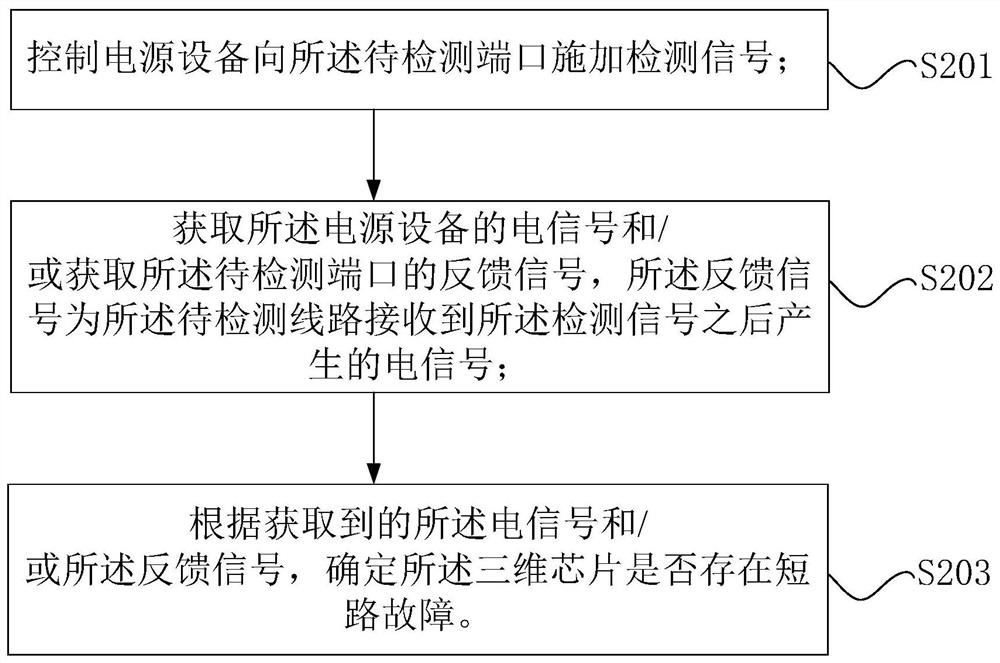

Method used

Image

Examples

Embodiment

[0096] Such as Figure 5 As shown, the three-dimensional chip 101 is placed on the chip mounting platform 103, the power supply device 104 is connected to one end of the power supply chip 112, the power supply chip 112 is connected to the first port 107 to be detected of the three-dimensional chip 101, and the first port 107 to be detected is applied. Small current, detect the first feedback signal between the first port to be detected 107 and the first ground pin 109 (the ground pin of the logic chip 105), if the first feedback signal is 0, then the first port to be detected 107 and There is a short circuit fault between the first ground pin 109; detect the second feedback signal between the first port to be detected 107 and the second ground pin 110 (the ground pin of the memory chip 106), if the second feedback signal is 0 , then there is a short-circuit fault between the first port to be detected 107 and the second ground pin 110 . Then detect the third feedback signal be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More