Power secondary equipment PCIe bus abnormal broken link self-recovery method and system

A secondary equipment, self-recovery technology, applied in data reset devices, electrical digital data processing, instruments, etc., can solve equipment abnormality, system abnormality, increase equipment cost and other problems, reduce the impact of power secondary equipment, avoid system Abnormal, low equipment cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The technical scheme of the present invention will be further described in conjunction with the accompanying drawings and embodiments.

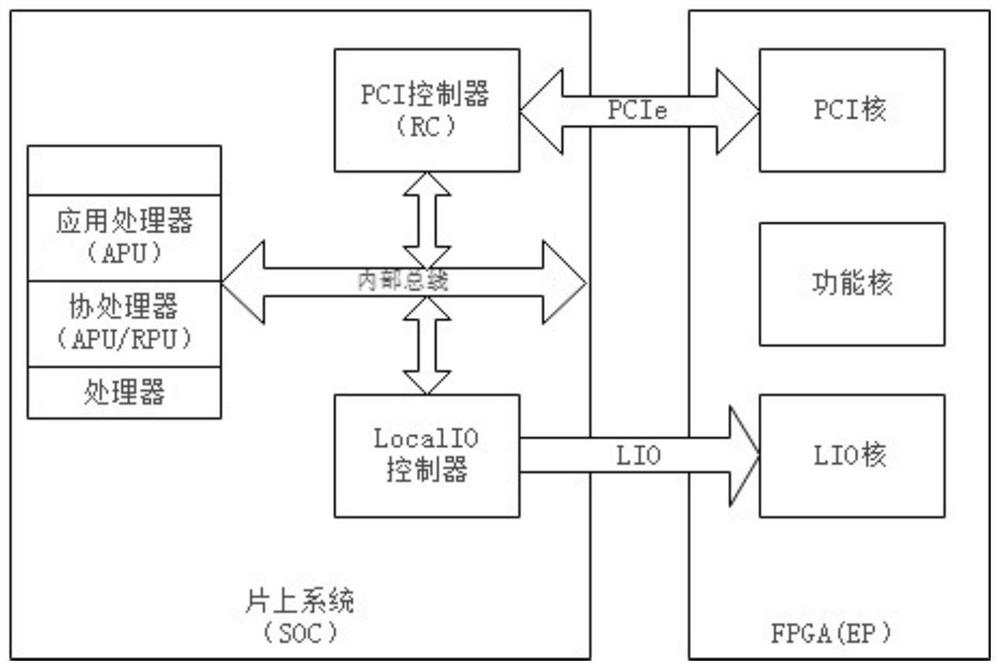

[0036] Such as figure 1 As shown, the system structure of this embodiment includes a PC master system as a first PCIe device and an EP slave system as a second PCIe device; specifically, in this embodiment, the PC master system is a system-on-chip SOC, The EP slave system is a programmable logic device FPGA. Among them, the system-on-chip SOC includes an application processor as a main processor, a coprocessor, a PCI controller RC and a LocalIO controller. The application processor is mainly used for the initialization of the PCI controller RC, the establishment of the PCIe bus link, PCIe bus scanning and address allocation, peripheral resource management and scheduling. The coprocessor may be a processor with the same architecture as the application processor, or a processor with a different architecture, such as a real-time process...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More