Formation method of semiconductor structure

A semiconductor and pattern structure technology, which is applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, and electric solid-state devices, etc., can solve the problems of increasing the difficulty and complexity of integrated circuits, and achieve high lithography process friendliness, small changes and small changes. The effect of key dimensions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] It can be known from the background art that how to improve the matching degree between the pattern formed on the wafer and the target pattern becomes a challenge in the case of shrinking technology nodes.

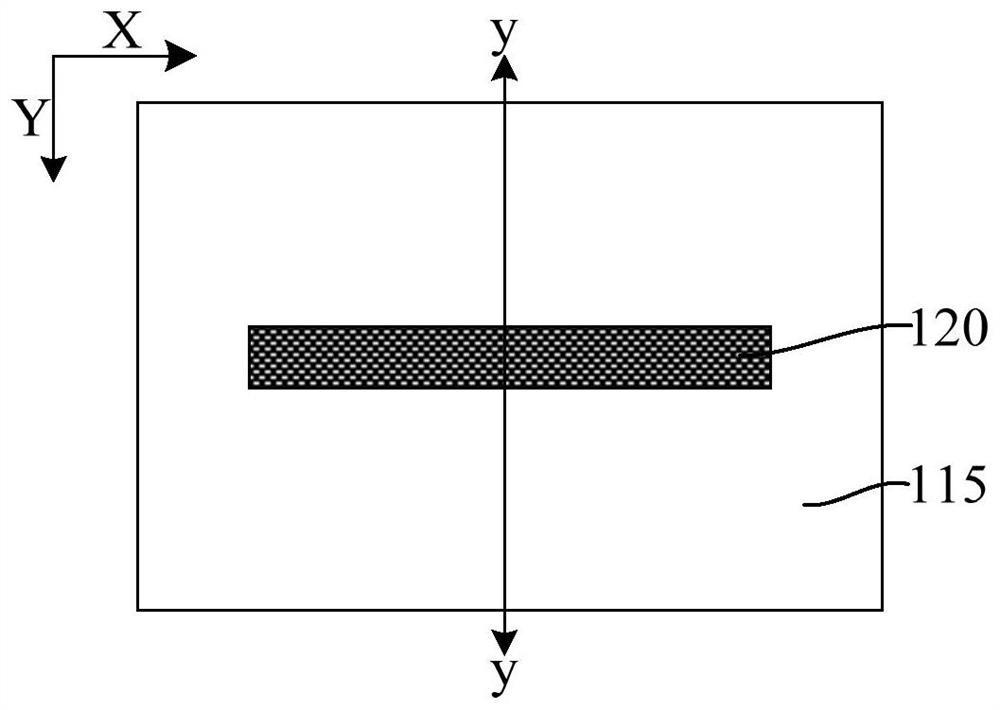

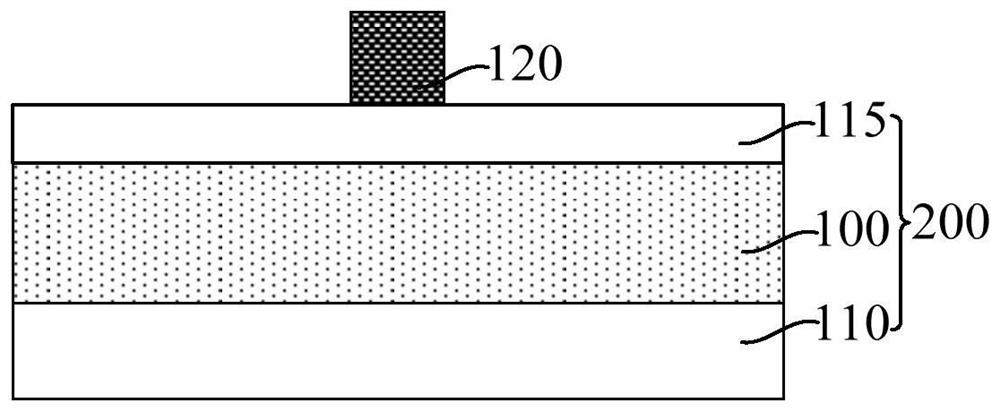

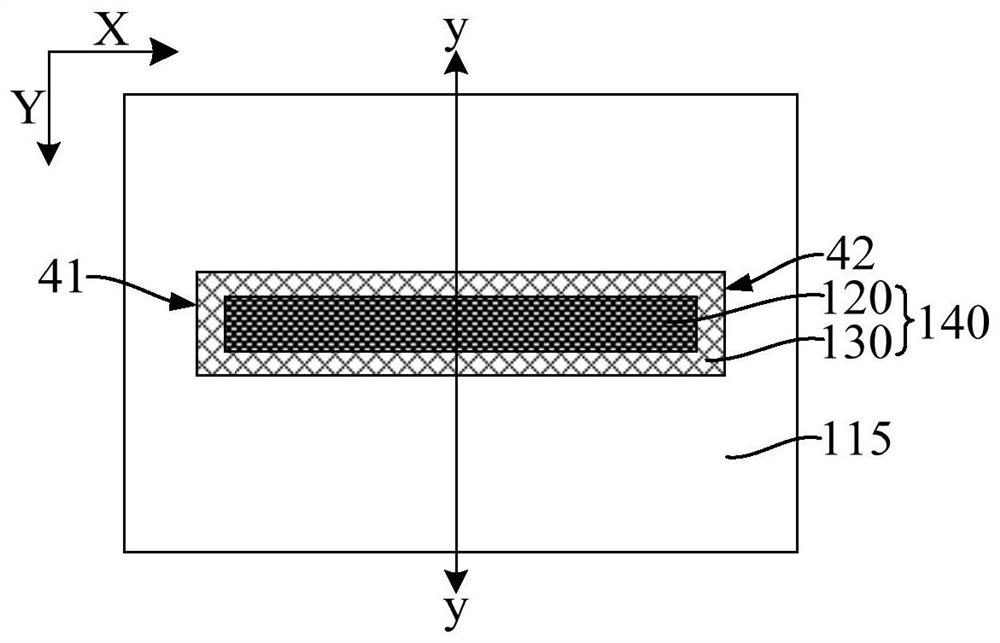

[0022] In order to solve the above technical problem, an embodiment of the present invention provides a method for forming a semiconductor structure, including: providing a substrate including a target layer for forming a target pattern; forming a core layer extending along a first direction on the substrate, The direction perpendicular to the first direction is the second direction; sidewalls are formed on the sidewalls of the core layer, and the core layer and the sidewalls located on the sidewalls of the core layer form a graphic structure layer; A sacrificial layer is formed on the substrate across the pattern structure layer along the second direction, and the sacrifice layer covers at least part of the top and part of the sidewall of the pattern structure layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More