Formation method of semiconductor structure

A technology in the direction of semiconductors and extensions, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., and can solve problems such as the need to improve the performance of semiconductor structures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] From the background technology, it can be seen that the performance of the existing semiconductor structure still needs to be improved.

[0021] Now combined with a semiconductor structure formation method for analysis, the process steps to form a semiconductor structure mainly include:

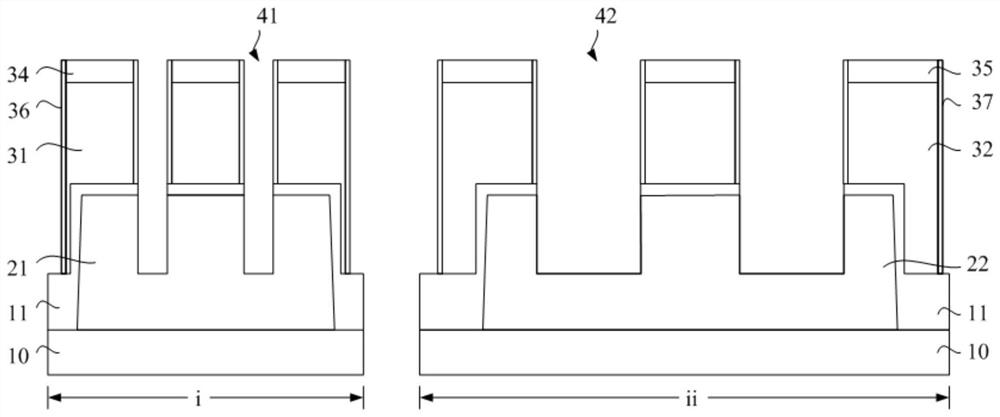

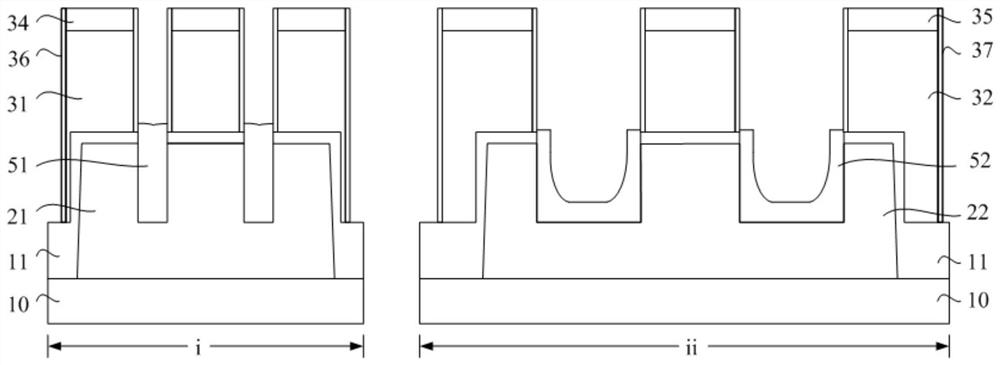

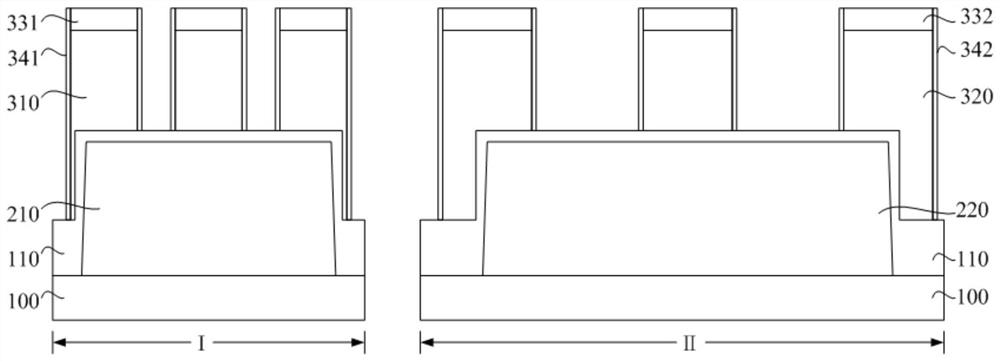

[0022] reference Figure 1, providing a substrate 10, the substrate 10 comprises a first region i and a second region ii, the first region i of the substrate 10 having a discrete first fin 21, the second region ii of the substrate 10 having a discrete second fin 22; the first fin 21 top and side wall, the second fin 22 top and side wall and the substrate 10 form a padding oxide layer 11; forming several discrete arrangements and across the first fin 21 of the first gate 31, The second gate 32 is formed in a plurality of discrete arrangements and across the second fin 22, the spacing adjacent to the first gate 31 is less than the spacing adjacent to the second gate 32; the first gate 31 has ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com