Semiconductor device with elevated source/drain structure and its manufacture method

a semiconductor and source/drain technology, applied in the direction of semiconductor devices, electrical devices, transistors, etc., can solve the problems of inconvenient mass production, slow growth speed of semiconductor films, increased junction leak current, etc., to prevent aggregation of metal silicides, reduce lateral diffusion of impurities, and increase growth speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

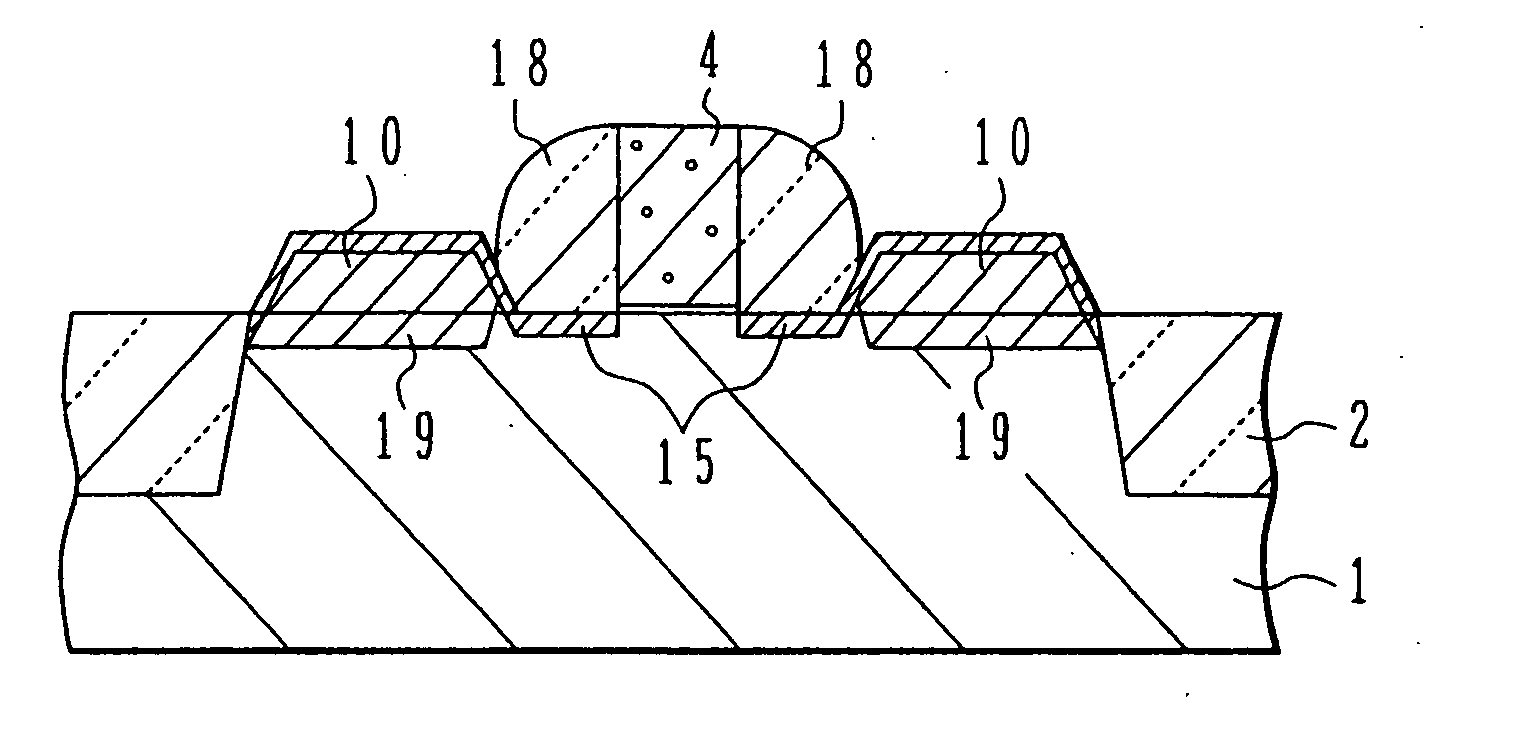

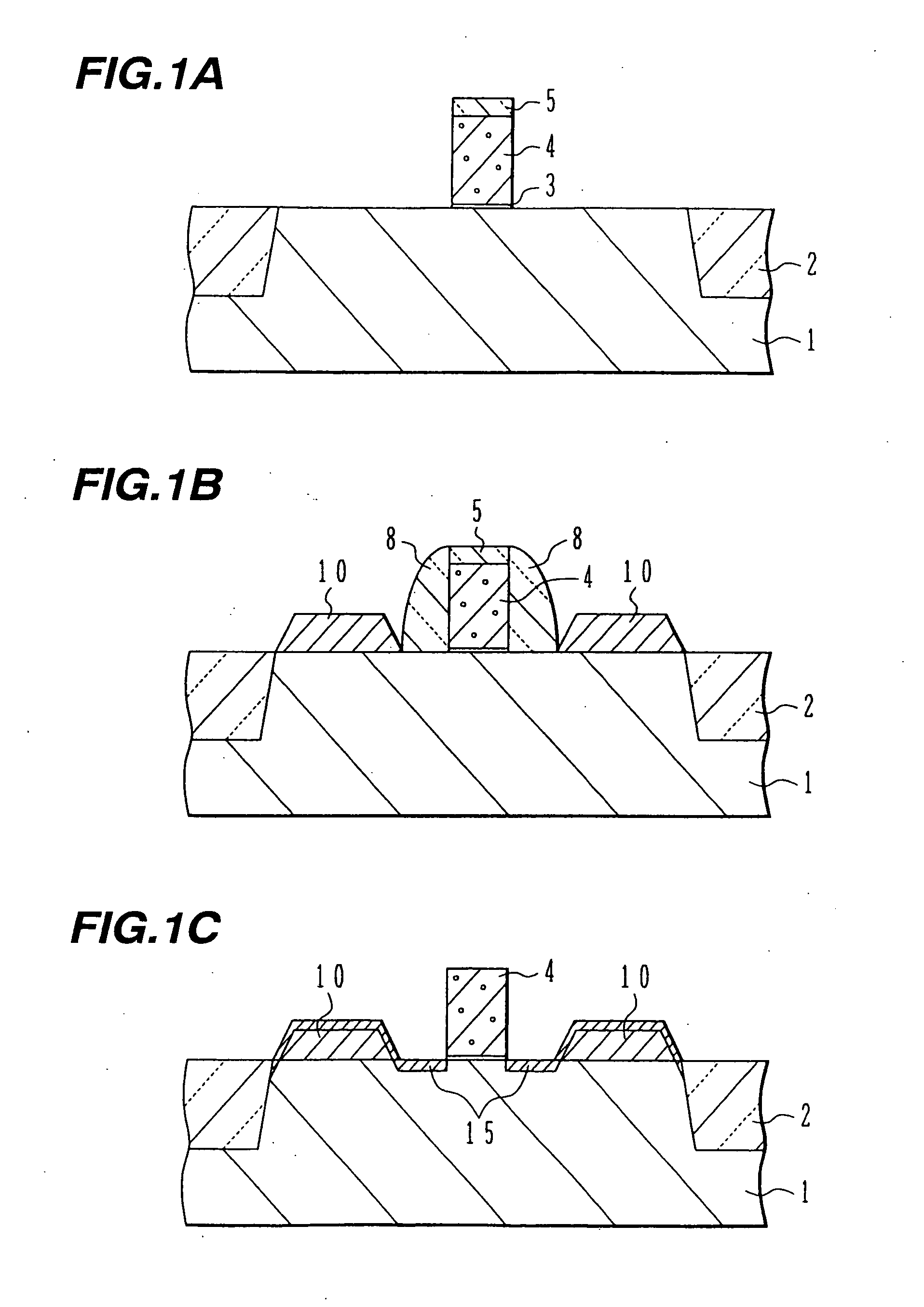

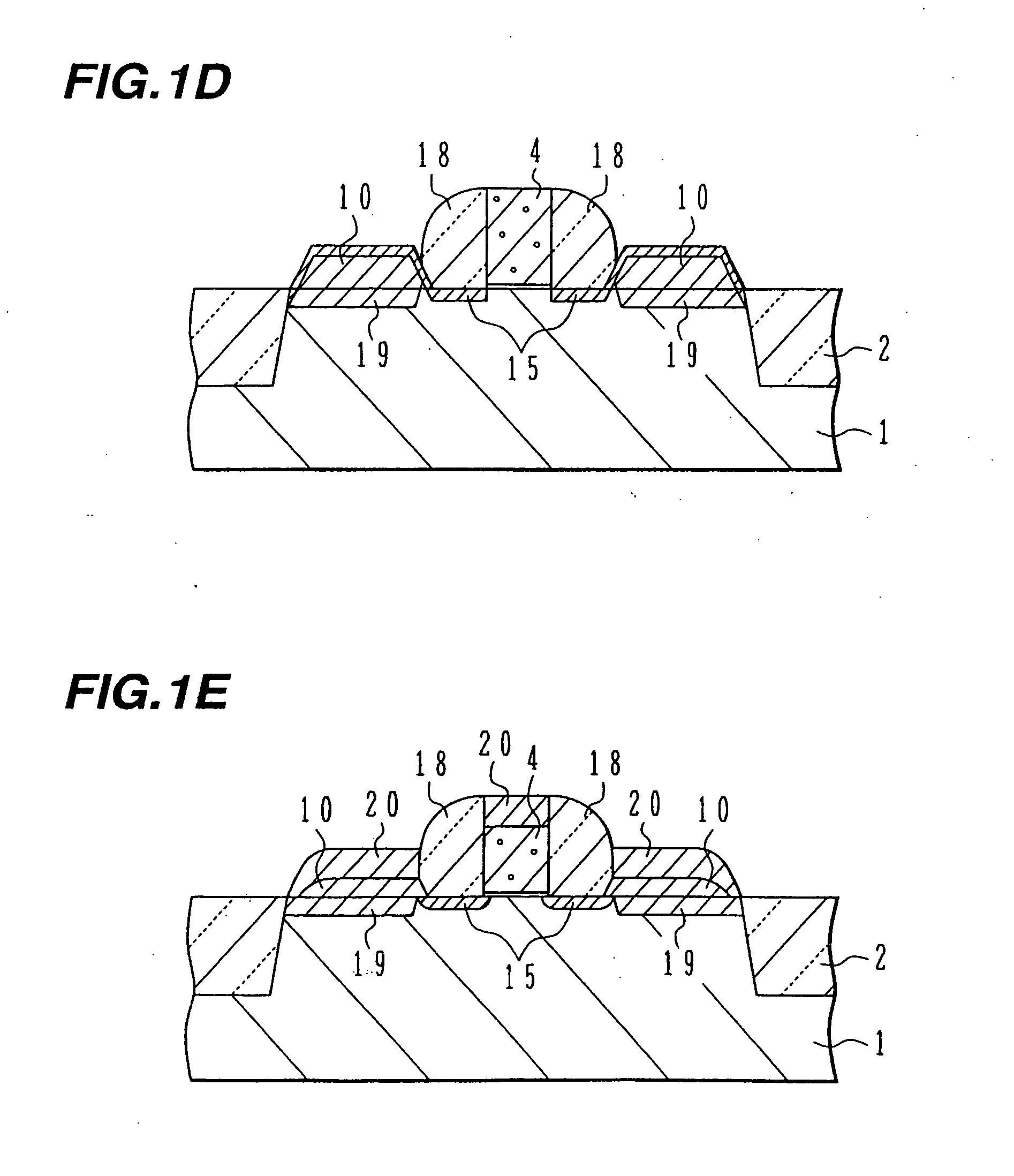

[0021] With reference to FIGS. 1A to 1E, a semiconductor device manufacture method according to an embodiment of the invention will be described.

[0022] As shown in FIG. 1A, in the surface layer of a semiconductor substrate 1 made of silicon, an element separation insulating film 2 is formed by local oxidation of silicon (LOCOS) or shallow trench isolation (STI). The element separation region 2 defines active regions. The surface of the semiconductor substrate 1 is thermally oxidized to form a silicon oxide film on the surface of each active region, the silicon oxide film having a thickness of about 2 nm and being used as a gate insulating film.

[0023] On the semiconductor substrate 1, a polysilicon film having a thickness of 70 to 120 nm is formed by chemical vapor deposition (CVD). Instead of the polysilicon film, an amorphous silicon film may be formed. A silicon nitride film having a thickness of 20 to 40 nm is formed on the polysilicon film by CVD. By covering the region where ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More