Dynamic configurable high-performance queue scheduling method, system, processor and protocol

A queue scheduling, high-performance technology, applied in transmission systems, electrical components, etc., can solve the problems of limited application scenarios, limited number of scheduling queues, poor scalability and universality, etc., to achieve strong scalability and universality, The effect of saving storage resources and good compatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0059] In order to make the objectives, technical solutions and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the embodiments. It should be understood that the specific embodiments described herein are only used to explain the present invention, but not to limit the present invention.

[0060] 1. Explain the embodiment. In order for those skilled in the art to fully understand how the present invention is specifically implemented, this part is an explanatory embodiment to expand the description of the technical solutions of the claims.

[0061] Dynamically configurable high-performance queue scheduling method, system, processor and protocol

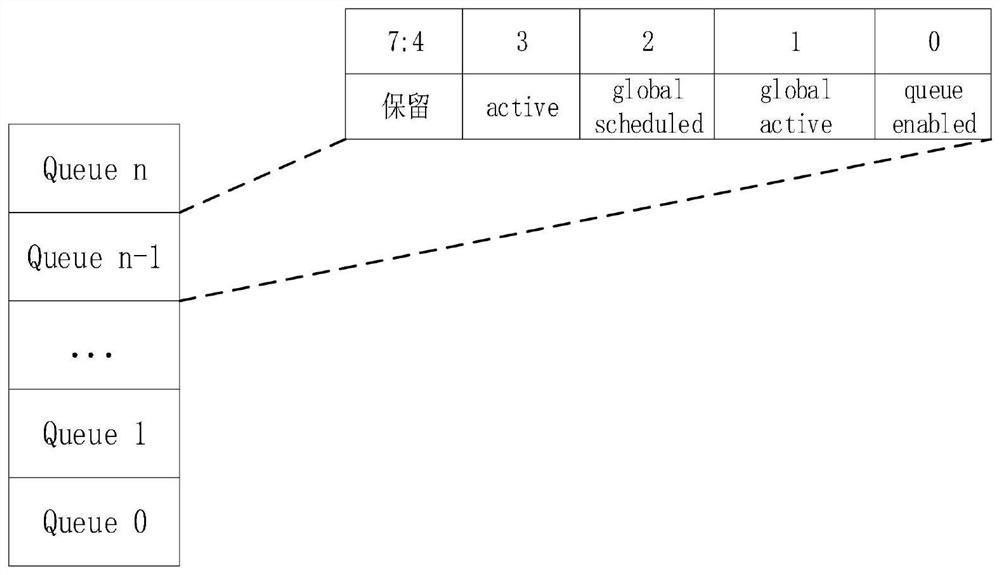

[0062] like figure 1 As shown, the queue status information provided by the embodiment of the present invention includes:

[0063] queue enabled bit: The user can disable or enable the queue at will through this bit. Only when the bit is written to 1 by th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More