Process for preparing low storage junctions of DRAM

A technology of thin film layer and photoresist layer, which is applied to the original parts, instruments, and optomechanical equipment used for photomechanical processing, and can solve the problems affecting the electrical performance of integrated circuits and reducing the power of the storage junction 30 under the capacitor, etc. Achieve the effects of improving optical proximity effect, solving circular deformation and shrinkage, and increasing power storage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

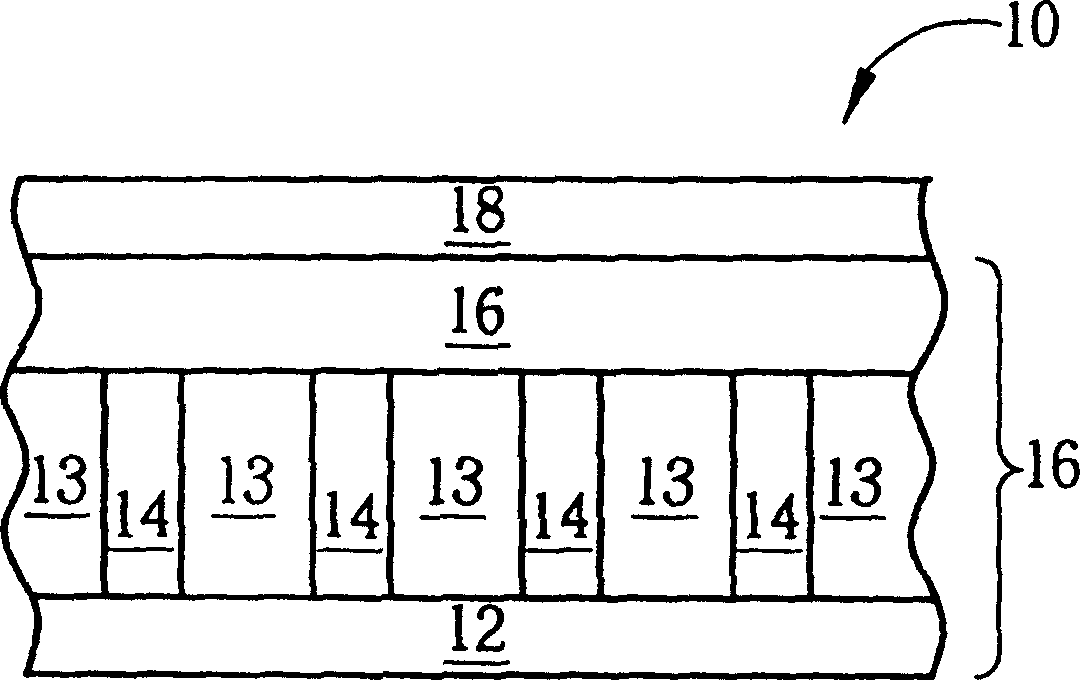

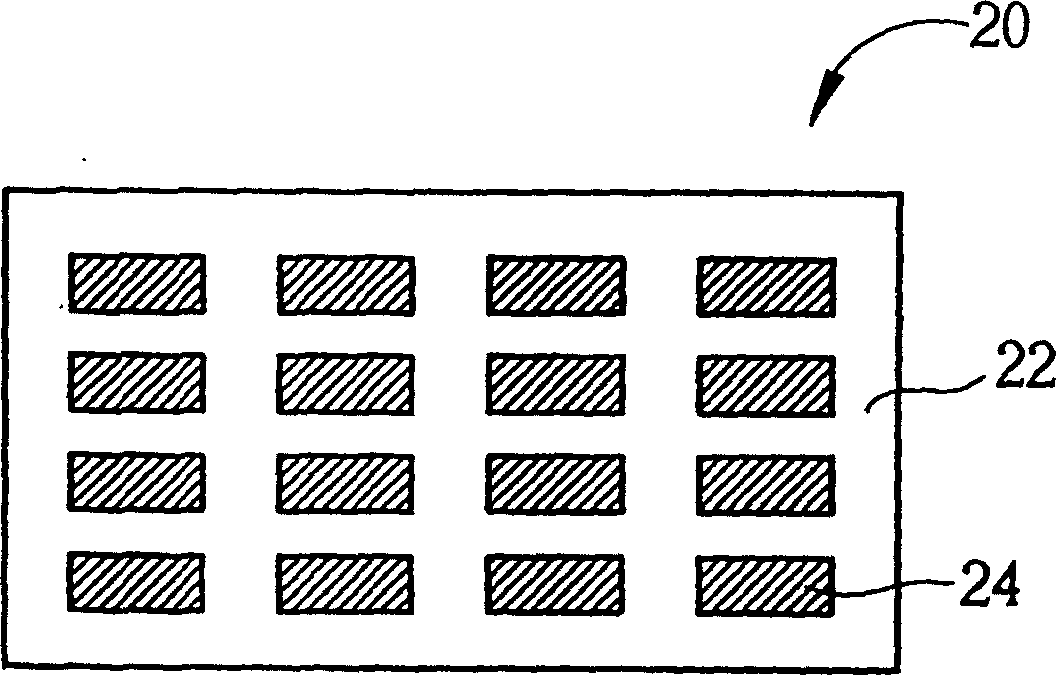

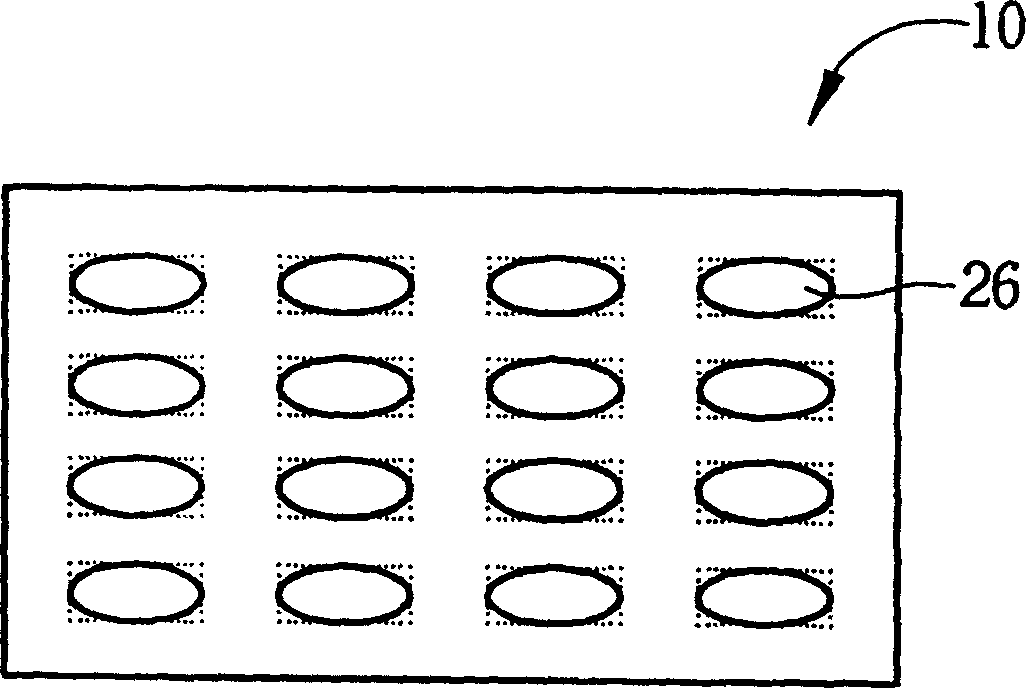

[0055] refer to Figure 10 to Figure 14 , Figure 10 to Figure 14 It is a schematic diagram of the photolithography process according to the present invention. The photolithography process is used to pattern the size and location of the capacitive lower storage junctions of the DRAM on a semiconductor wafer 60 . Such as Figure 10 As shown, the semiconductor wafer 60 includes a silicon substrate 62, an insulating layer 63 made of a silicon oxide compound is arranged on the surface of the silicon substrate 62, and a plurality of contact junctions 64 made of doped polysilicon are arranged in the insulating layer 63, A polysilicon or amorphous silicon layer 65 for forming the underlying storage junction is disposed on the surface of the insulating layer 63 and covers the contact junctions 64 , and a photoresist layer 67 is disposed on the surface of the semiconductor wafer 60 . Wherein, the contact junction 64 is used to electrically connect a drain (not shown) of a MOS transi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More