Silicon insulator structure simicoductor device

A semiconductor and device technology, applied in the field of SOI structure semiconductor devices, can solve the problems of reduced efficiency, narrow process margin, and complicated manufacturing process.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

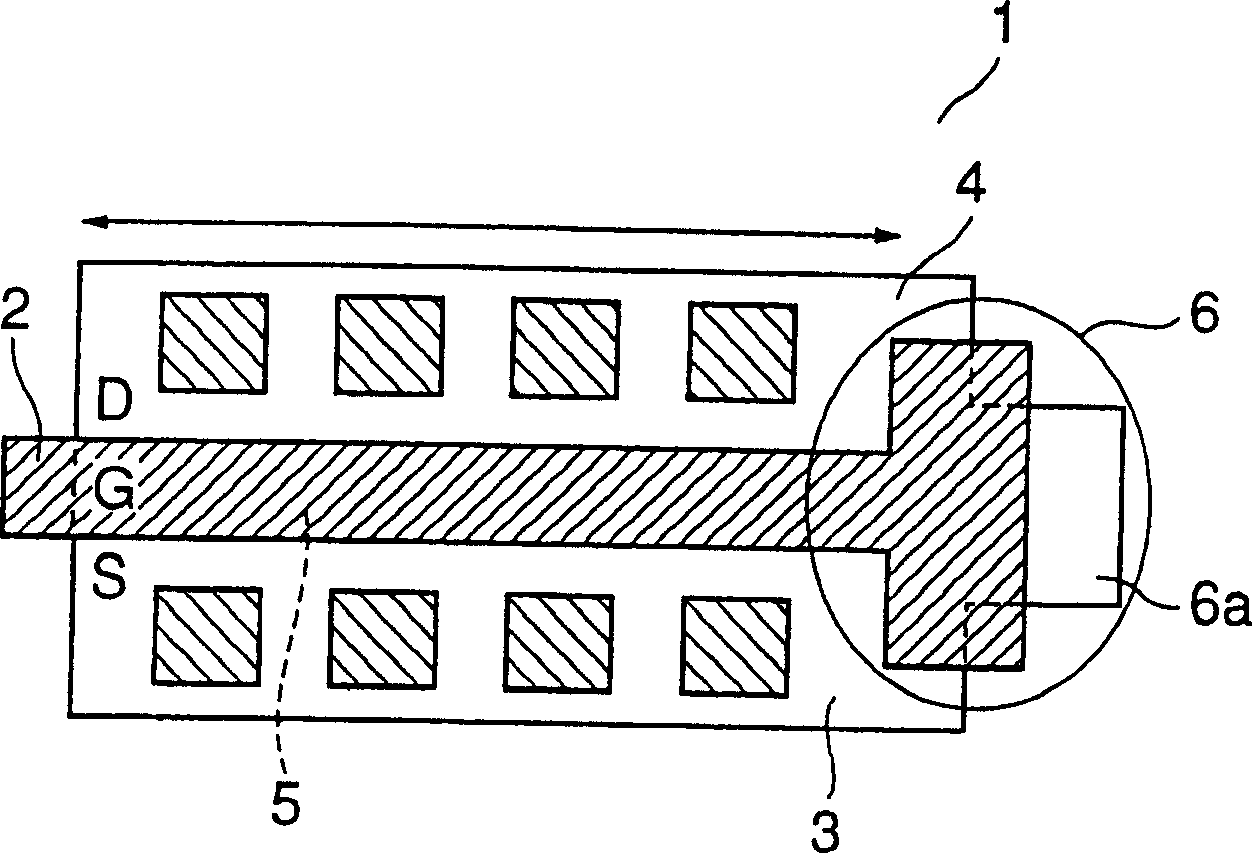

[0053] As shown in Figure 1(a), the SOI MOSFET in this embodiment is fabricated on an SOI substrate. The SOI substrate is a buried oxide film with a thickness of about 120nm and a surface silicon layer with a thickness of about 50nm. The way it is constructed on the substrate. The LOCOS film 1 is formed on the surface silicon layer of the SOI substrate to define the active area. The gate 2 doped with N-type impurities is formed on the active region by a gate oxide film with a thickness of about 7 nm, and the gate length L=0.35 μm. In addition, the N-type source region 3 and the drain region 4 are formed in those surface silicon layer portions on both sides of the gate 2. By the way, the surface silicon layer is in a floating state.

[0054] The channel region 5 is formed directly below the gate 2, and the potential well 6 is formed directly below the channel region 5 in the gate width direction (the direction indicated by the arrow in FIG. 1(a)), and surrounds the channel region 5...

Embodiment 2

[0069] Such as Figure 4 As shown, except that the potential wells 6 are formed on both sides of the channel region 5, the SOI MOSFET in this embodiment is basically the same as the SOI MSOFET in the first embodiment.

[0070] Therefore, the holes generated near the drain junction will migrate to the two potential wells 6.

Embodiment 3

[0072] Such as Figure 5 As shown, except that the potential well 16 is formed directly below both ends of the channel region 5 in the direction of its gate width, and does not include any protruding active regions or any regions with higher impurity concentration, the SOIMOSFET of this embodiment is compatible with The SOI MOSFET of Embodiment 1 is basically the same.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More