A read-only memory and read-only memory devices

A read-only memory, memory technology, applied in the direction of read-only memory, static memory, digital memory information, etc., can solve problems such as high complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

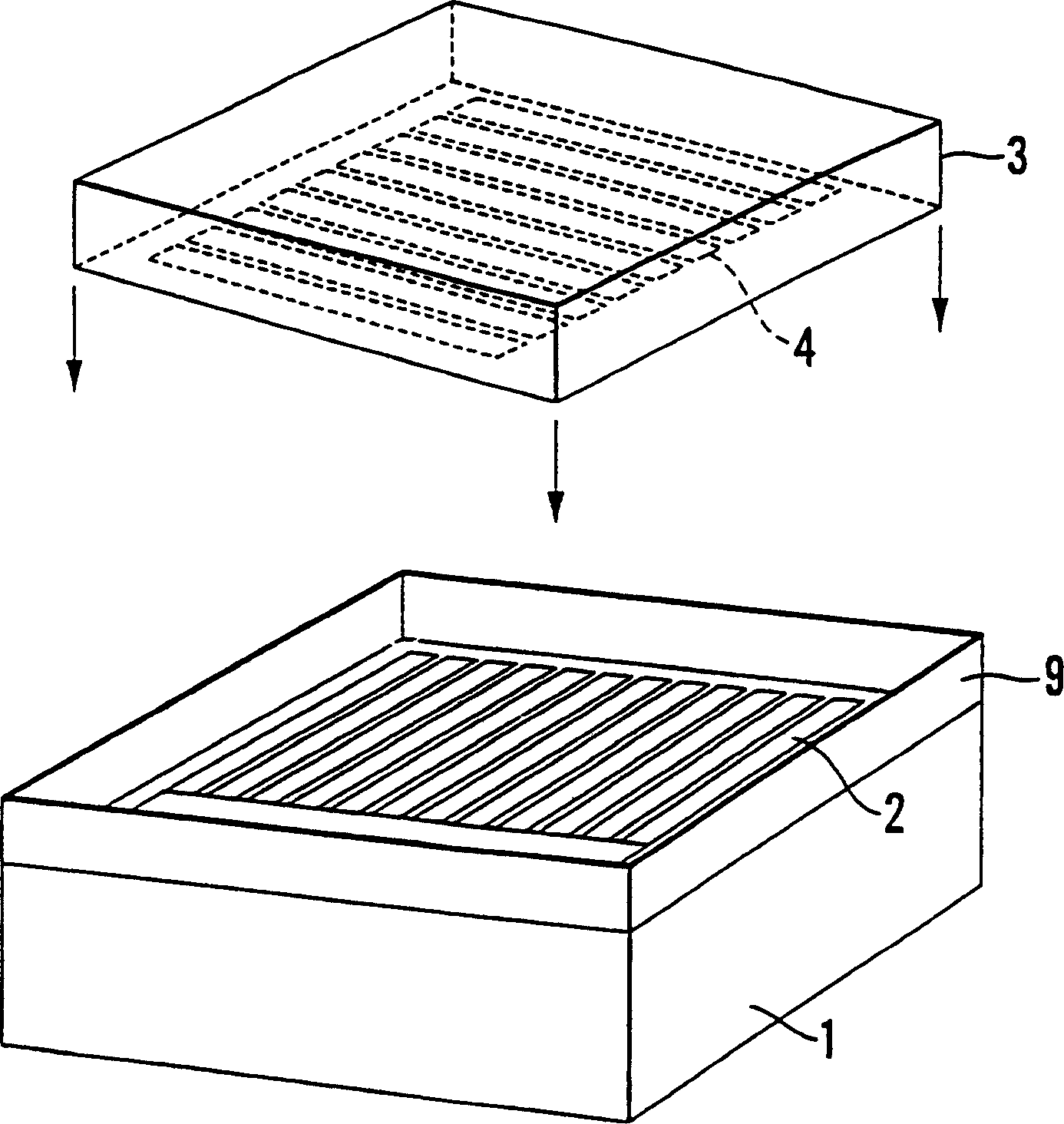

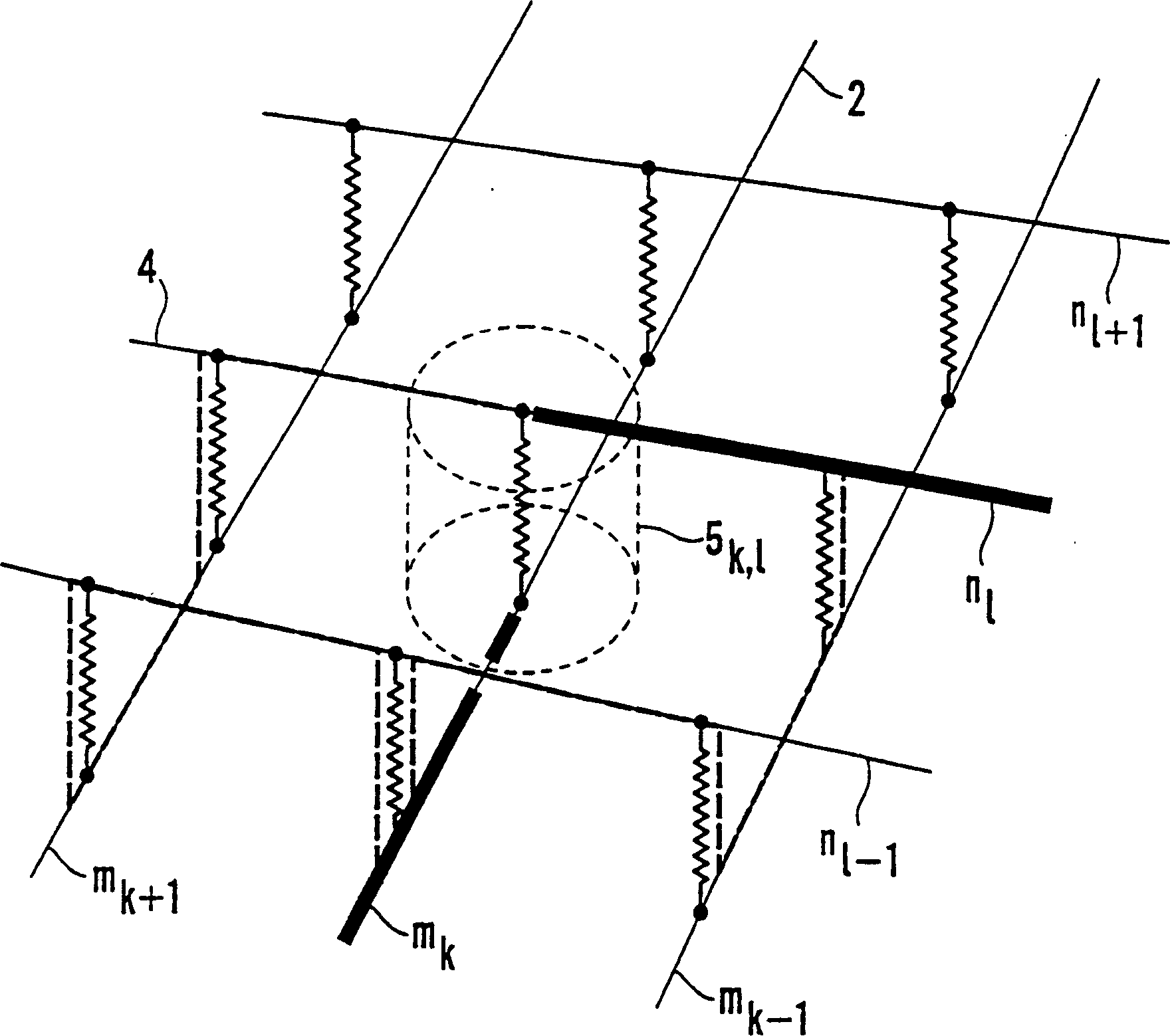

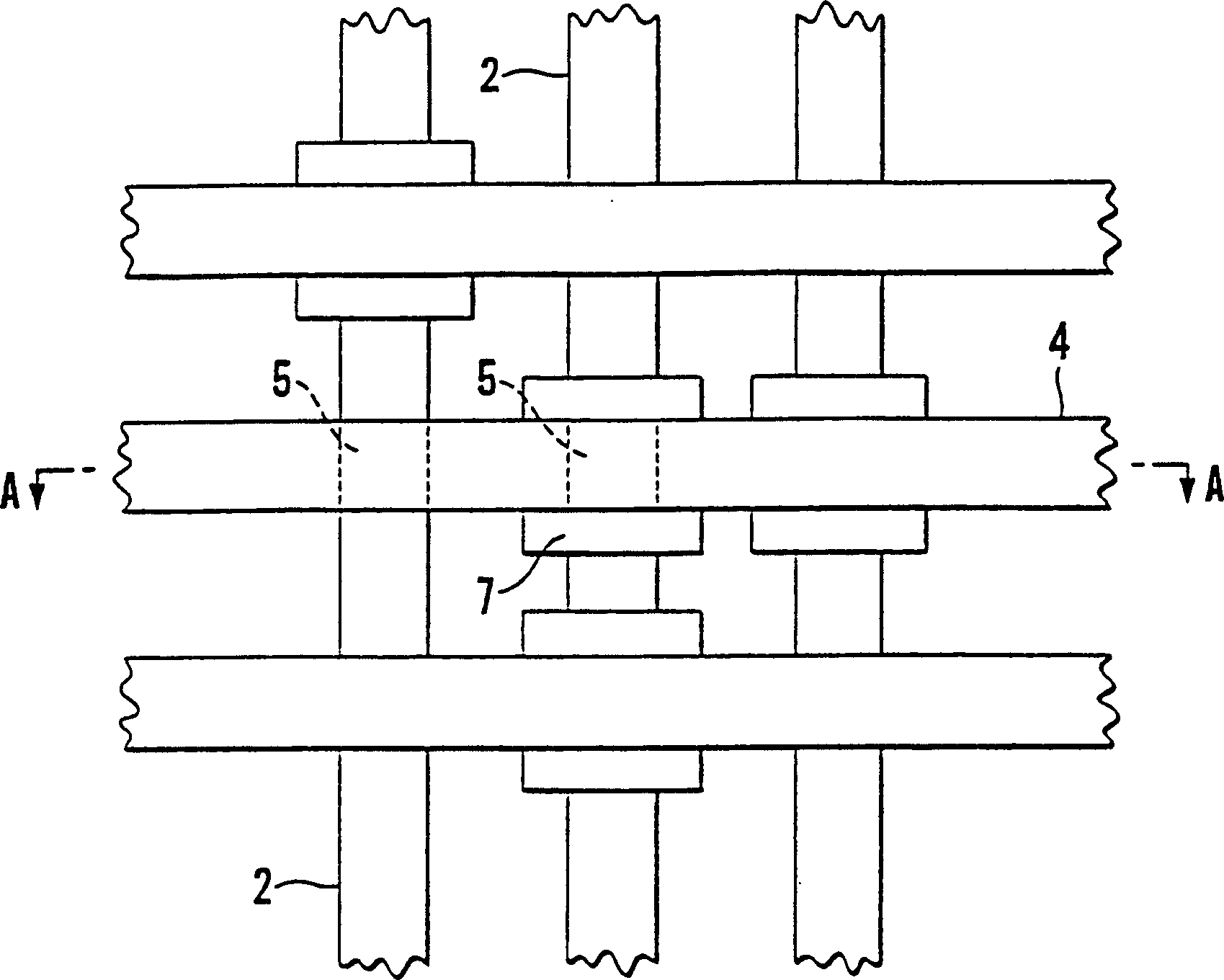

[0036] The general background of the invention is discussed in more detail below. figure 1 A general matrix addressing system is shown in , in which, for example, m wires 2 are spaced from each other and extend in the x direction, for example, n overlapping wires 4 extend in the y direction, respectively forming the first orthogonal x, y electrode matrix and a second electrode structure. The x-electrodes 2 and y-electrodes 4 are arranged relatively close to each other, thereby providing a geometrically well-defined area of overlap or intersection between the two electrodes. The space around and between each intersection is roughly defined by the overlap given by the width of the intersecting x- and y-electrodes at these intersections, including those which will be denoted below as memory cells 5, see figure 2 . In the memory cell 5, the mutually overlapping area of the respective x and y electrodes 2, 4 is indicated as the contact area of the memory cell. According t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com