Method for encapsulation in chip level by use of electroplating mask of elastic body

A technology of chip-level packaging and elastomers, which is applied to circuits, electrical components, and electrical solid devices, and can solve problems such as the complexity of the manufacturing process and the waste of photoresist materials

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

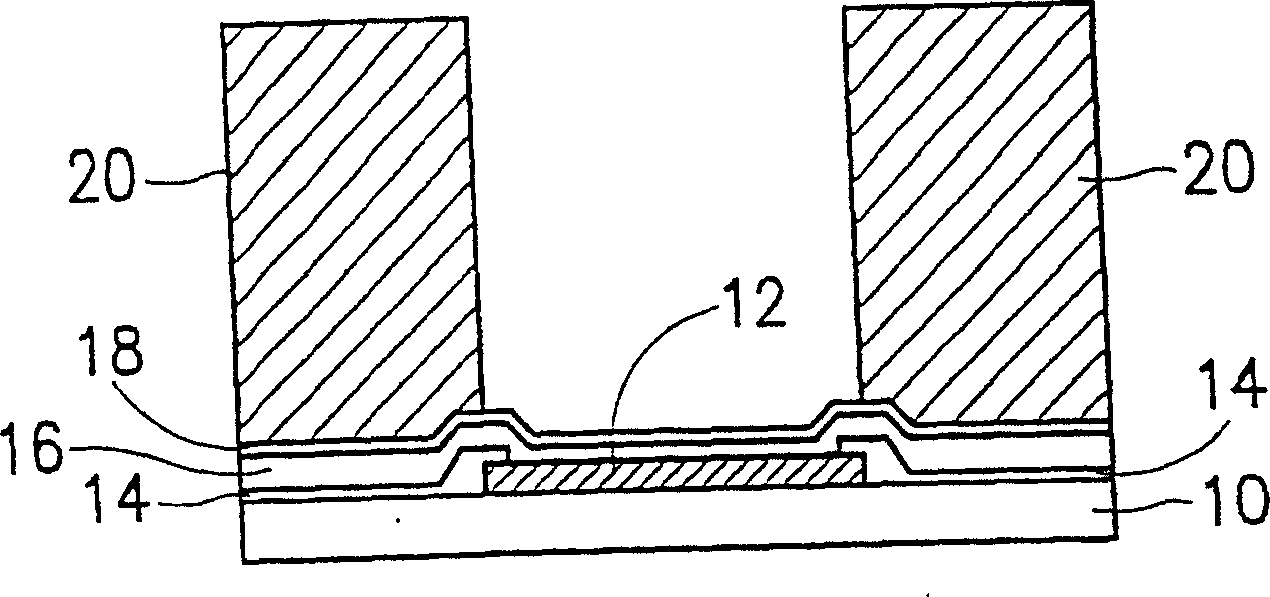

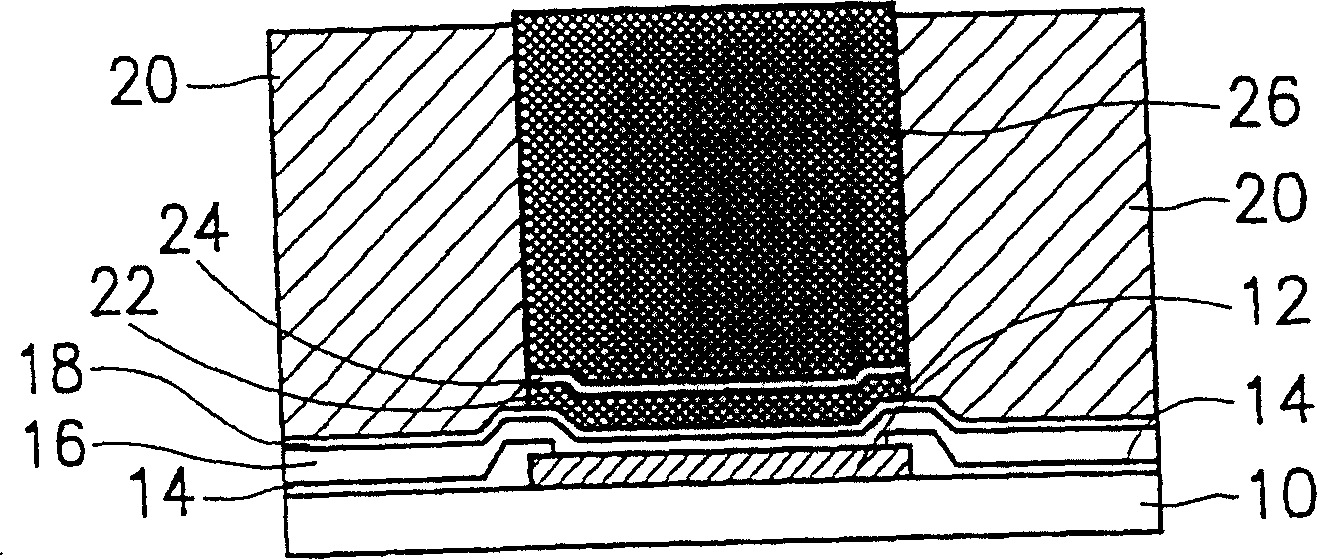

[0018] In order to simplify the packaging manufacturing process, avoid waste of photoresist material, and make the chip assembled on the circuit board, it can still be disassembled and redone, so the electroplating manufacturing process is combined with the packaging manufacturing process. The following will match Figure 2A to Figure 2E , a method of using an elastomer plating mask as a chip-scale package of the present invention in detail.

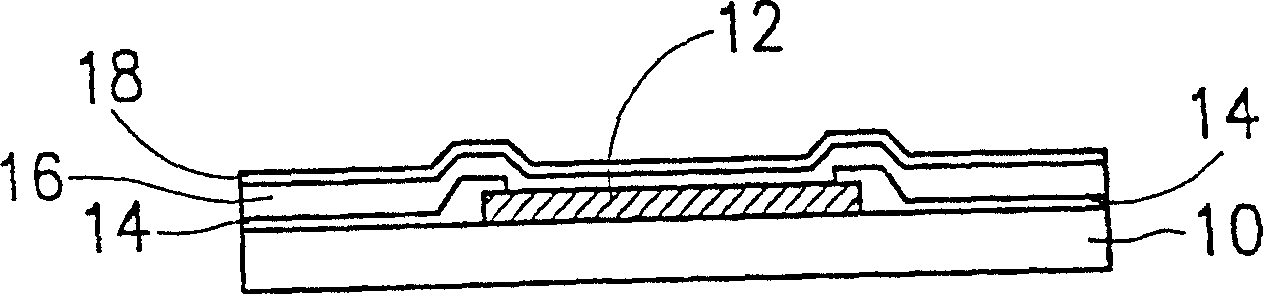

[0019] First please refer to Figure 2A , on the wafer 100 on which the solder pads 102 have been formed, first cover a protective layer 104, such as a polyimide (polyimide) protective layer, the protective layer 104 roughly exposes the area of the solder pads 102, and then coat the protective layer 104 , forming an under-bump metal layer 106 on the wafer 100 and the bonding pad 102 under the solder bump to be formed, which is used to prevent the diffusion of other metal materials subsequently formed above it.

[0020] Please refer t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com