Method for preparing semiconductor device with super shallow and super steep backward surface groove

A surface channel, semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., can solve problems such as low productivity of doping curves and difficulty in extracting ultra-low energy ion beams

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] Other objects and aspects of the present invention will be apparent from the following description of the embodiments with reference to the accompanying drawings.

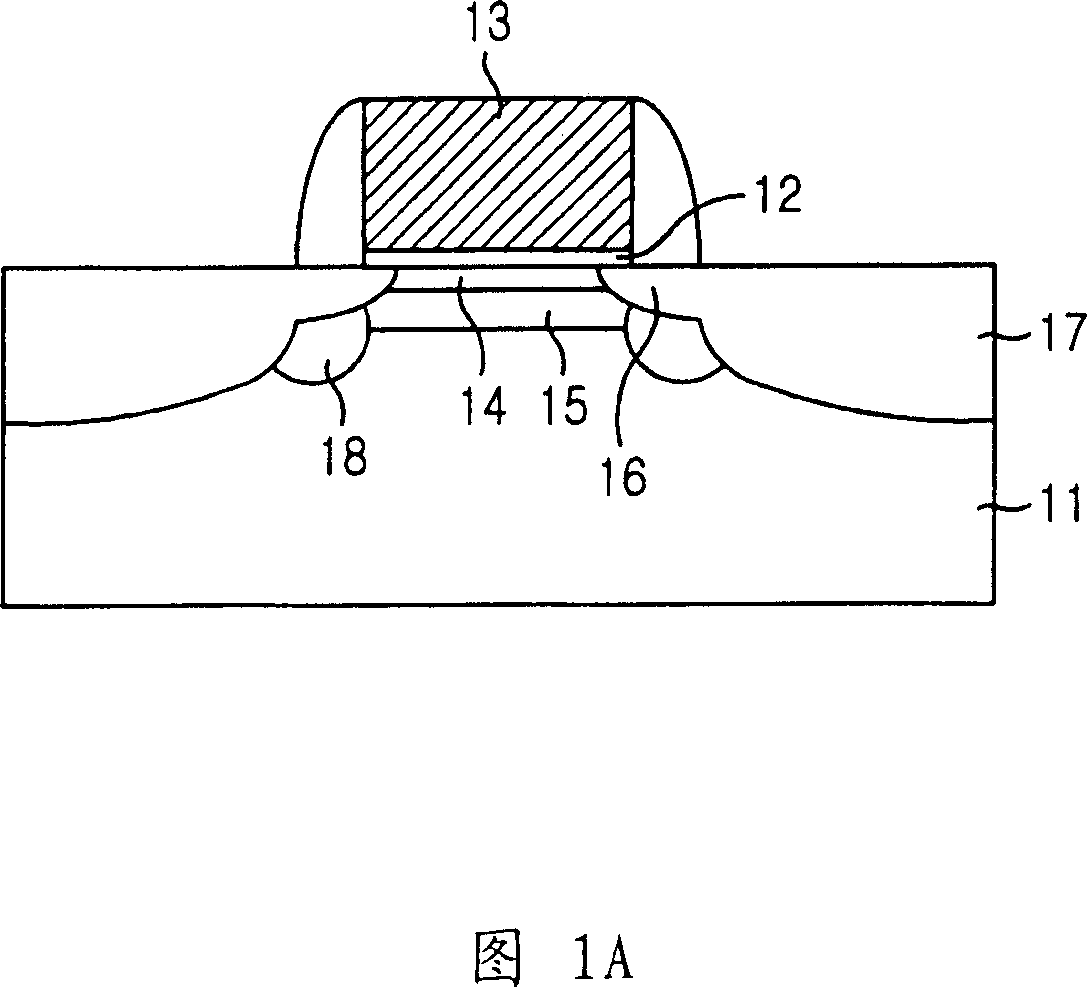

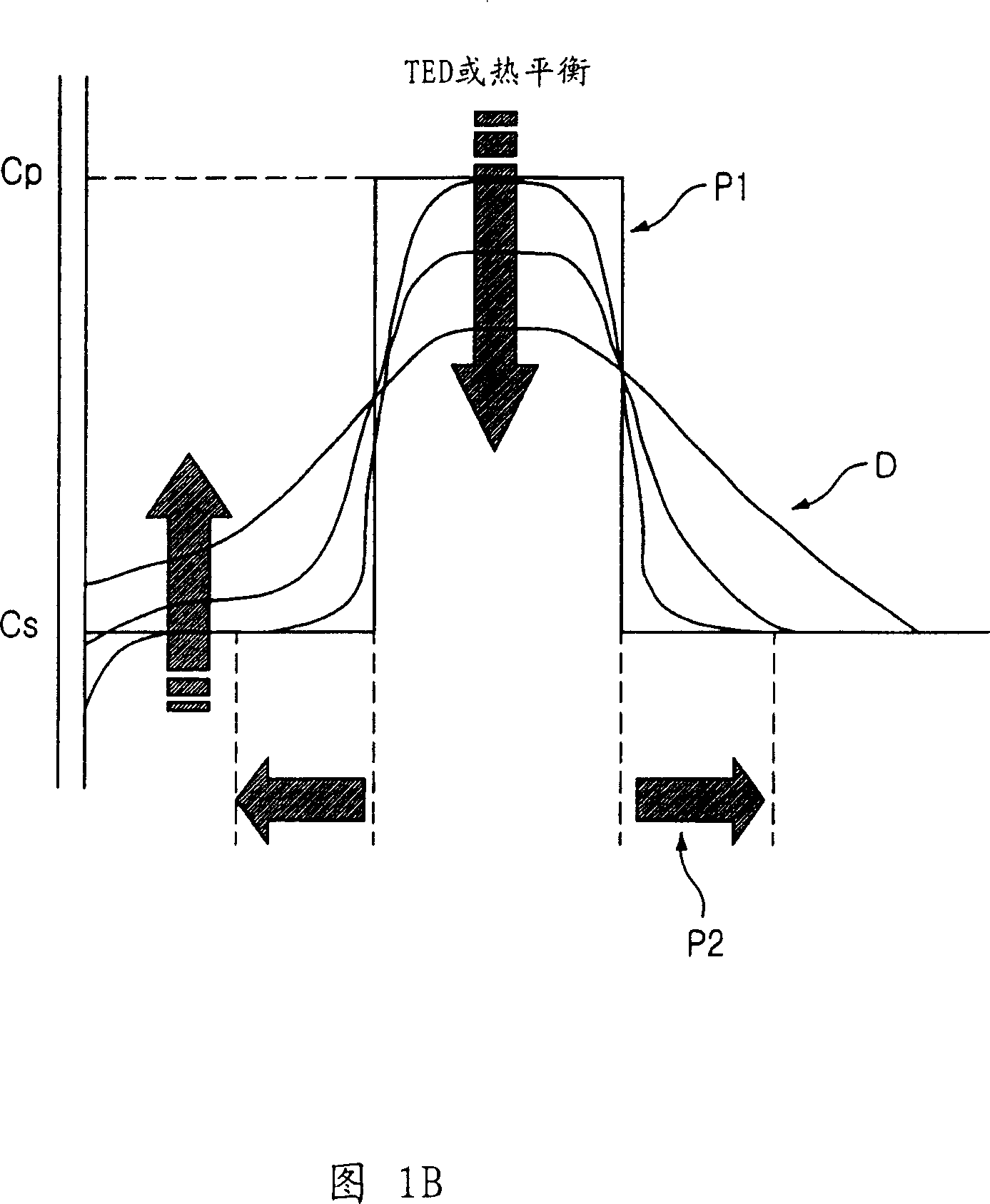

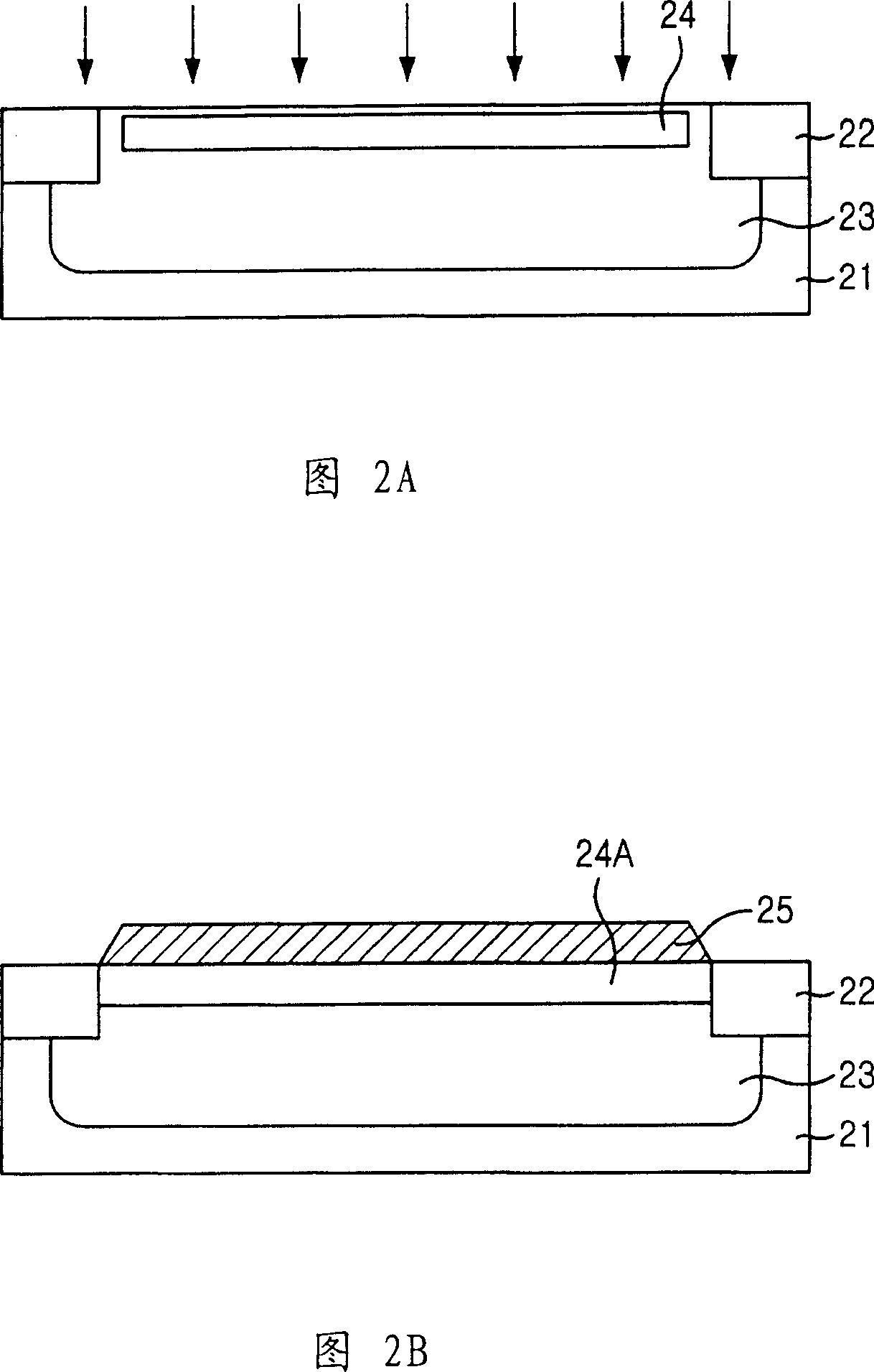

[0044] The present invention provides a method for manufacturing a semiconductor device with an ultra-shallow ultra-steep reverse (hereinafter referred to as SSR) surface channel. Compared with low-energy ion implantation technology, decaborane ion implantation technology reduces the distribution width of dopants and greatly improves productivity due to shortened process time. Therefore, this method is particularly suitable for epi-channel doping to provide ultra-shallow SSR epi-channels with improved performance and increased productivity.

[0045] Molecular formula is B 10 h 14 Decaborane is a particularly suitable source ion for implantation in the present invention. Decaborane also has a large molecular weight, capable of providing boron ions comprising 10 boron atoms when ionized. Because of these c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More