Method for manufacturing semiconductor integrated circuit device

A technology of integrated circuits and manufacturing methods, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, circuits, etc., can solve problems such as the inability to obtain withstand voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] Hereinafter, embodiments of the semiconductor integrated circuit device and its manufacturing method according to the present invention will be described in detail with reference to the drawings.

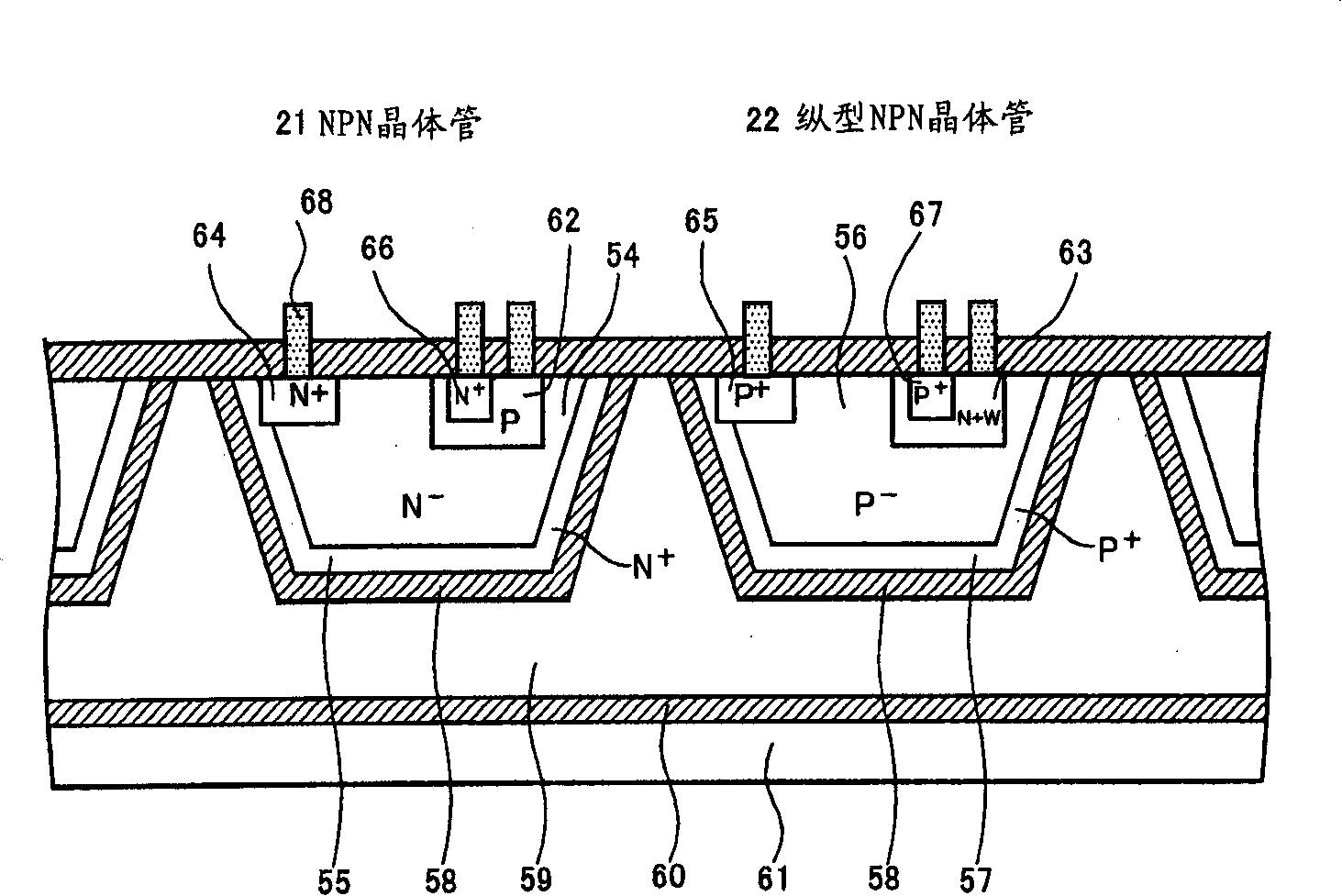

[0044] figure 1 It is a cross-sectional view of an IC of a high withstand voltage NPN transistor 21 and a high withstand voltage vertical PNP transistor 22 formed by using polysilicon 59 as dielectric isolation type complementary transistors.

[0045] In the semiconductor integrated circuit device of the present invention, polysilicon 59 is formed on support substrate 61 covered with silicon oxide film 60 . Here, the support substrate 61 and the polysilicon 59 are bonded together by performing heat treatment at 1100° C. to 1200° C. for about 2 hours through the silicon oxide film 60 . Then, a dielectric isolation type complementary type bipolar transistor is formed via the polysilicon 59 .

[0046] In the high withstand voltage NPN transistor 21, a silicon oxide film 58 an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More