Defect reduction with rotated double aspect ratio trapping

An aspect ratio and high aspect ratio technology, applied in the field of semiconductor devices, can solve problems such as affecting the quality of the crystal structure of epitaxial growth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

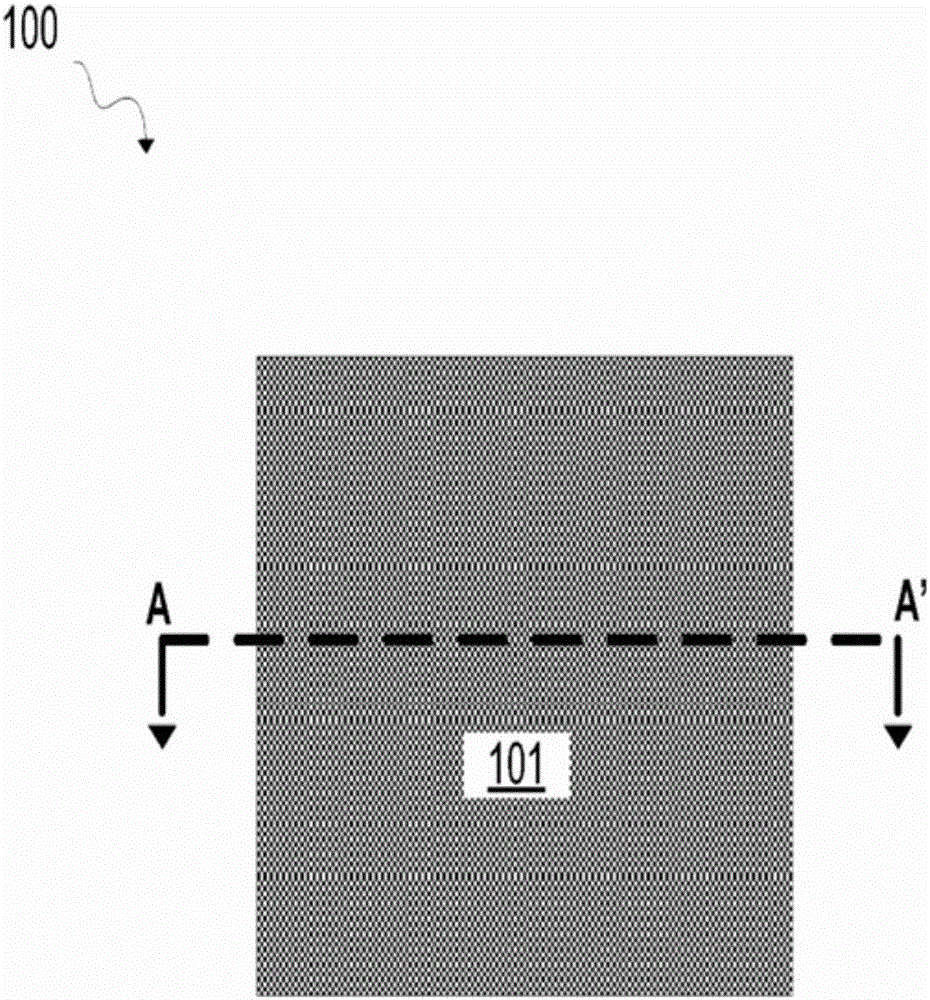

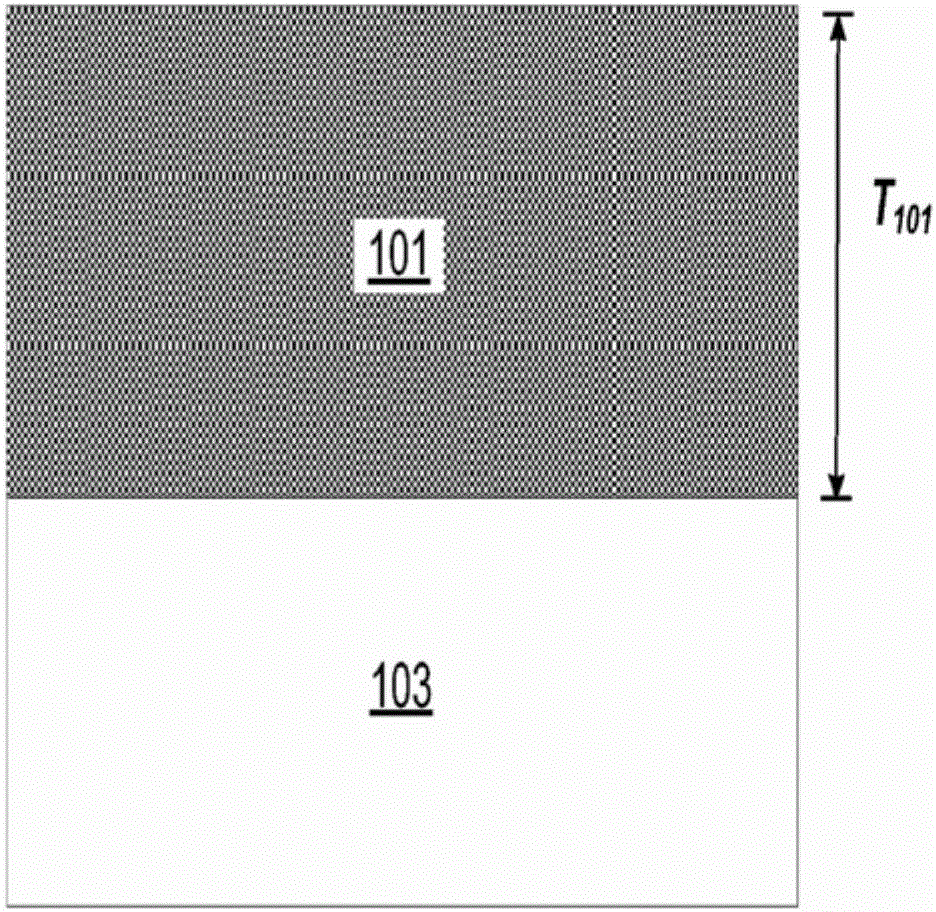

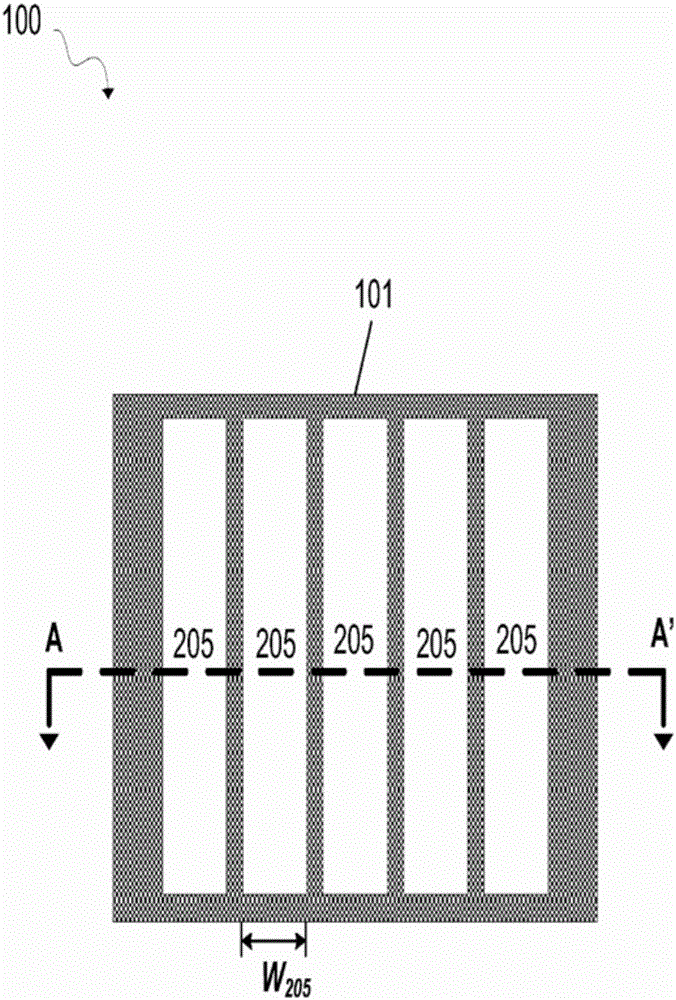

[0016] Disclosed herein are detailed embodiments of the claimed structures and methods; however, it is to be understood that the claimed structures and methods may be embodied in various forms and the disclosed embodiments are illustrative only . This invention may, however, be embodied in many different forms and should not be construed as limited to the specific embodiments illustrated herein. Rather, these illustrative embodiments are provided so that this disclosure will be thorough and complete, and will convey the scope of the invention to those skilled in the art.

[0017] In the following description, numerous specific details are provided, such as particular structures, components, materials, dimensions, processing steps and techniques, in order to provide a thorough understanding of the present invention. It will be understood, however, by one of ordinary skill in the art that the present invention may be practiced without these specific details. In other instances...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More