Semiconductor memory device and memory modulus and system adopting same

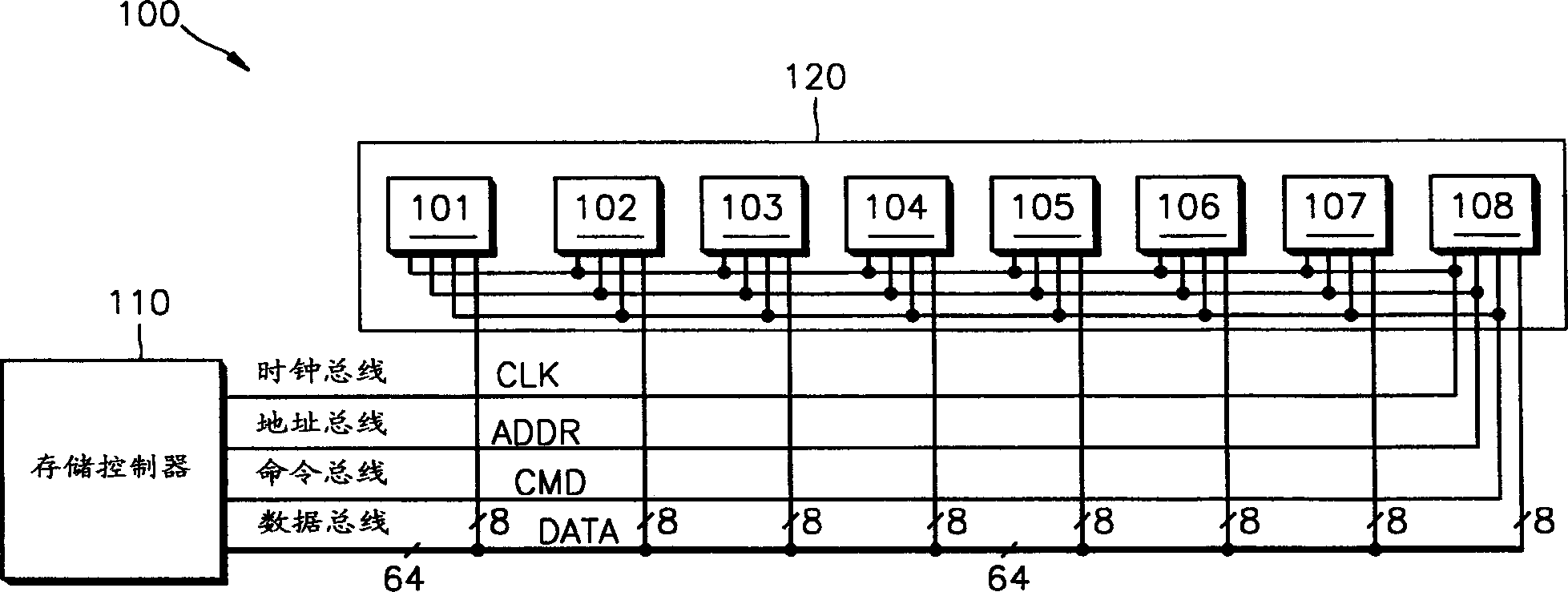

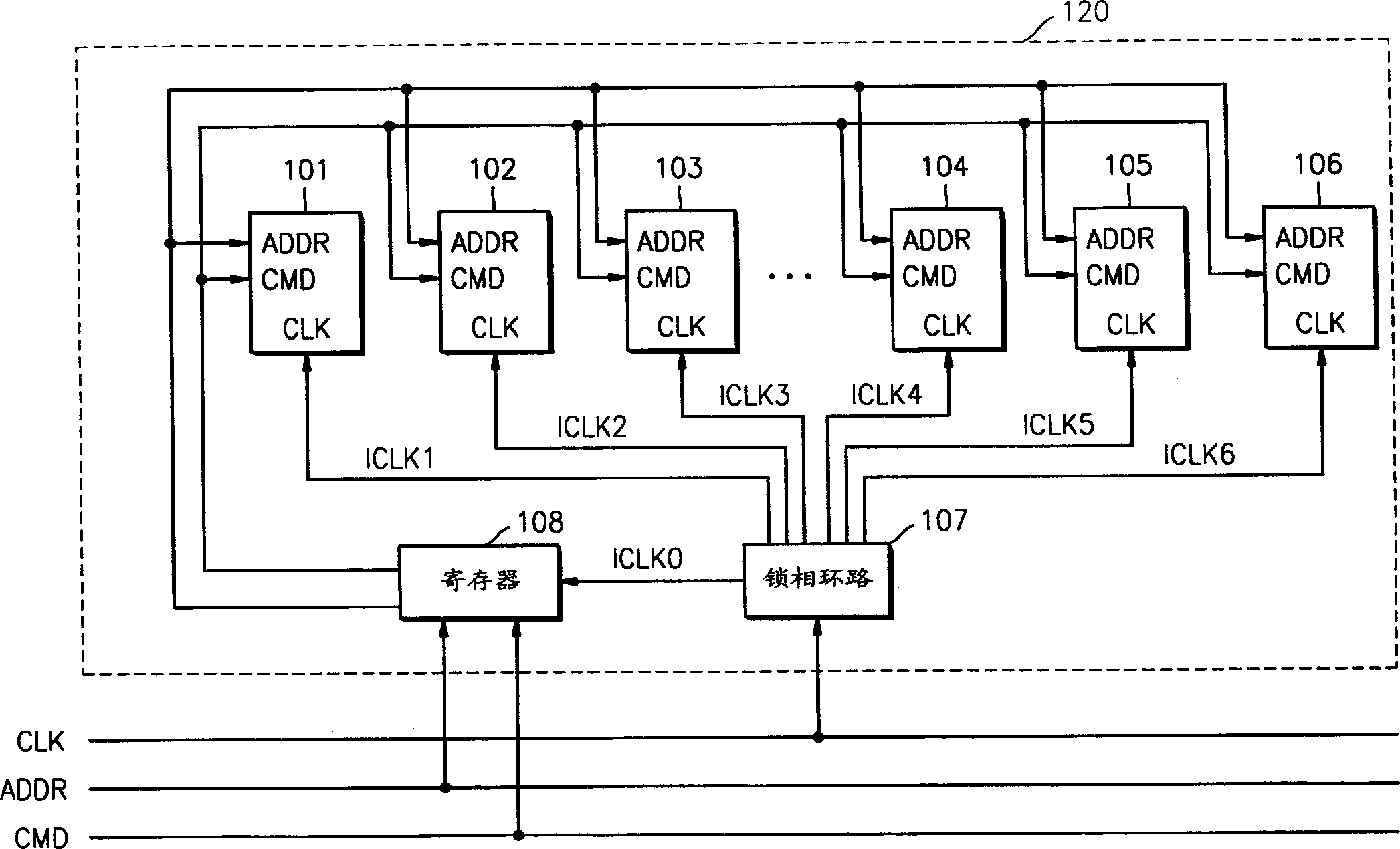

A technology of storage device and storage module, which is applied in the direction of memory system, static memory, digital memory information, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

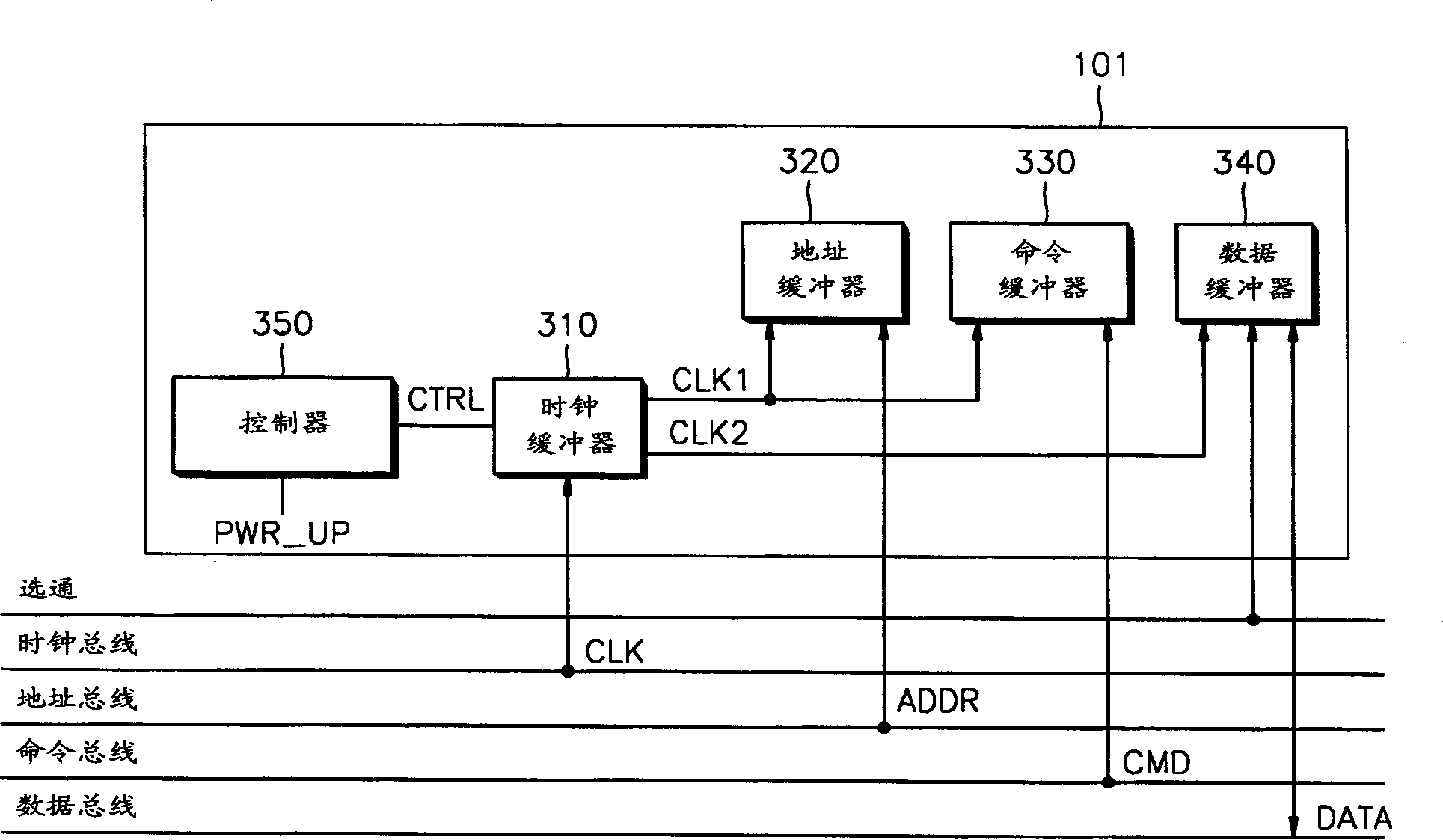

[0034] Preferred embodiments of the present invention will now be described in detail with reference to the accompanying drawings, wherein like elements are designated by like numerals.

[0035] image 3 A semiconductor memory device of a first embodiment of the present invention is explained. The semiconductor memory device 101 generally corresponds to a memory module (such as figure 1 One of the memory chips included in the module 120 ) includes a clock buffer 310 , an address buffer 320 , a command buffer 330 , a data buffer 340 and a controller 350 . The clock buffer 310 receives the clock signal CLK on the clock bus (herein referred to as "external clock signal"), and generates internal clock signals CLK1 and CLK2. Relative frequencies of the first internal clock signal CLK1 and the second clock signal CLK2 are determined by the clock buffer 310 in response to the control signal CTRL output from the controller 350 . For example, the control signal CTRL may specify whet...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More