Crystal covered package substrate

A technology of assembly and substrate, applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problems of long current path, large plane inductance value, large inductance value variation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

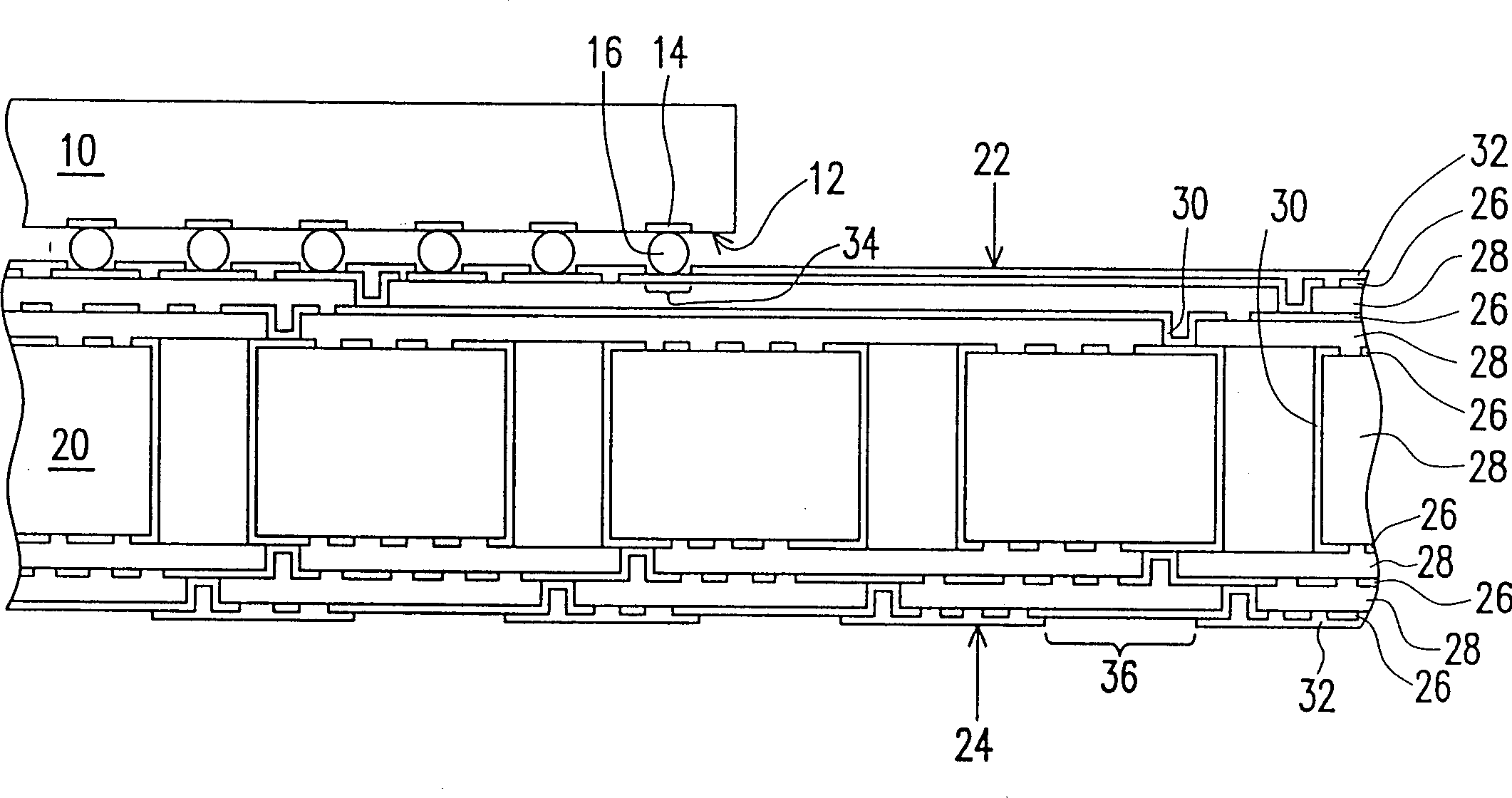

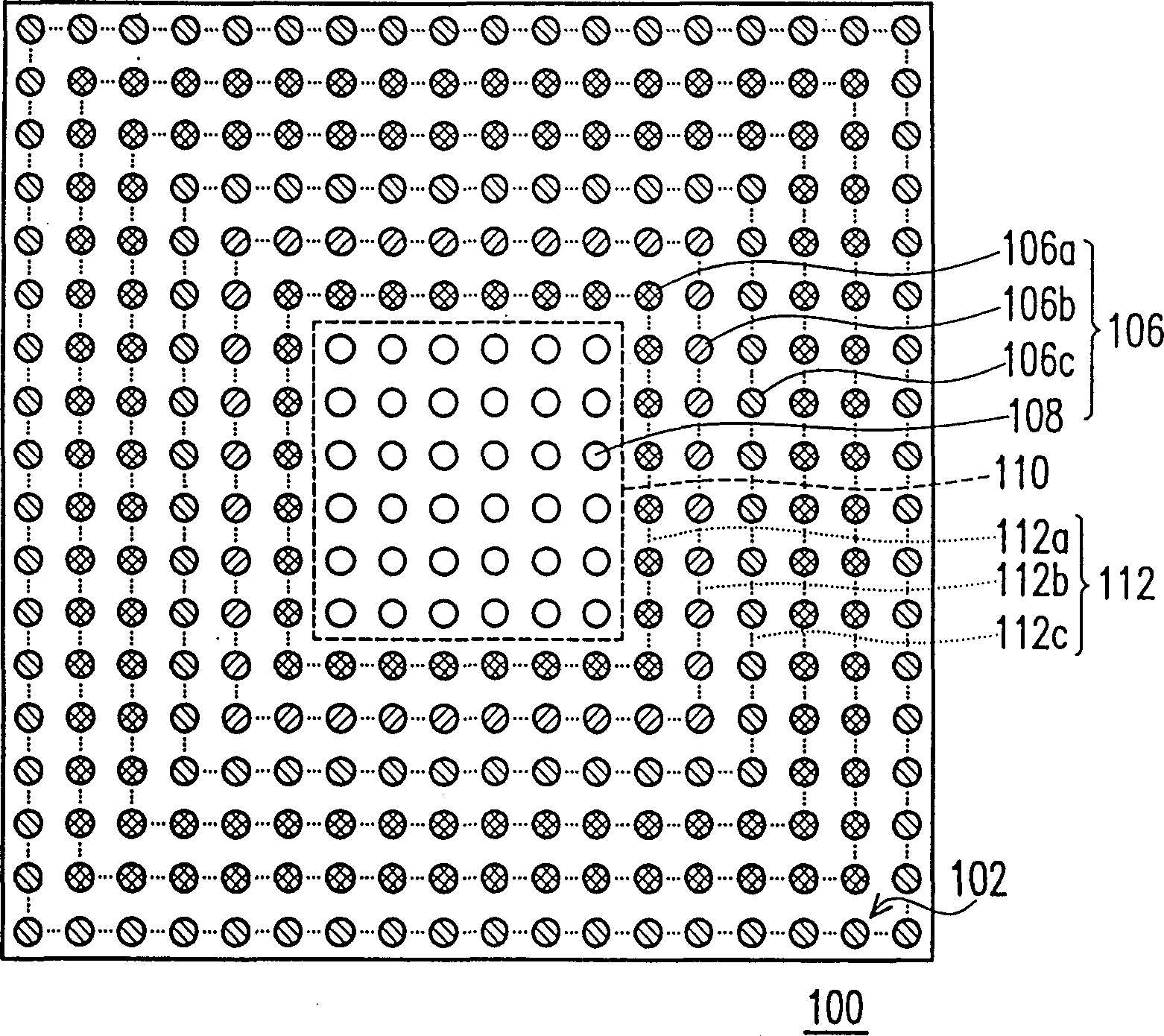

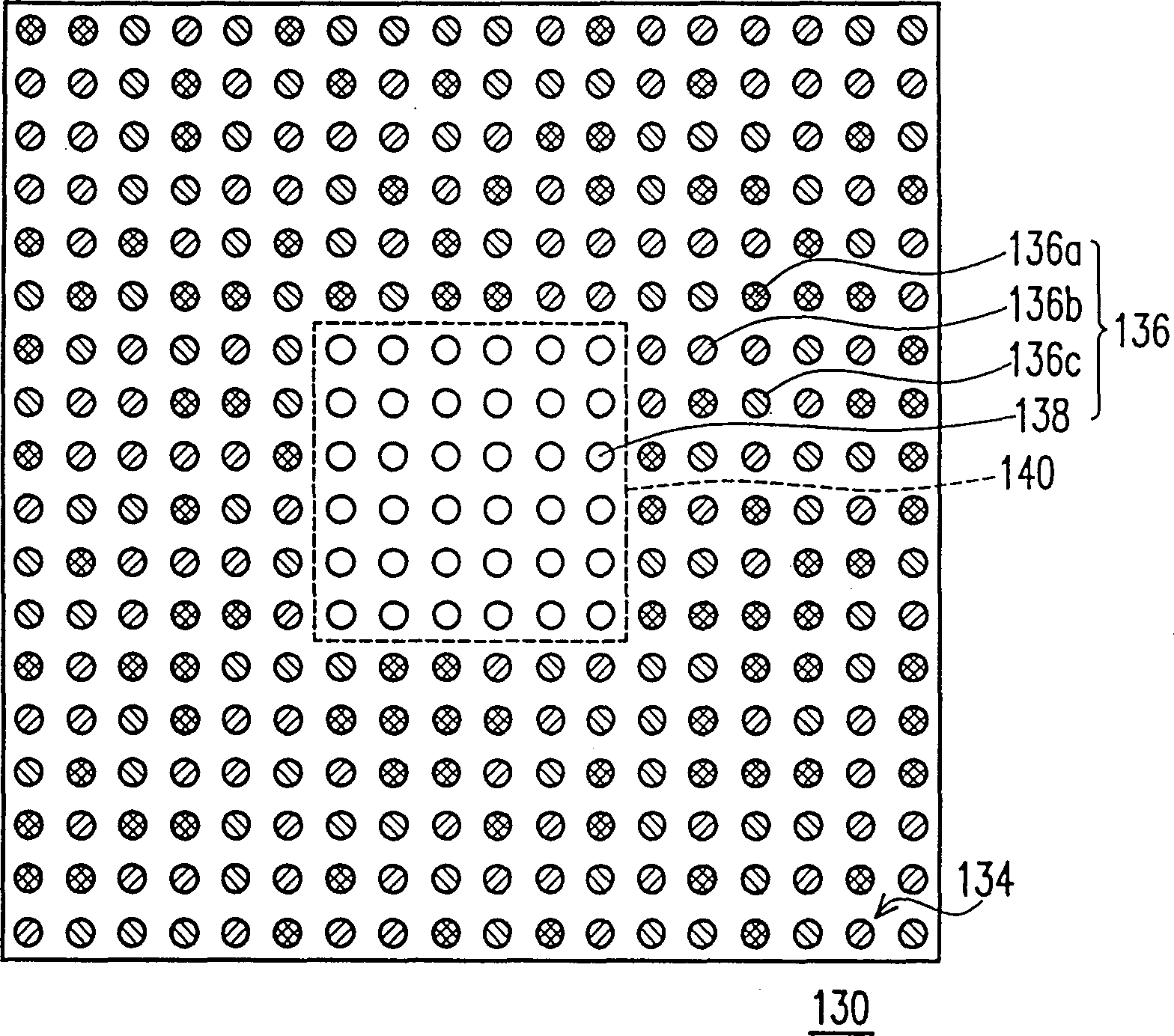

[0057] Please refer to figure 1 , Figure 4 ,in Figure 4 It is a partial top view of a flip-chip substrate of a preferred embodiment of the present invention. Figure 4 The composition structure of the flip-chip substrate 200 is the same as figure 1 The composition structure of the flip-chip substrate 20 includes a multi-layer patterned wiring layer 26, at least one insulating layer 28 and a plurality of conductive plugs 30, wherein these wiring layers 26 overlap each other in sequence, and the insulating layer 28 is They are respectively arranged between two adjacent wire layers 26 to isolate the wire layers 26 and overlap with the wire layers 26. The conductive plugs 30 respectively penetrate through the insulating layer 28 to electrically connect the wire layers 26. . also, figure 1 The top surface 22 and the bottom surface 24 of the flip-chip substrate 20 also have a solder mask layer 32 to protect the outermost conductive layer 26 and the underlying insulating layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More