Low-k interconnect structure comprised of a multilayer of spin-on porous dielectrics

A technology of interconnection structure and dielectric, applied in the direction of circuits, electrical components, electrical solid devices, etc., can solve the problems of increasing equipment purchase and maintenance costs, and achieve the effect of increasing production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example

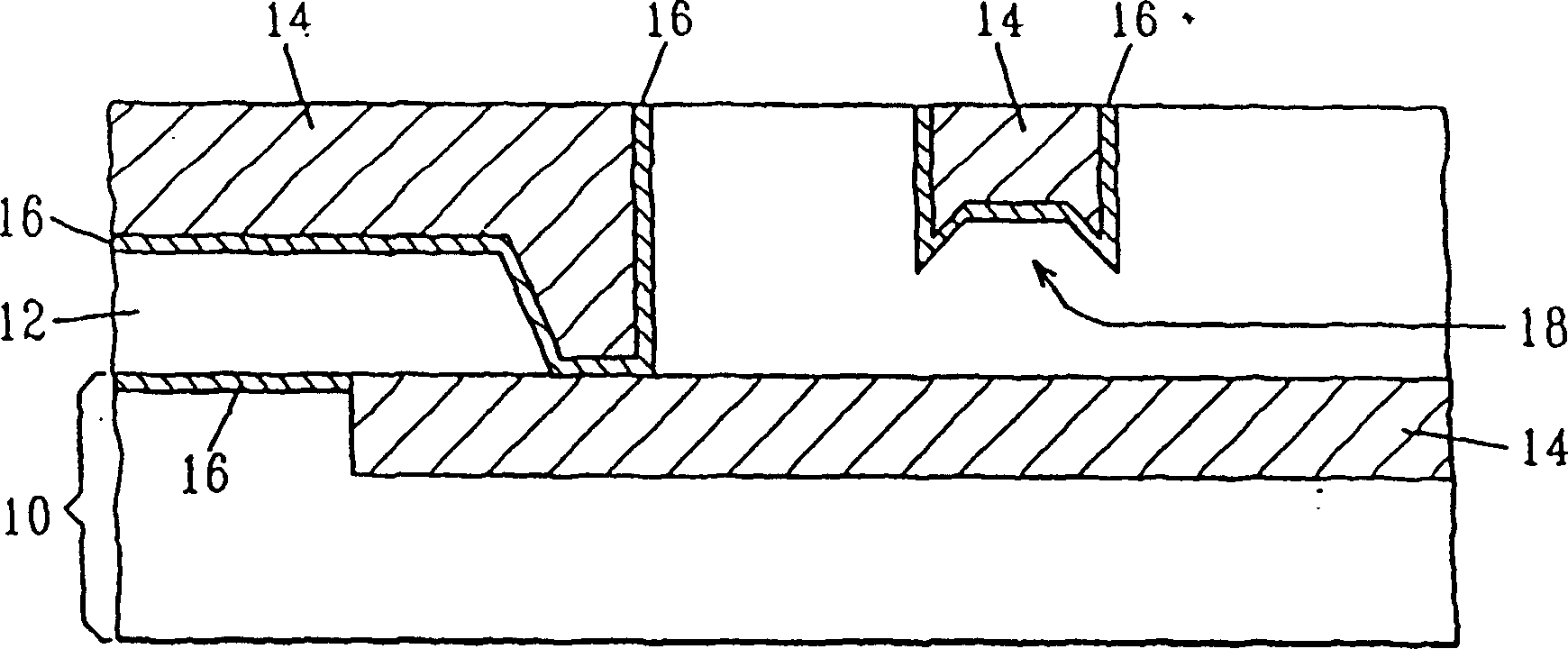

[0058]In this example, a SiLK(R) / HOSP / SiLK(R) / HOSP dielectric stack was prepared and used to form an interconnect structure. Specifically, in this example, a bare 8-inch Si wafer was used as the substrate. This wafer was treated with the adhesion promoter by applying a 2.5 weight percent solution of organosilane adhesion promoter in propylene glycol monomethyl ether acetate (PGMEA) to the wafer, followed by spinning at approximately 3000 rpm for 30 seconds . The wafer is then placed on a hot plate and baked at about 100 degrees Celsius for about 90 seconds. This bake promotes the reaction of the adhesion promoter to the surface of the wafer. After cooling to room temperature, the wafer with adhesion promoter was rinsed with propylene glycol monomethyl ether acetate (PGMEA) to remove excess adhesion promoter. The wafer was washed with about 30 milliliters (ml) of propylene glycol monomethyl ether acetate (PGMEA) and then spun at about 3000 rpm for about 30 seconds.

[0059]...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

| size | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More