Electric interconnecting structure on substrate and producing method thereof

A technology of electrical interconnection and interconnection, applied in the direction of circuits, electrical components, electrical solid devices, etc., can solve the problem of increasing the effective dielectric constant

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example

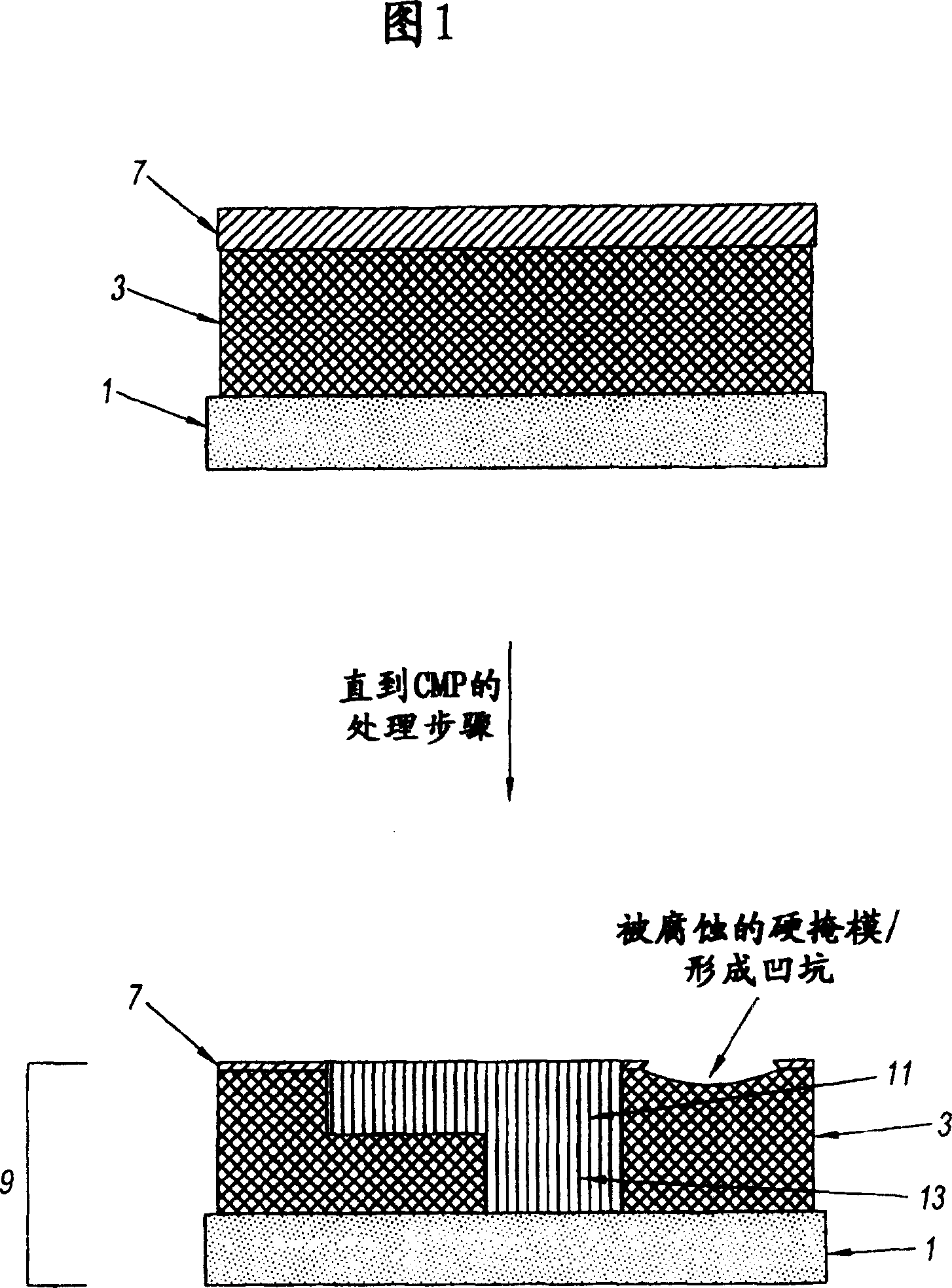

[0080] A fabricated SiLK TM / HOSP BEST TM / BLOk TM structure

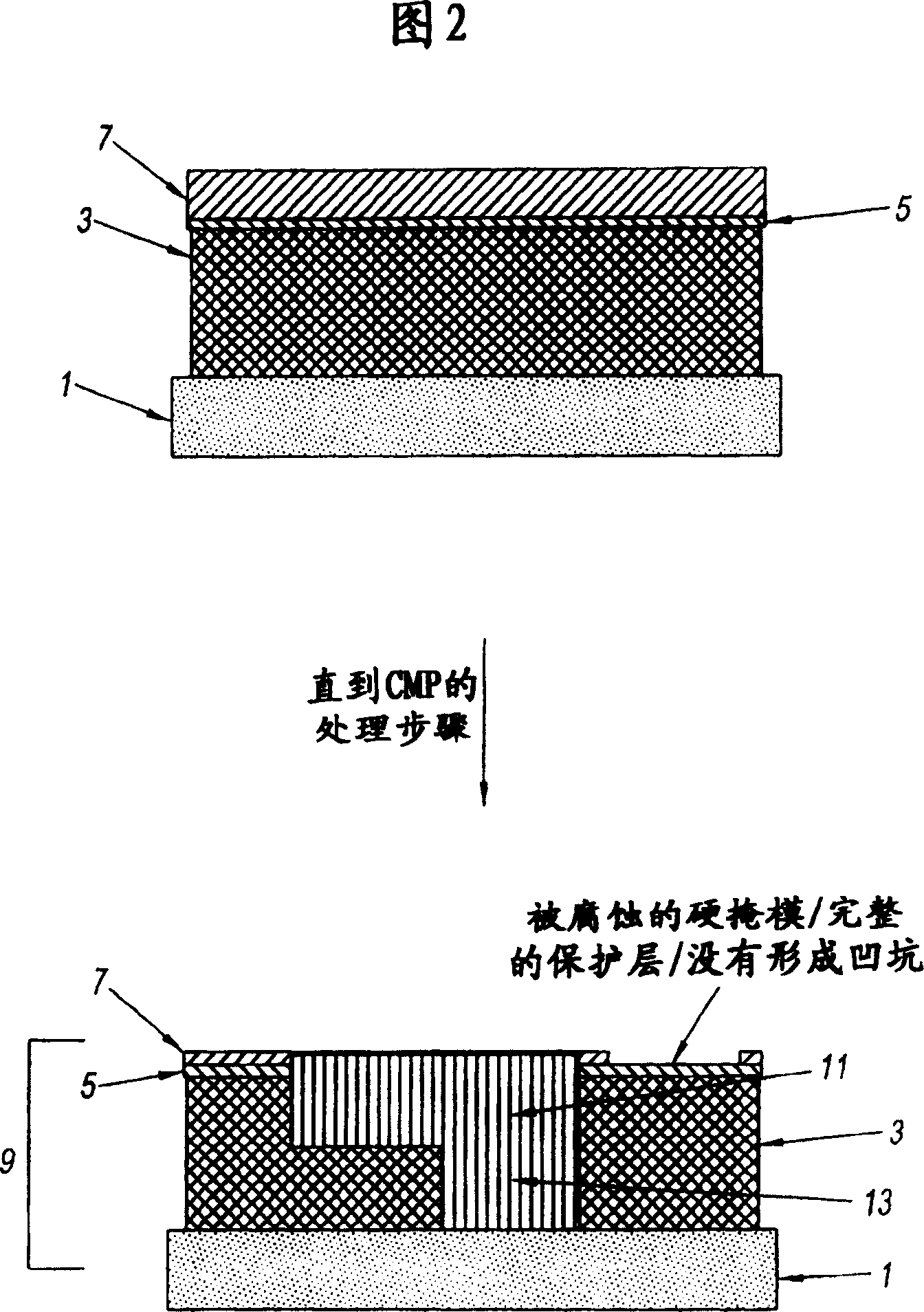

[0081] A. Lamination of dielectric layers as shown in Figure 2

[0082] steps

condition

adhesion promoter

hot plate baking

310℃ / 90s

First ILD layer (SiLK)

hot plate baking

310℃ / 2min.

CMP protection layer (HOSP BESt)

hot plate baking

310℃ / 2min

to bake

Furnace -415℃ / 60min.

CVD deposition

[0083] See Table I and Figure 2 above, by adding the AP 6000 TM A 200 mm diameter silicon wafer was treated with the adhesion promoter by coating the solution onto the wafer and then spinning at 3000 rpm for 30 seconds. At 22, the wafer was then placed on a hot plate at 310° C. for 120 seconds for a first hot plate bake.

[0084] After cooling the wafer to room temperature, the first layer of low-k dielectric (SiLK TM ) (Figure 2, layer 3). SiLK TM The solution w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More