Double-grid vertical channel field effect transistor and its manufacturing method

A technology of transistors and dojos, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of poor quality of single crystal silicon, large leakage current of devices, and inability to realize dual-gate vertical channel devices, etc. The effect of suppressing the short-channel effect of the device, reducing the leakage current, and high integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

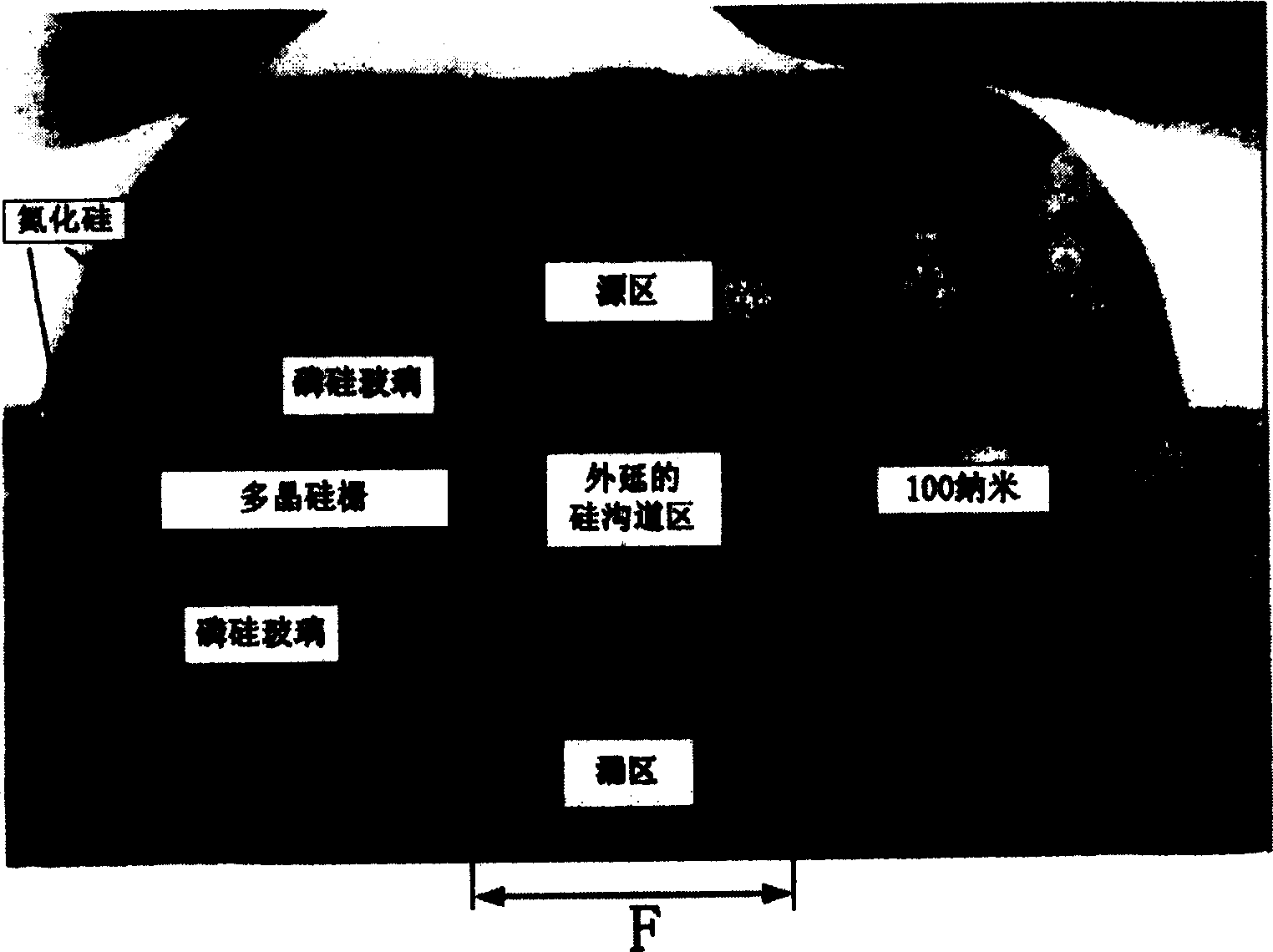

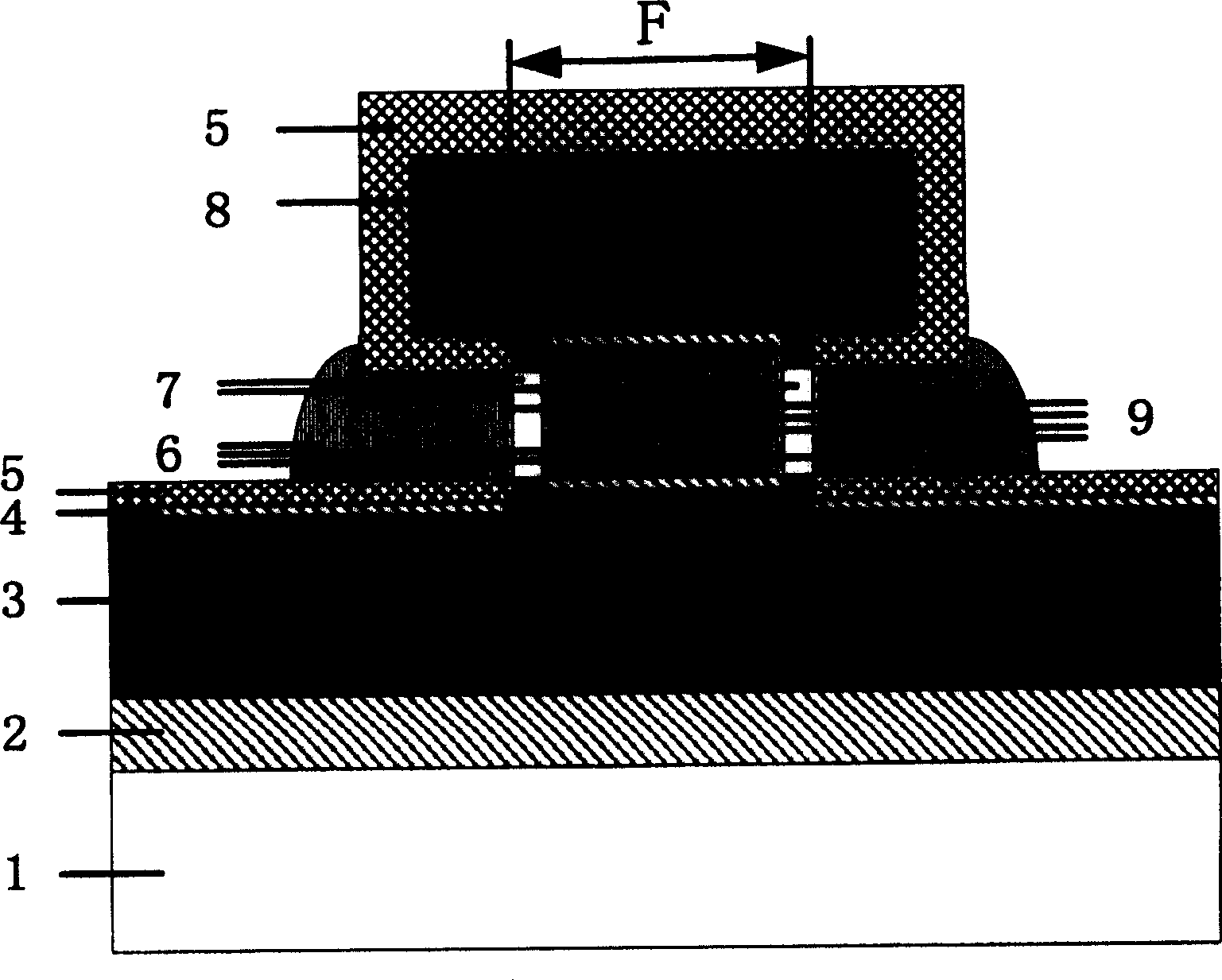

[0024] Such as figure 2 As shown, it is a schematic cross-sectional structure diagram of a specific embodiment of the novel fully depleted double-gate vertical channel field-effect transistor of the present invention. ) 3, buffer silicon dioxide 4, deposited silicon nitride 5, polysilicon germanium gate 6, vertical channel 7, polysilicon drain region (n+ doped) 8 and gate oxide layer 9. The channel length of the device is 50 nanometers (that is, the thickness of the silicon dioxide replacement gate layer is 50 nanometers), the thickness of the channel region is 20 nanometers (that is, the thickness of the polycrystalline germanium sacrificial layer is 20 nanometers), and the thickness of the gate oxide layer is 1.5 nanometers, using a 248-nanometer (optical lithography feature size F) process.

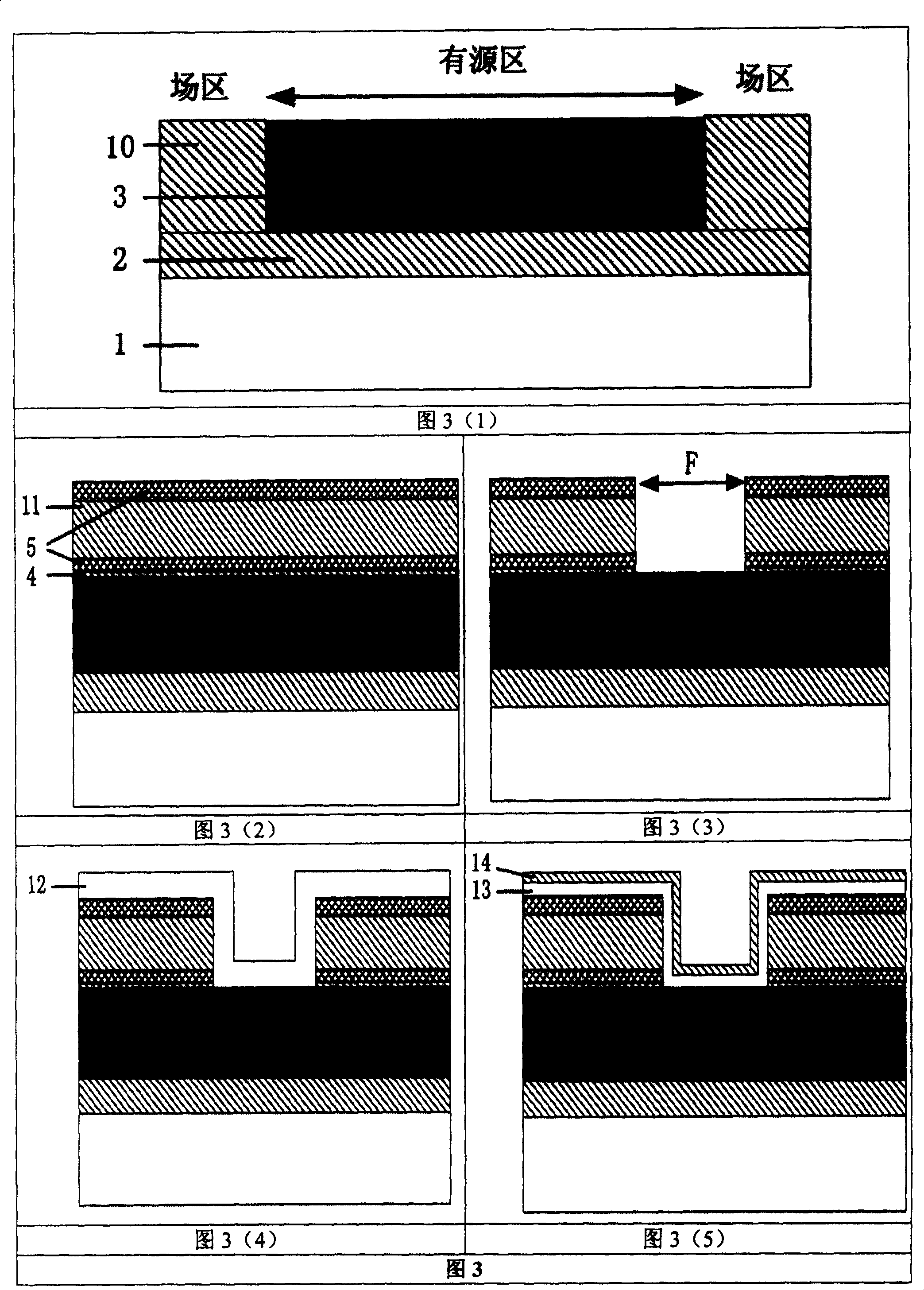

[0025] An implementation method for preparing the above-mentioned vertical channel field effect transistor with a fully depleted double-gate structure will be described in detail bel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More