Processor and compiler for creating program for the processor

A processor and program execution technology, applied in the field of branch instructions, which can solve problems such as reducing real-time performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

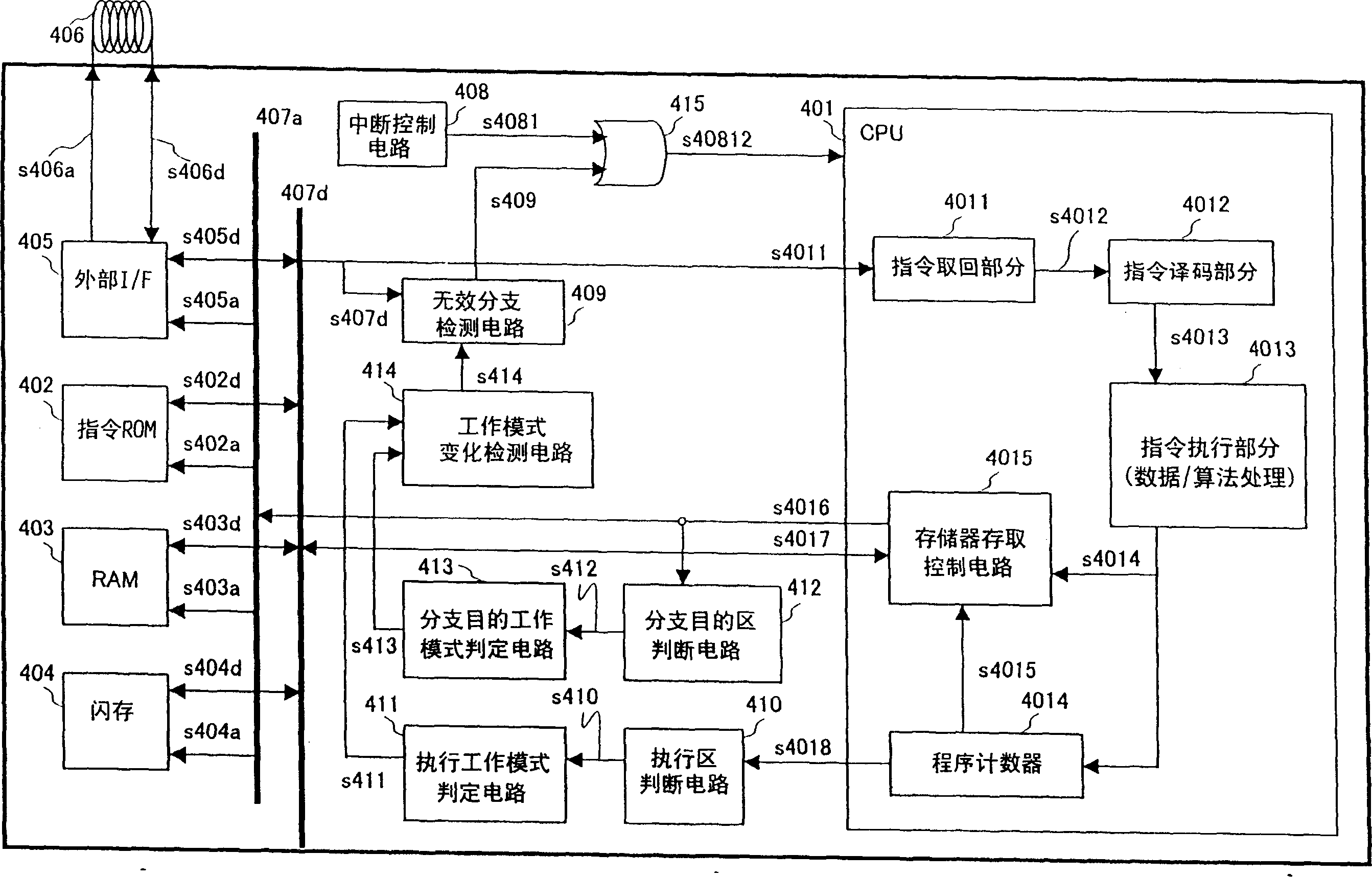

[0037] will refer to the attached figure 1 One embodiment of the processor 400 of the present invention is described.

[0038] figure 1 A block diagram of an IC card system using the processor 400 of this embodiment is shown.

[0039] Such as figure 1 As shown, the IC card system includes the following: CPU 401; instruction ROM 402; RAM403; flash memory 404; external I / F 405; antenna coil 406; address bus 407a; data bus 407d; interrupt control circuit 408; invalid branch detection circuit 409 Execution area judgment circuit 410; Execution work mode judgment circuit 411; Branch destination judgment circuit 412; Branch destination work mode judgment circuit 413;

[0040]The CPU 401 includes an instruction retrieval unit 4011 , an instruction decoding unit 4012 , an instruction execution unit 4013 , a program counter 4014 , and a memory access control circuit 4015 .

[0041] CPU 401 reads instructions from instruction ROM 402 or flash memory 404 and then executes the instr...

Embodiment 2

[0058] The following is a description of an IC card system using the processor 400 of Embodiment 2 of the present invention.

[0059] The hardware structure of the IC card system in the present embodiment is identical with the IC card system in embodiment 1 (see figure 1 ). Moreover, when the processor 400 of this embodiment is used, the division of the memory space divided into a plurality of regions is also the same as in Embodiment 1 (see Figure 7 ).

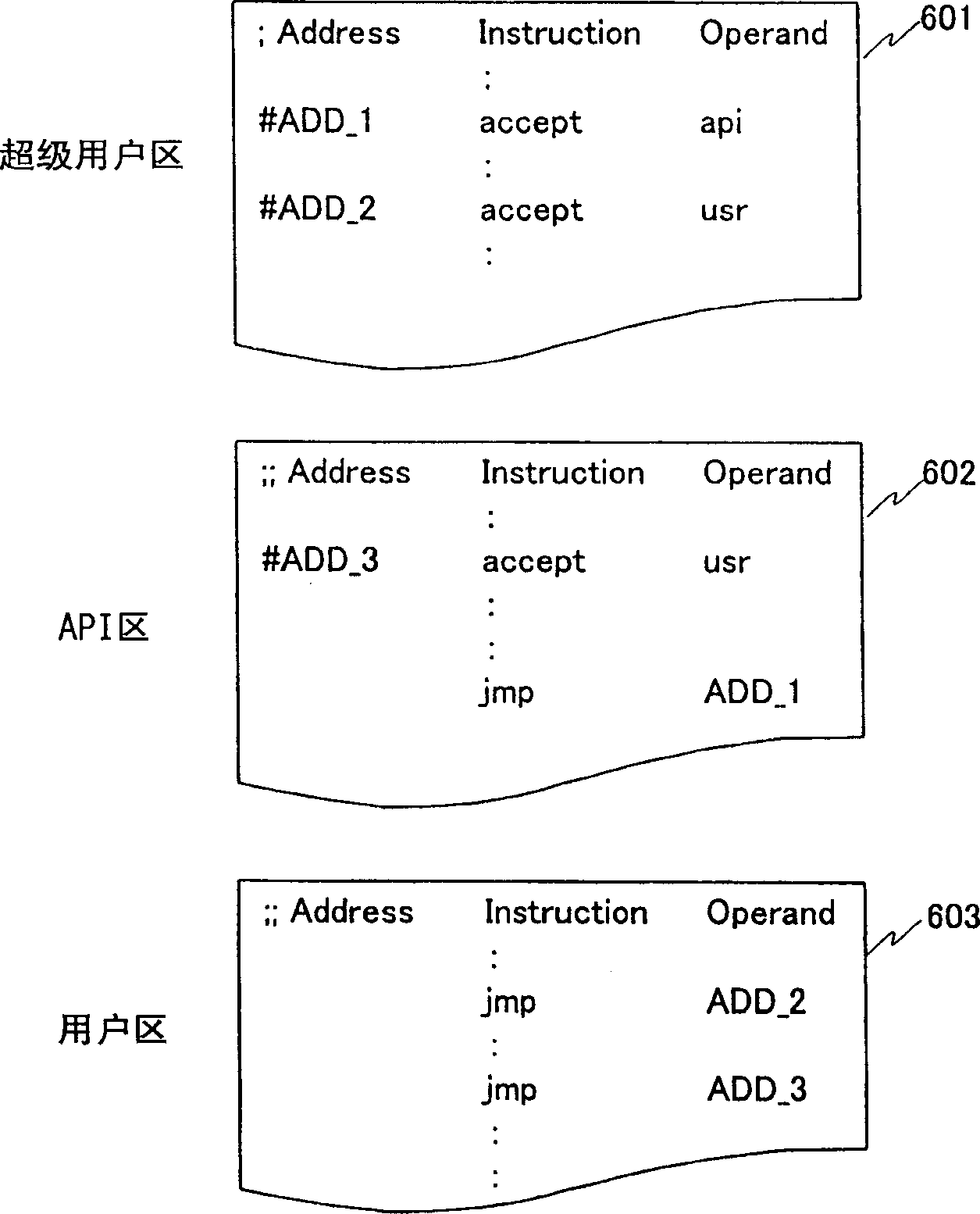

[0060] image 3 is a conceptual diagram of programs used in processor 400 of this embodiment.

[0061] The API program 602 in the API storage space includes a branch enabling instruction (accept usr), which is used to determine the API area when the execution is transferred from the user program 603 in the user area to the API program 602 in the API area by a branch instruction (jmp). Whether the branch destination address in is valid.

[0062] The supervisor program 601 in the supervisor area also includes a branch en...

Embodiment 3

[0078] The following is a description of an IC card system using the processor 400 of Embodiment 3 of the present invention.

[0079] The hardware structure of the IC card system in the present embodiment is identical with the IC card system in embodiment 1 (see figure 1 ). Moreover, when the processor 400 of this embodiment is used, the division of the memory space divided into a plurality of regions is also the same as in Embodiment 1 (see Figure 7 ). .

[0080] image 3 is a conceptual diagram of programs used in processor 400 of this embodiment.

[0081] The API program 602 in the API area includes a branch enabling instruction (accept usr), which is used to determine the API program 602 in the API area when the execution is transferred from the user program 603 in the user area to the API program 602 in the API area by a branch instruction (jmp). Whether the branch destination address of the branch is valid.

[0082] The supervisor program 601 in the supervisor ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More