Time delayed testing generation method for wire-to-wire crosstalk decereration effect

A technology of time-delay test and deceleration effect, applied in semiconductor/solid-state device test/measurement, electrical components, electro-solid-state devices, etc., it can solve the problems of large number of faults, difficult to find tests, long calculation time, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

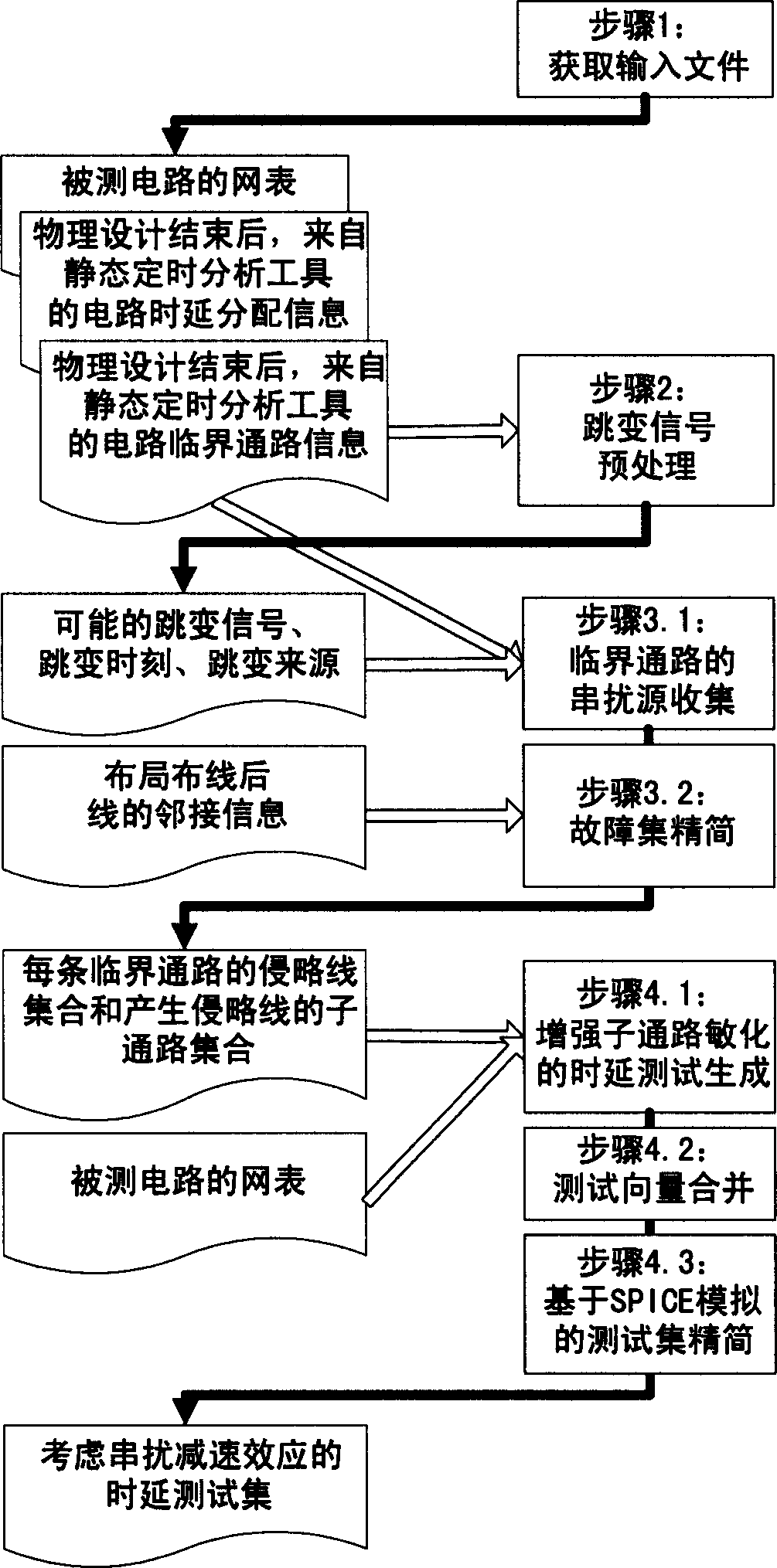

[0037] figure 1 The rectangular block diagram in the middle right half shows the main steps to realize the method, figure 1 The file block diagram in the middle left half shows the output files and input files of each step. figure 1 The solid black arrows in indicate "file output", and the hollow arrows indicate "file input".

[0038] figure 1 In the prototype system of the time delay test generation method for crosstalk deceleration effect between lines, the 4 steps introduced in the technical solution of the invention are included. Except that SPICE simulation adopts off-the-shelf commercial tools, we have implemented tool prototypes in C language for other parts, which can test and generate benchmark circuit netlists in the research field.

[0039] We use figure 1 The system is tested on the reference circuit netlist ISCAS89 in the research field (the reference circuit proposed by the International Conference on Circuits and Systems in 1989). Due to the lack of real phy...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More