ATE test equipment-oriented novel integrated circuit test excitation generation method

A technology of testing excitation and testing equipment, which is applied in the direction of electronic circuit testing, measuring electricity, measuring electrical variables, etc., can solve the problems of incomprehension of the specific content of the test and the specific process of the test, high labor costs, difficulties, etc., to improve intuitive and readability, improve compatibility and adaptability, and reduce difficulty and complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

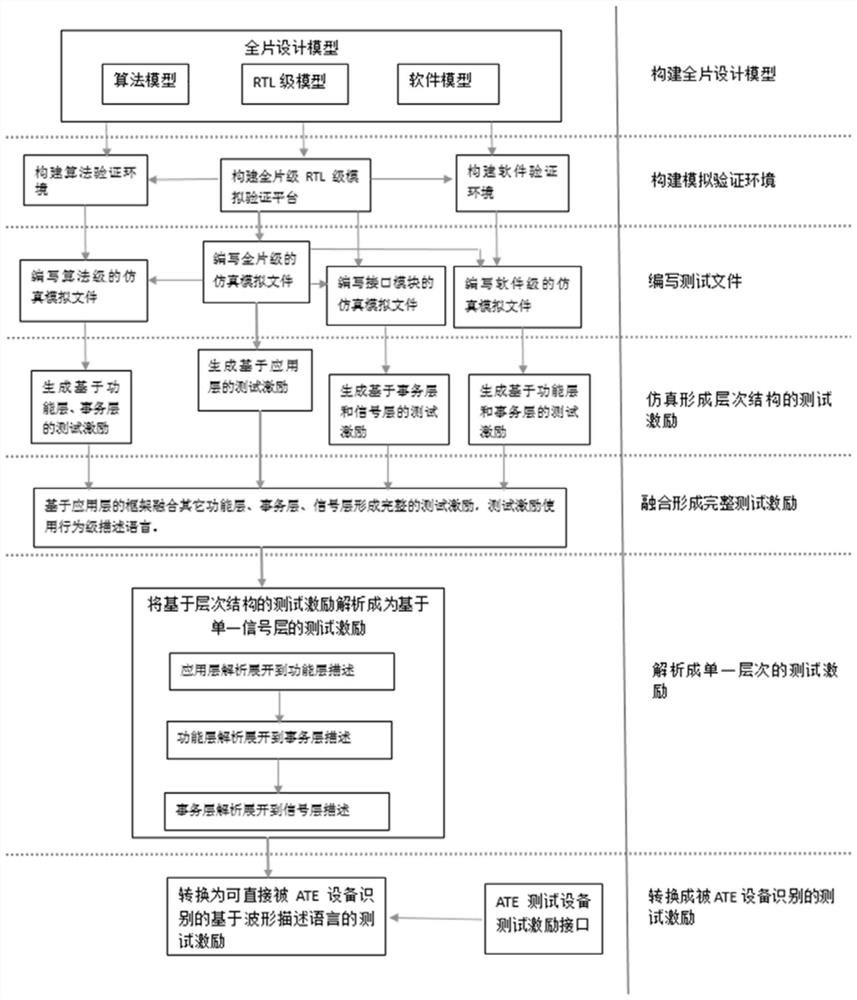

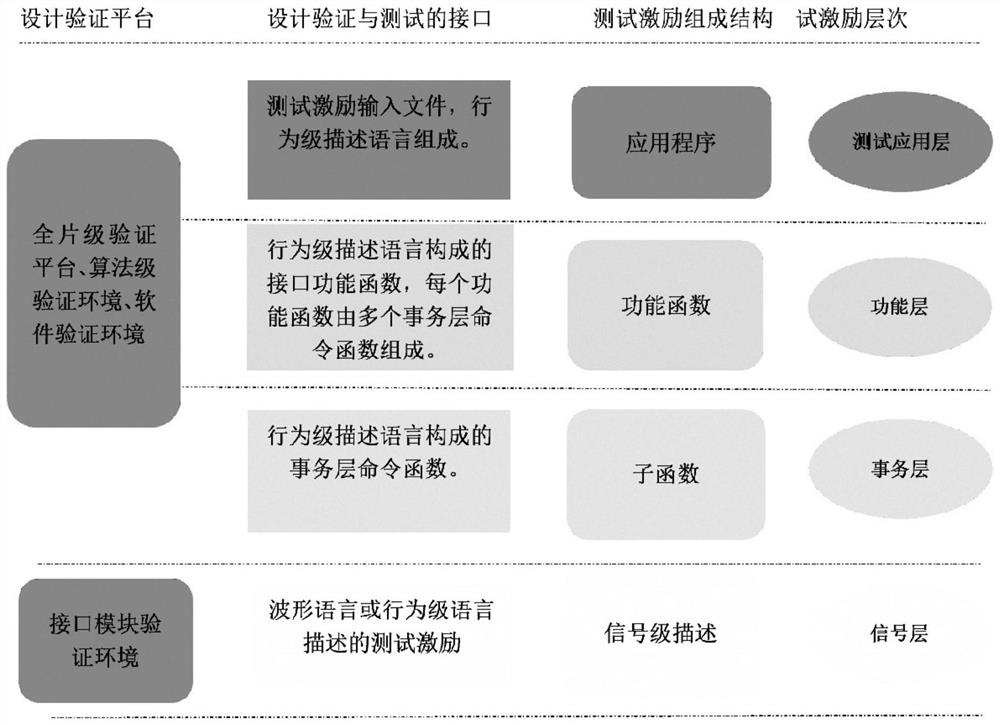

[0034] Embodiment: the present invention provides a kind of novel integrated circuit test stimulus generation method facing ATE test equipment, this test stimulus generation method generates test stimulus by verification platform simulation simulation on the basis of integrated circuit design environment, the test stimulus of generation is mainly used in Test the circuit on ATE test equipment, this method is mainly suitable for the generation of integrated circuit function test stimulus;

[0035] Include the following steps:

[0036] Step 1. Build a full-chip design model. Traditional ATE test stimulus generation requires the construction of a unified full-chip RTL-level design model. In this solution, the full-chip design model does not require all design modules to be RTL-level, but the overall design The model framework should be at RTL level, which constitutes the module-level design model of the whole chip design model, and can use algorithm models, software models or oth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More