Memory rewind and reconstruction for hardware emulator

A random access memory and storage unit technology, applied in static memory, software simulation/interpretation/simulation, detection of faulty computer hardware, etc., can solve problems such as neglect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

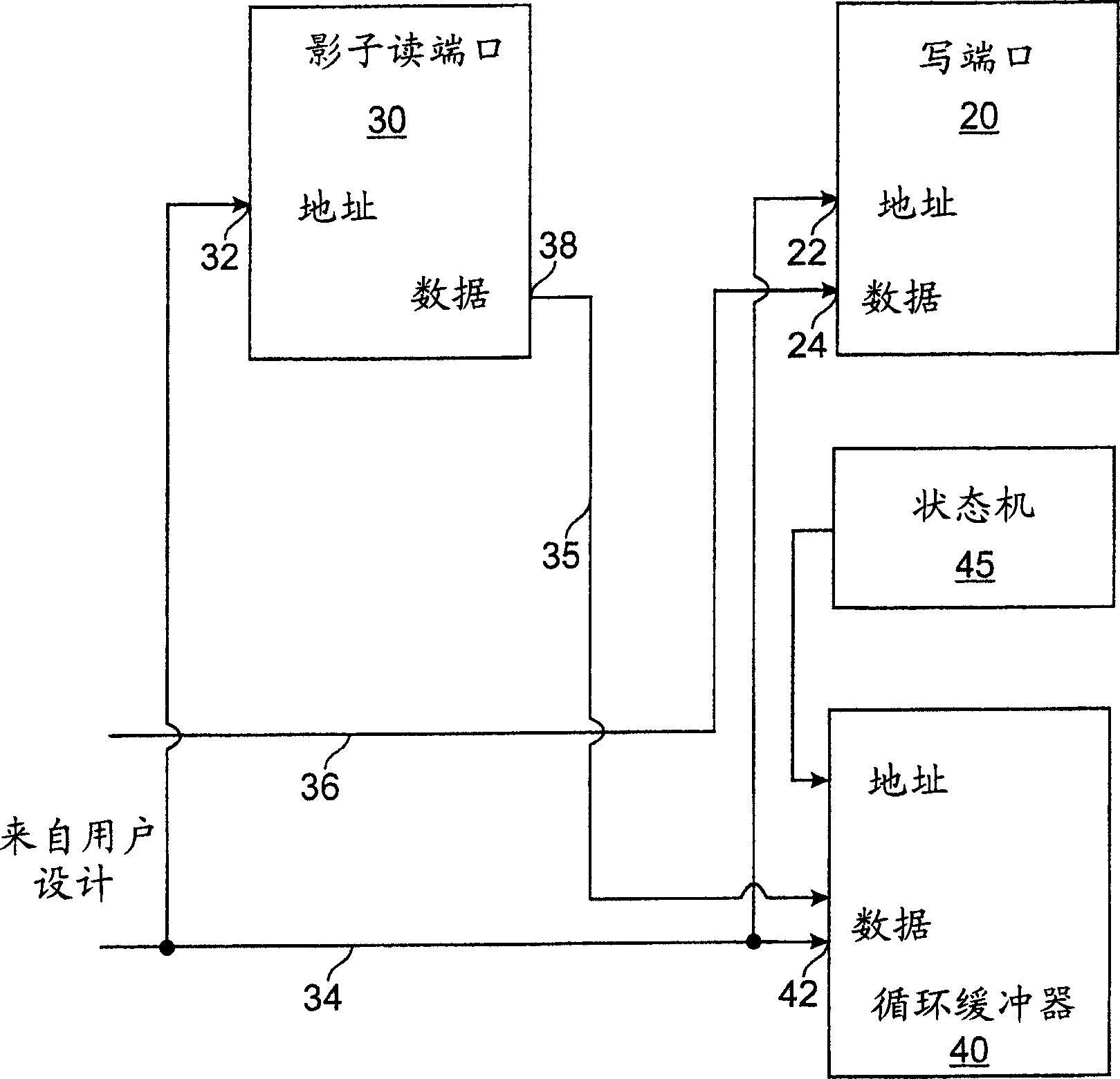

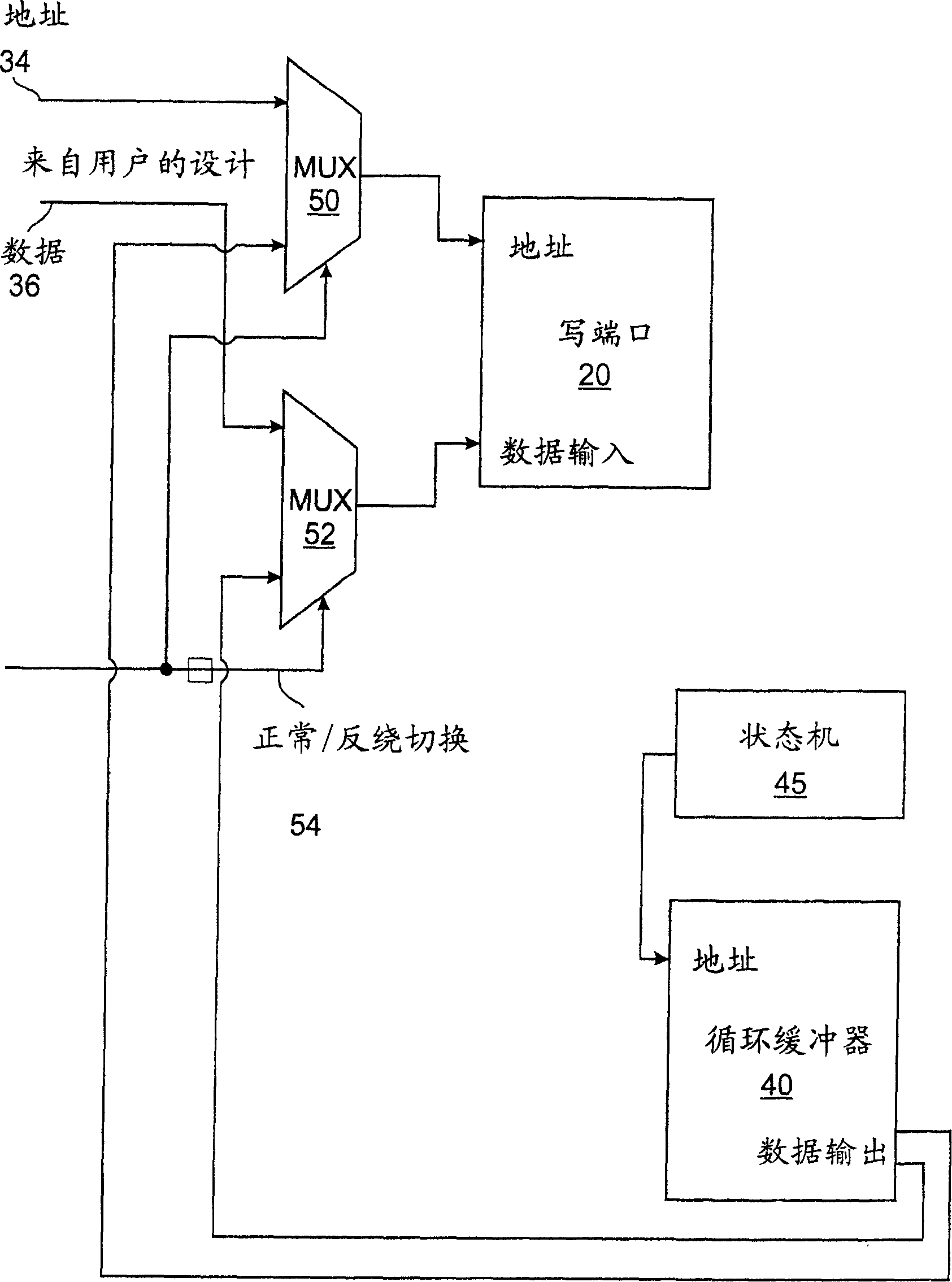

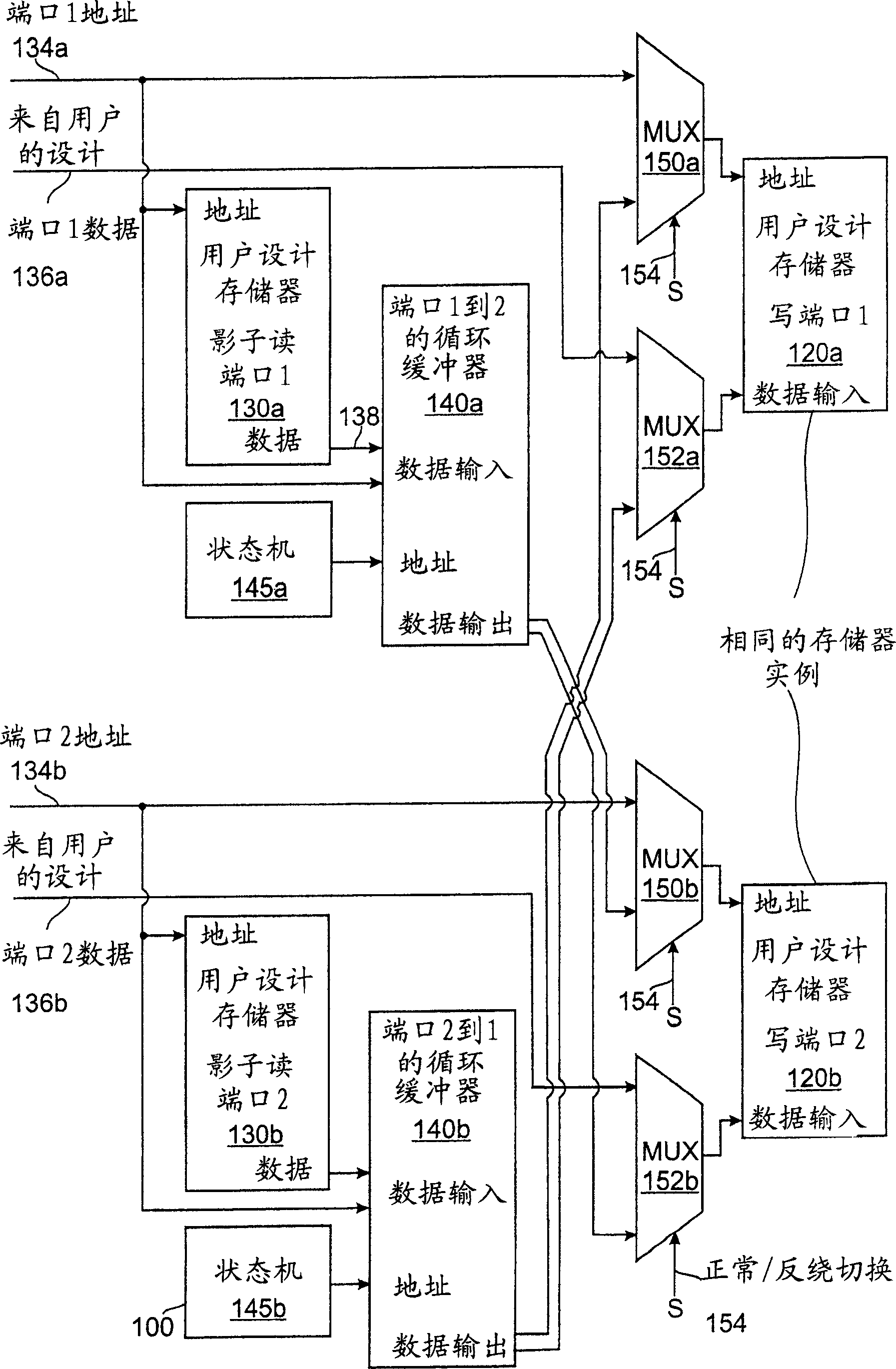

[0054] Opening the drawings, the preferred apparatus and method of the present invention will now be described.

[0055] As will now be seen, one embodiment has three main parts. These parts are "Capture", "Rewind" or "Reconstruct", and "Replay". The capture is performed while the DUV is running in the emulator, in the context of various embodiments of the invention, capture refers to the capture of memory write operations. As will now be shown, memory write data is captured into a circular buffer. The depth of this circular buffer determines the length of the time interval used for rewinding or reconstruction, ie the trace window.

[0056] First, it must be noted that most of the discussion of the various embodiments herein will be in the context of logic gates. In processor-based simulation systems, this approach is implemented by compiling the logic into Boolean expressions to be executed by the processor. For users of simulated systems, the output of a processor-based ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More