Processing method and apparatus for implementing systolic arrays

A technology of systolic array and processing equipment, applied in the direction of systolic array, electrical digital data processing, digital data processing components, etc., can solve the problems of impractical implementation of VLIW, complex structure, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

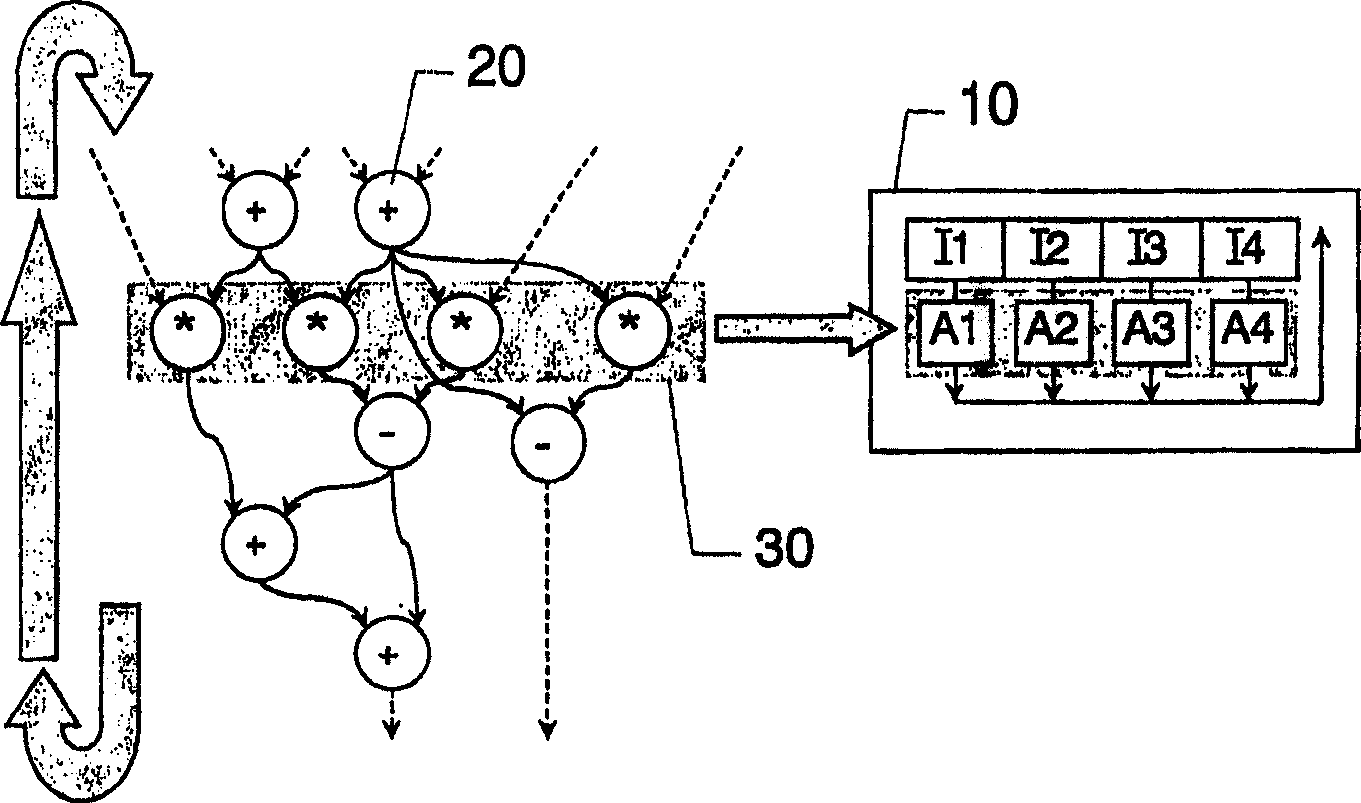

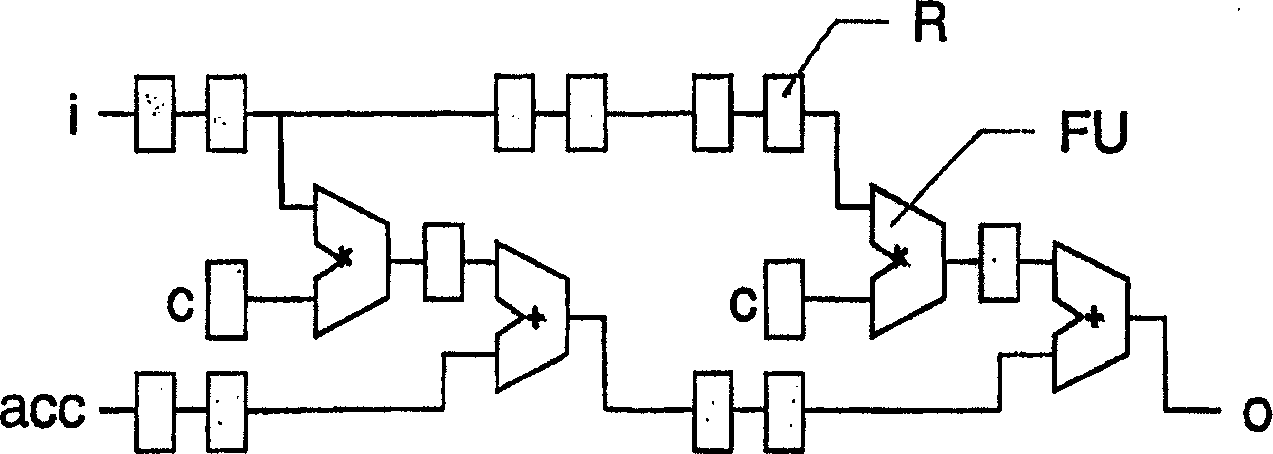

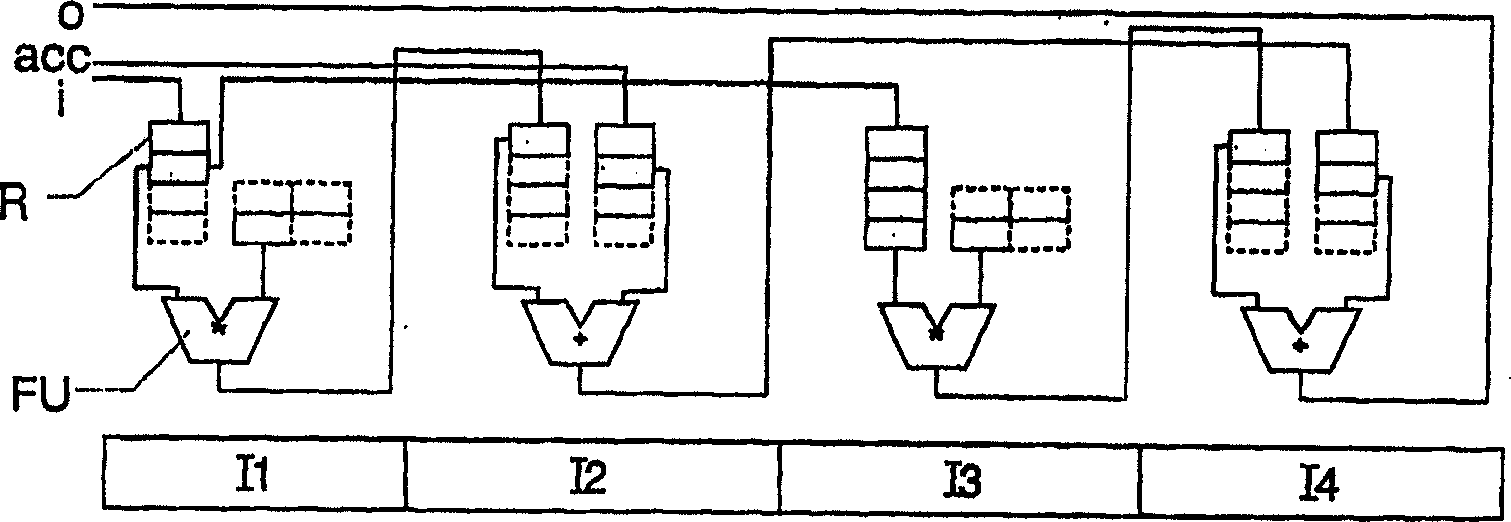

[0022] exist image 3 in, refactored figure 2 of systolic arrays to enable their implementation in VLIW architectures. Outgoing slots I1 to I4 are made explicit and a first-in-first-out (FIFO) delay line comprising register R is maintained at the input of a functional unit (eg, ALU). Dashed boxes represent physical registers that are available in hardware but are not used in the systolic configuration shown. The technical solution thus delineated suggests a VLIW template that can efficiently map systolic structures. By providing a distributed register file on each input of a functional unit FU, it is possible to generalize image 3 The intuitive concept shown in .

[0023] Figure 4 A programmable processor architecture is shown as a preferred embodiment of a VLIW template that can efficiently map systolic structures. In particular, one distributed register file DCF is provided for each input of each functional unit FU. Furthermore, an interconnection network consistin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More