Semiconductor device including bipolar junction transistor with protected emitter-base junction

A technology of bipolar junction transistors and semiconductors, applied in semiconductor devices, semiconductor/solid-state device manufacturing, transistors, etc., can solve the problems of reduced current amplification factor and increased leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

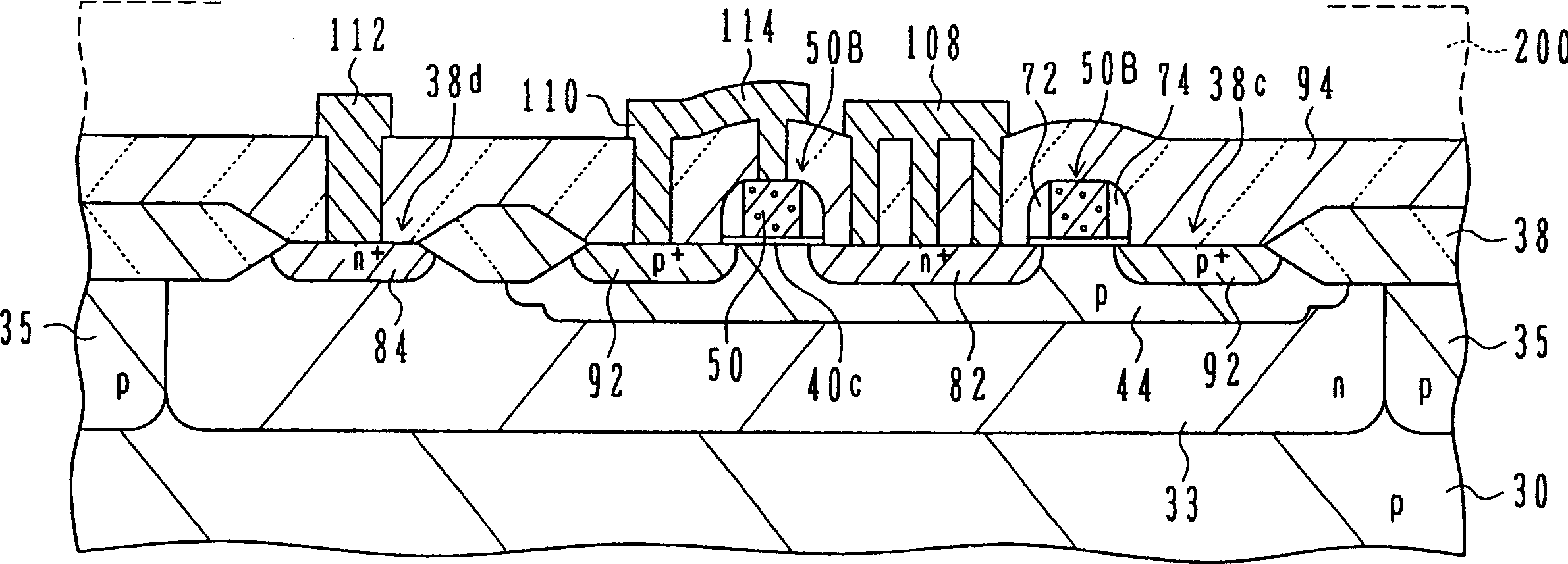

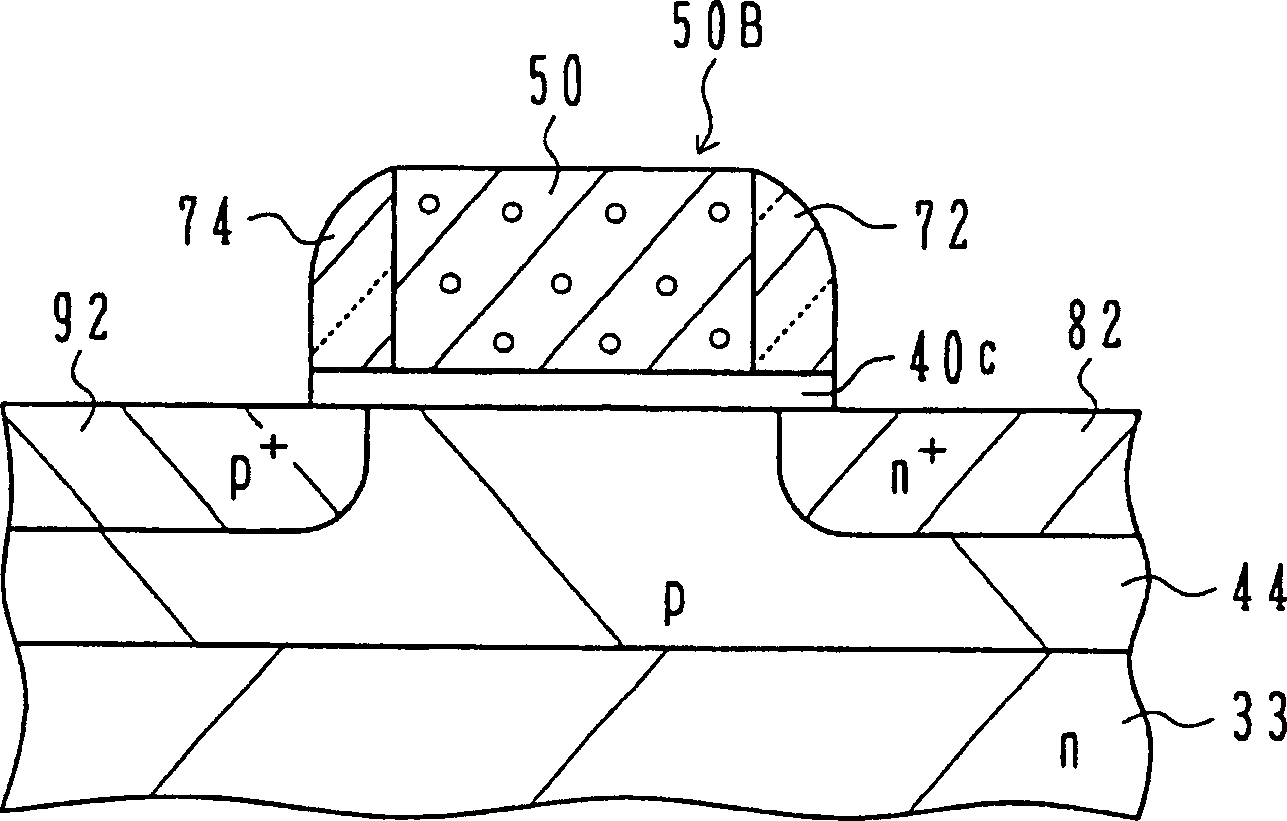

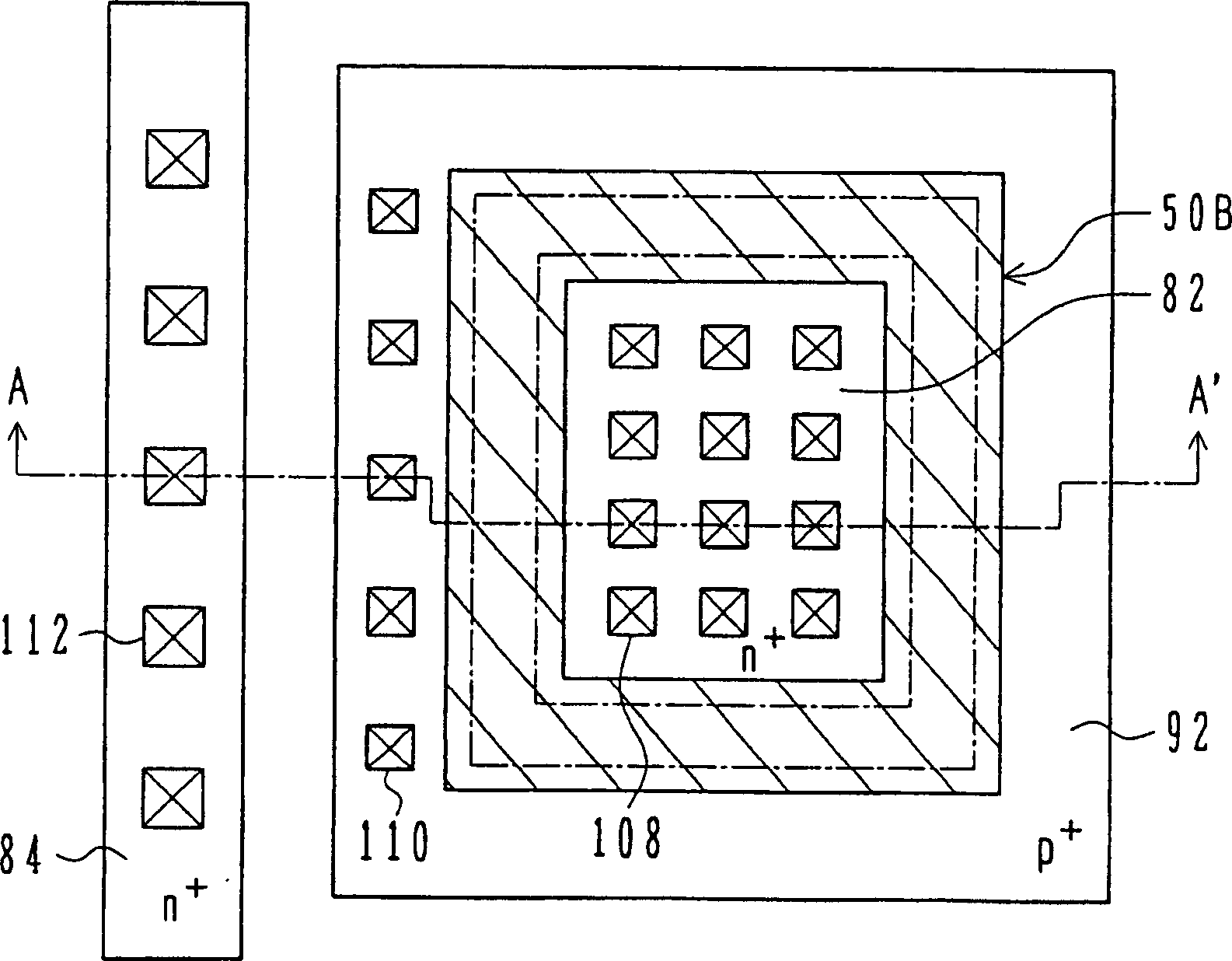

[0055] Before describing the examples, preliminary studies by the present inventors will be described.

[0056] Figure 23 An example of a bipolar transistor fabricated by the present inventors in the course of research is shown. In this example, the number of steps is reduced.

[0057] On one main surface layer of p-type silicon substrate 20, n-type collector region 21 and p-type isolation region 22 are formed. The n-type region 21 is formed by using an ion implantation process to form an n-type well of a p-channel MOS transistor in the CMOS transistor region. The p-type region 22 surrounding the n-type region 21 is formed by using an ion implantation process to form a p-type well of an n-channel MOS transistor in the CMOS transistor region.

[0058] On the surface of the substrate 20 is formed a field oxide film 23 having emitter / base holes 23a and collector contact holes 23c. The oxide film 23 is formed by using a selective oxidation process for forming a field oxide fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More