Extracting wiring parasitics for filtered interconnections in an integrated circuit

A technology of integrated circuits and parasitic resistance, which is applied in the field of electronic design automation and can solve problems such as a large amount of memory and processing power

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

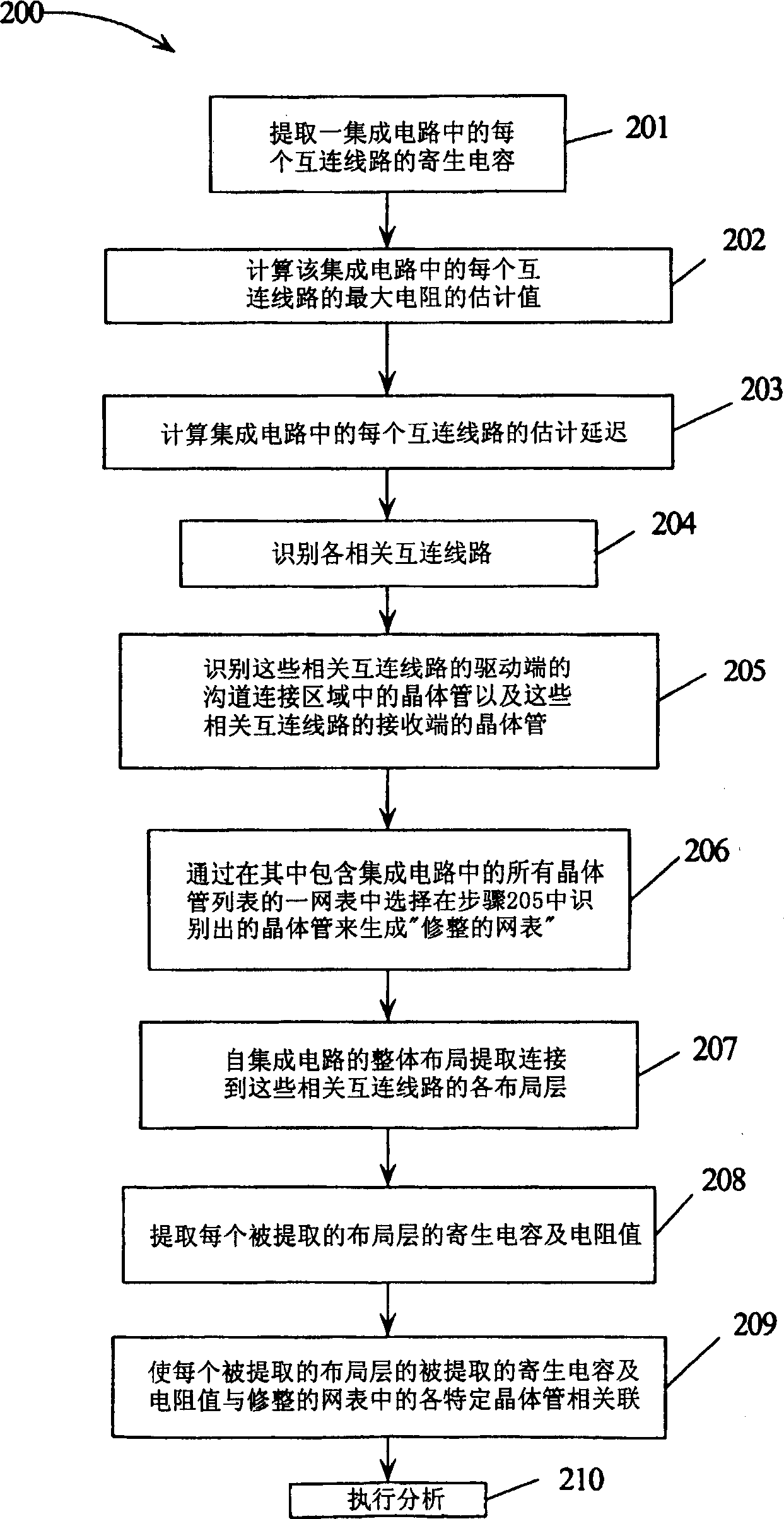

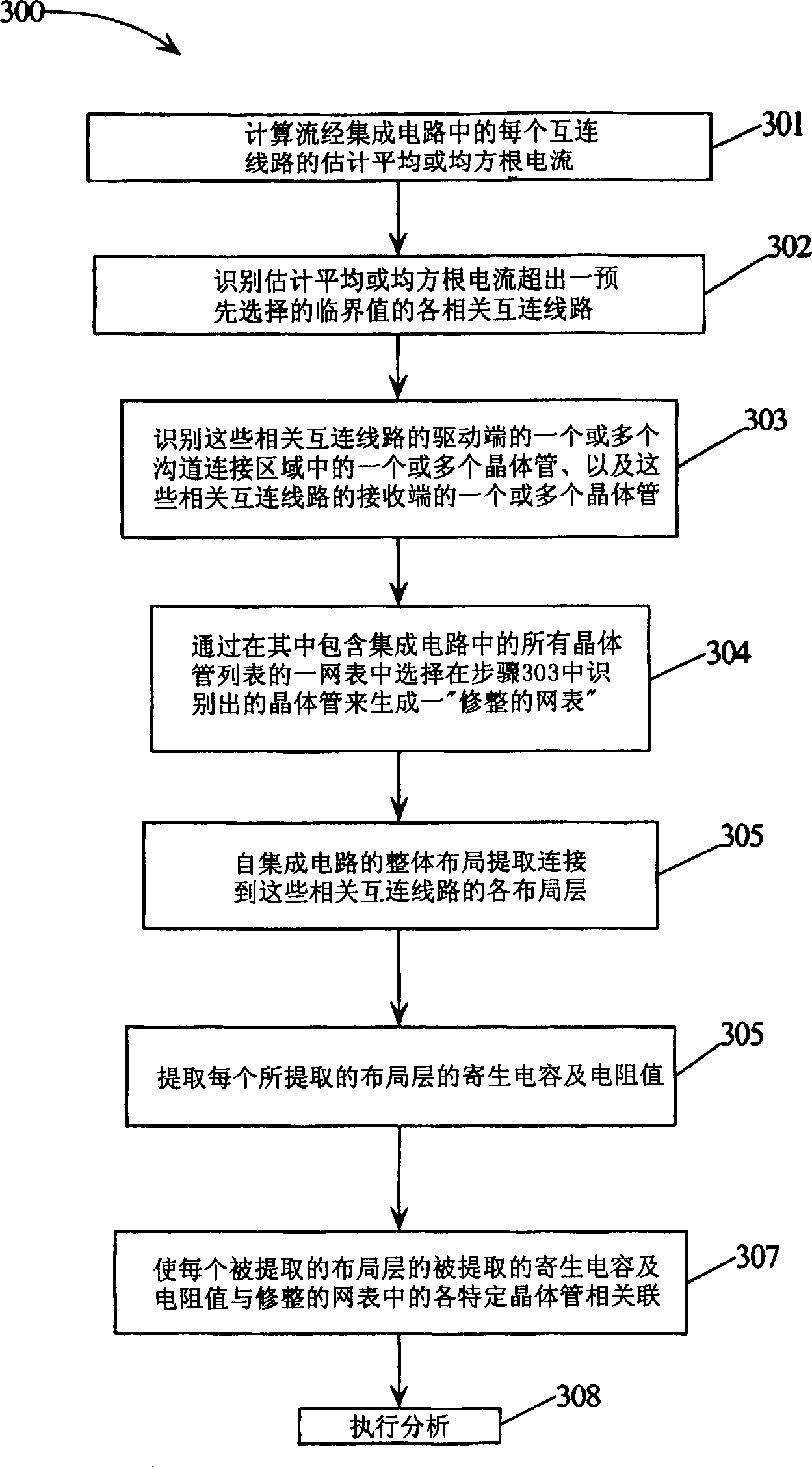

Method used

Image

Examples

Embodiment Construction

[0015] Please note that although extraction of parasitic resistance and capacitance values to perform a delay and an electromigration analysis will be described below, the principles of the invention outlined below can be applied to applications such as power line net voltage drop analysis, clock network analysis, coupling Analysis and other types of analysis. Note also that one with ordinary knowledge in the art can apply the principles of the present invention to these types of analyses. Note also that embodiments that perform such analysis would still be within the scope of the present invention. Note also that for ease of reading, parasitic capacitance or parasitic resistance may be simply referred to as "capacitance" or "resistance", respectively.

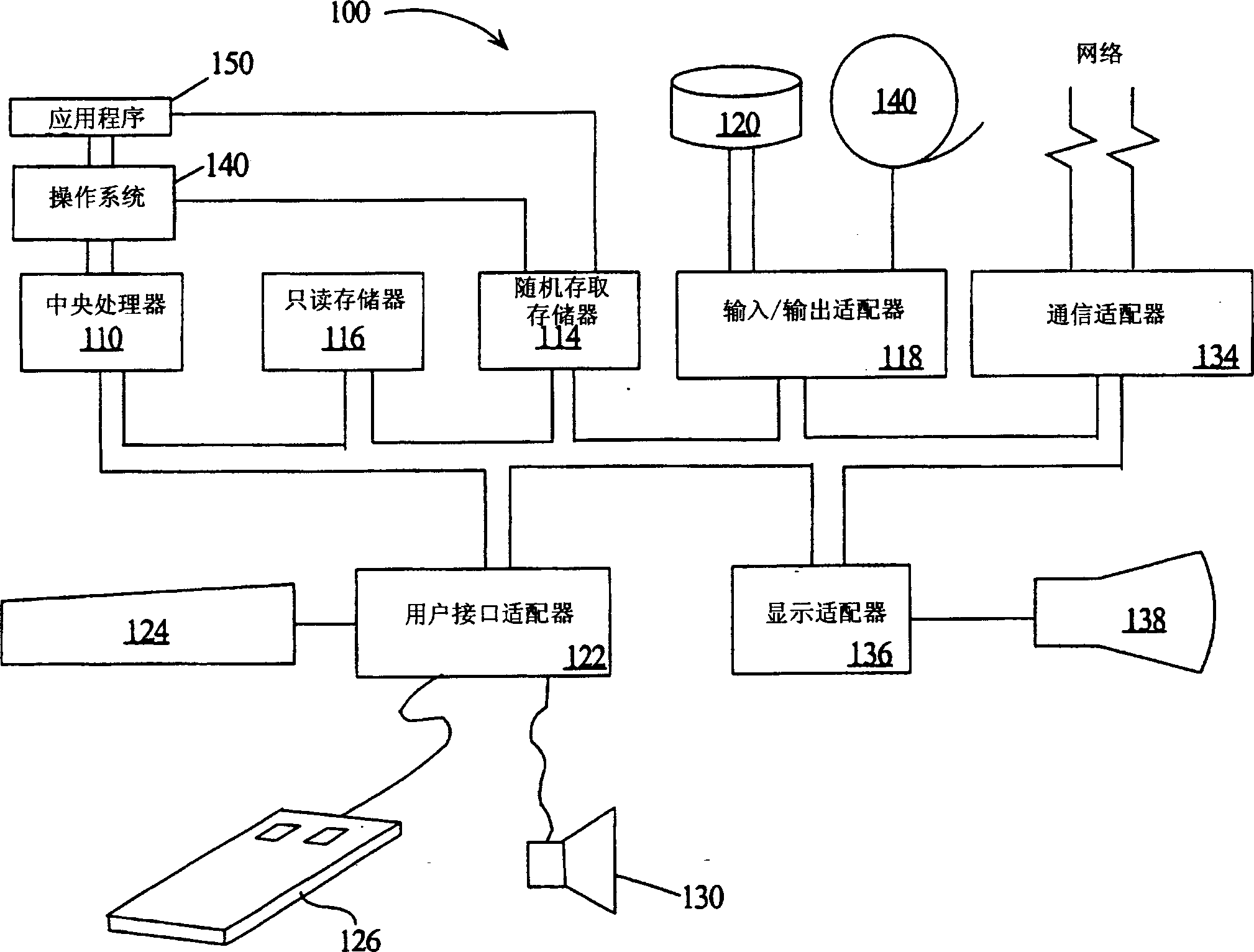

[0016] figure 1 - The hardware configuration of the computer system

[0017] figure 1 A typical hardware configuration of computer system 100, such as a workstation, is identified, representing a hardware environment in ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More