Semiconductor device

A semiconductor and device technology, applied in the field of semiconductor devices, can solve problems such as interlayer peeling of thermal expansion rate of insulating layer and adhesive layer or increase in manufacturing cost, poor bonding wire connection, inevitable hollow state, etc., to achieve suppression of cracks or Bonding failure, thin profile, excellent reliability, and the effect of suppressing connection failure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] Hereinafter, modes for implementing the present invention will be described with reference to the drawings. In addition, although embodiment of this invention is described based on drawings below, these drawings are provided for illustration, and this invention is not limited to these drawings.

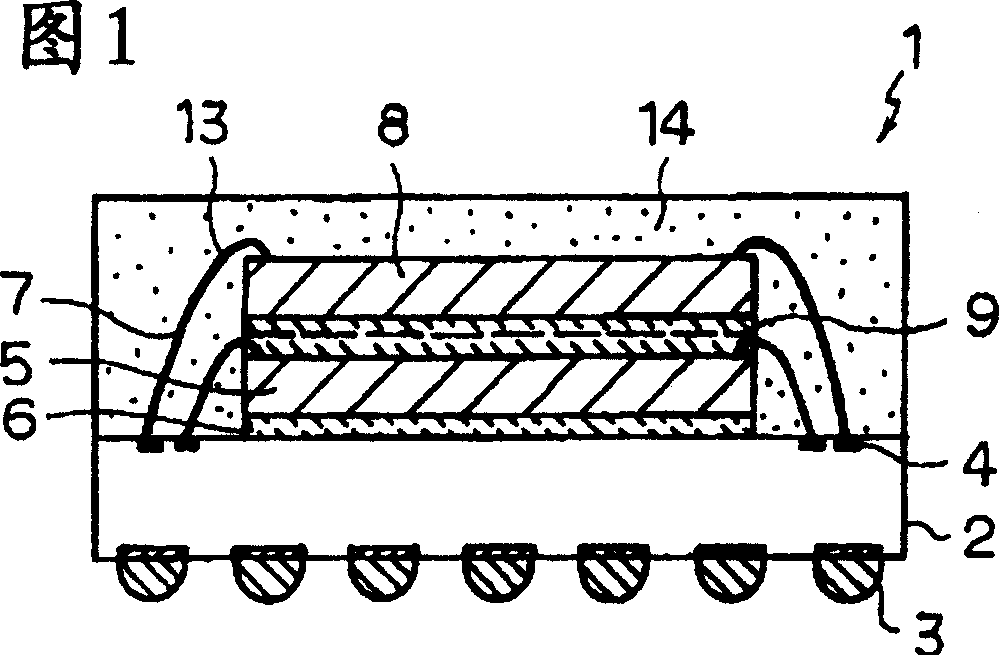

[0054] FIG. 1 is a cross-sectional view showing a schematic configuration of a semiconductor device according to a first embodiment of the present invention. A semiconductor device (semiconductor package) 1 shown in the figure has a circuit board 2 as an element mounting substrate. As the circuit board 2 , a substrate made of various materials such as a resin substrate, a ceramic substrate, and a glass substrate can be used. As the resin substrate, a common multilayer copper-clad laminate (multilayer printed wiring board) or the like is used. On the lower surface side of the circuit board 2, external connection terminals 3 such as solder bumps are formed. In addition, on the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com