Isolation spacer for thin isolation semiconductor

A technology of semiconductors and components, applied in the field of microelectronic components with thin insulating semiconductor structures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The following discussion provides quite a few embodiments or examples to incorporate different features in different embodiments. Specific examples of components and arrangements are described below to simplify the disclosure. Therefore, mere few examples should not be considered limiting. Additionally, the same notation and text may be used in different instances throughout the disclosure. Reuse of symbols and text is for simplification and clarity only and does not dictate relationships between different embodiments and / or discussion outlines.

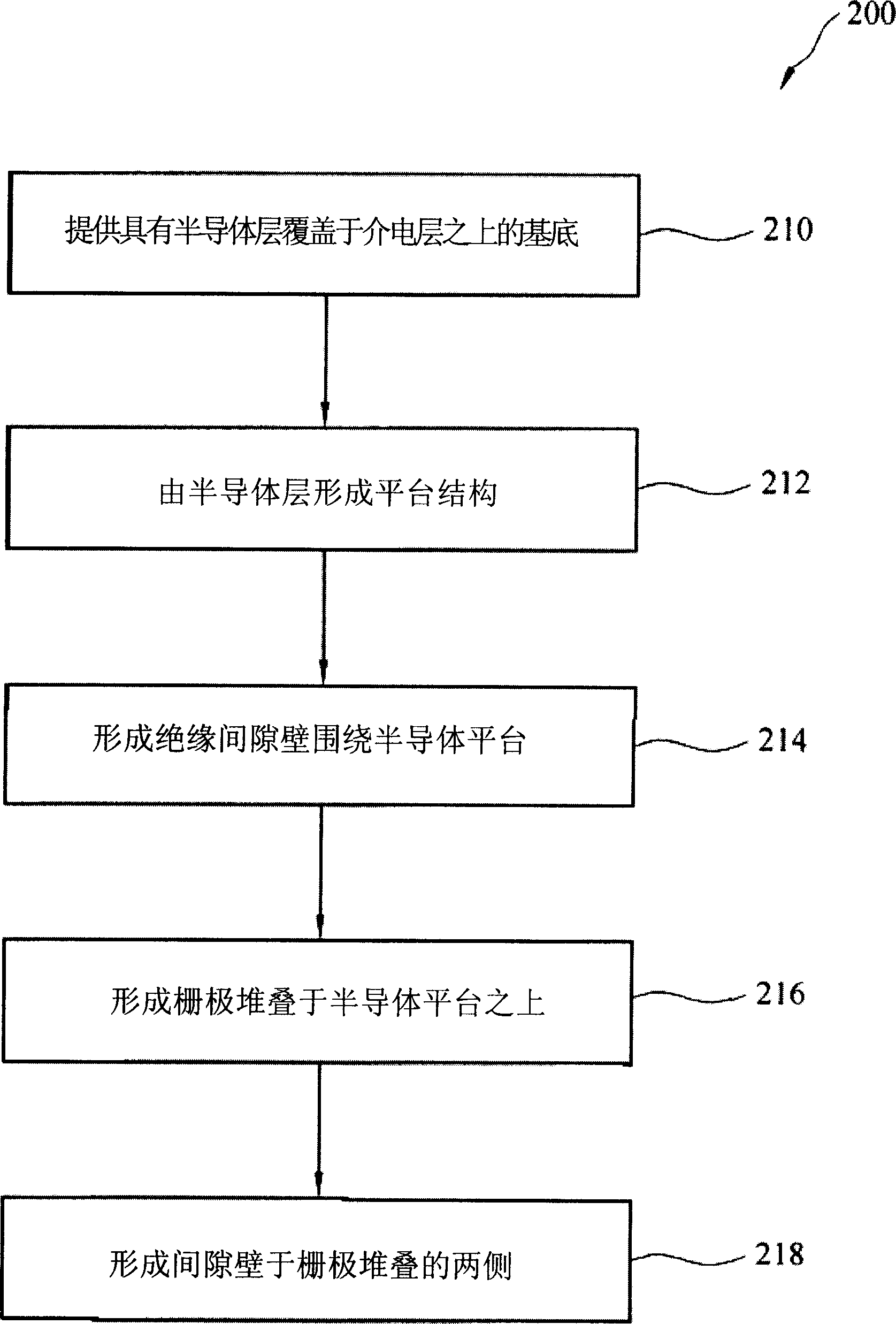

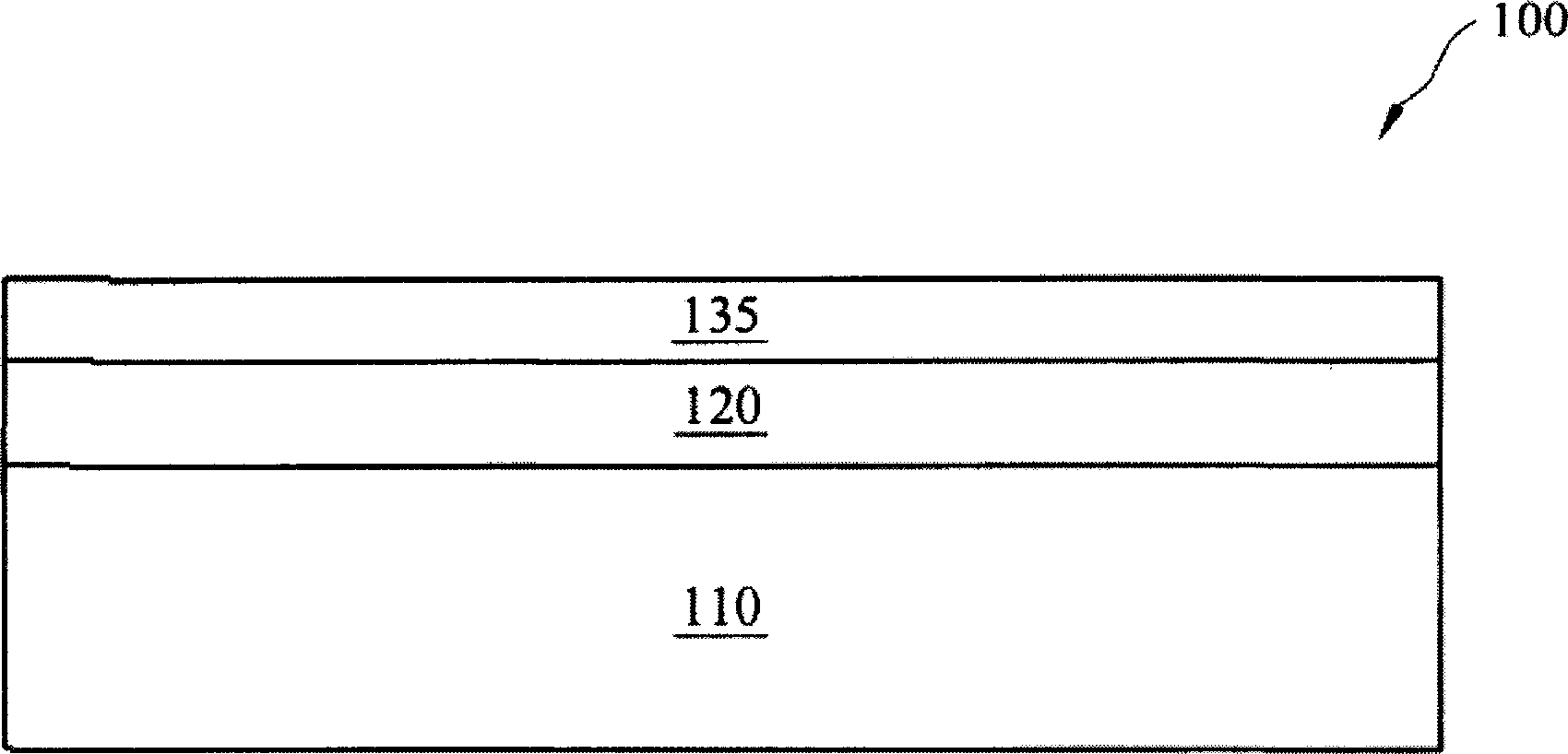

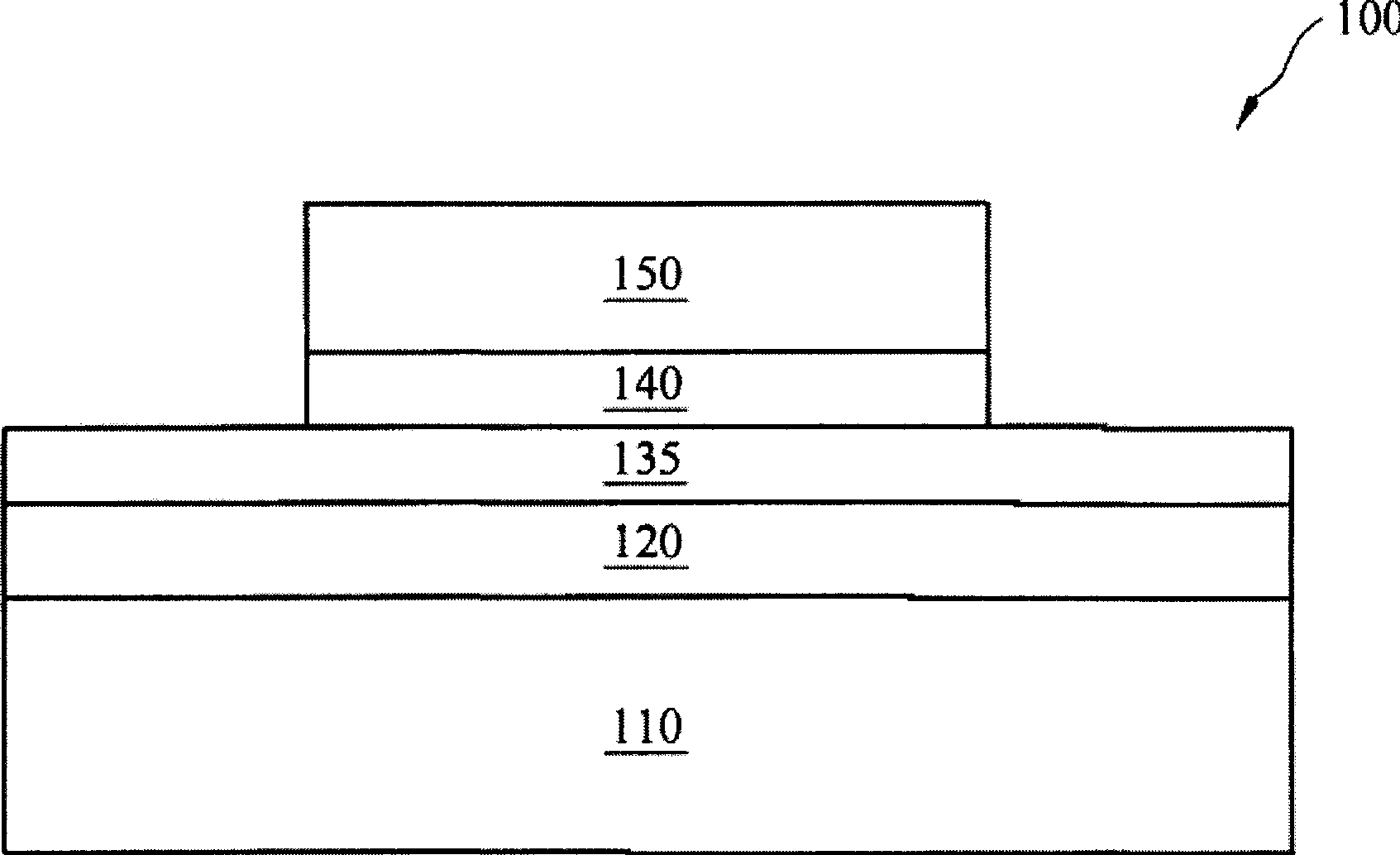

[0034] figure 1 is a simplified flowchart of the method 200 for forming a thin insulating semiconductor device. and Figure 2 to Figure 7a and 7b are schematic cross-sectional views of the process of forming the semiconductor device 100 .

[0035] Method 200 starts from step 210, first provides as figure 2 A semiconductor substrate 110 is shown, a dielectric layer 120 is formed on the substrate 110 , and a semiconductor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More