Apparatus and method for verificating chip standard coincidence degree

A verification method and verification equipment technology, which is applied in the field of chip standard compliance verification equipment, can solve problems such as error-prone, high manpower input costs, and normal failure to be guaranteed, and achieve high input and output effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

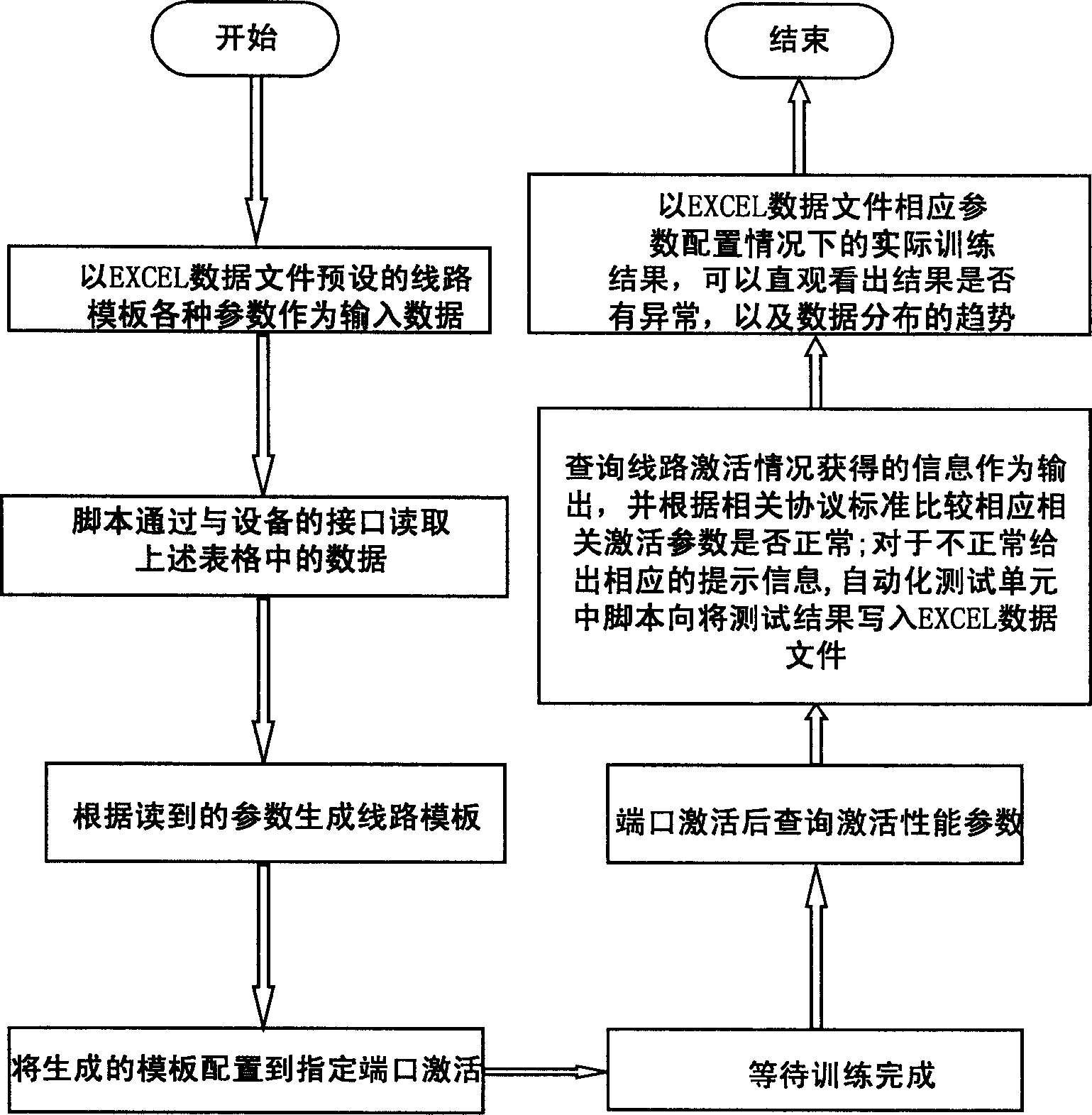

[0034] A chip standard compliance verification device and method of the present invention will be further described in detail below in conjunction with the accompanying drawings.

[0035] A kind of chip standard conformity verification equipment and method of the present embodiment is particularly described with ADSL2+, ADSL chip standard conformity verification equipment and method, but the present invention is equally applicable except the chip standard mentioned above The case of communicating with any other communication chip standards.

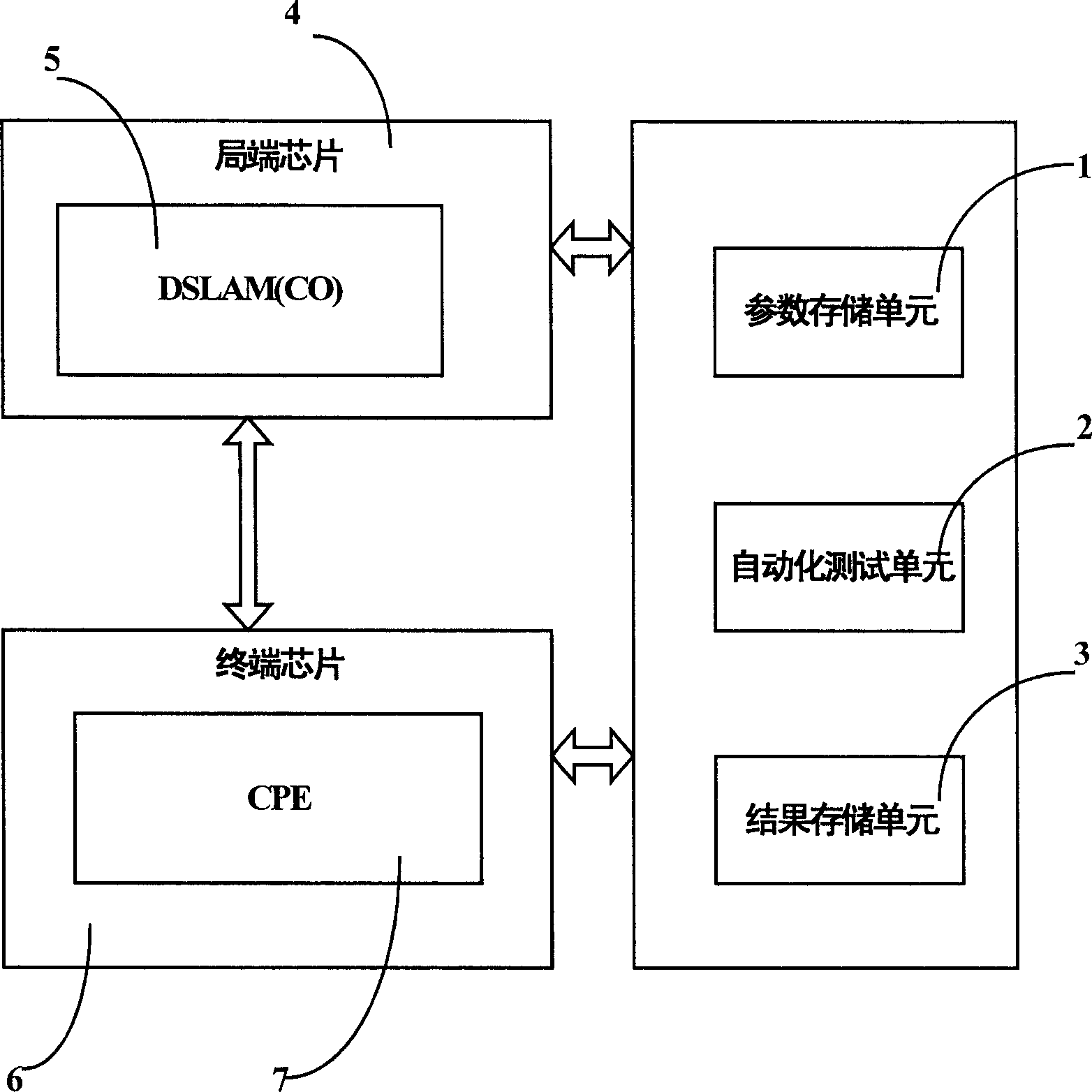

[0036] The chip standard seat verification device of the present invention includes a parameter storage unit 1 , an automatic test unit 2 and a result storage unit 3 .

[0037] The parameter storage unit 1 is used to store various parameters of the line template, including the hardware configuration environment and software configuration environment parameters required for functional verification, and for the functional verification of di...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com