Patents

Literature

35 results about "Port performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

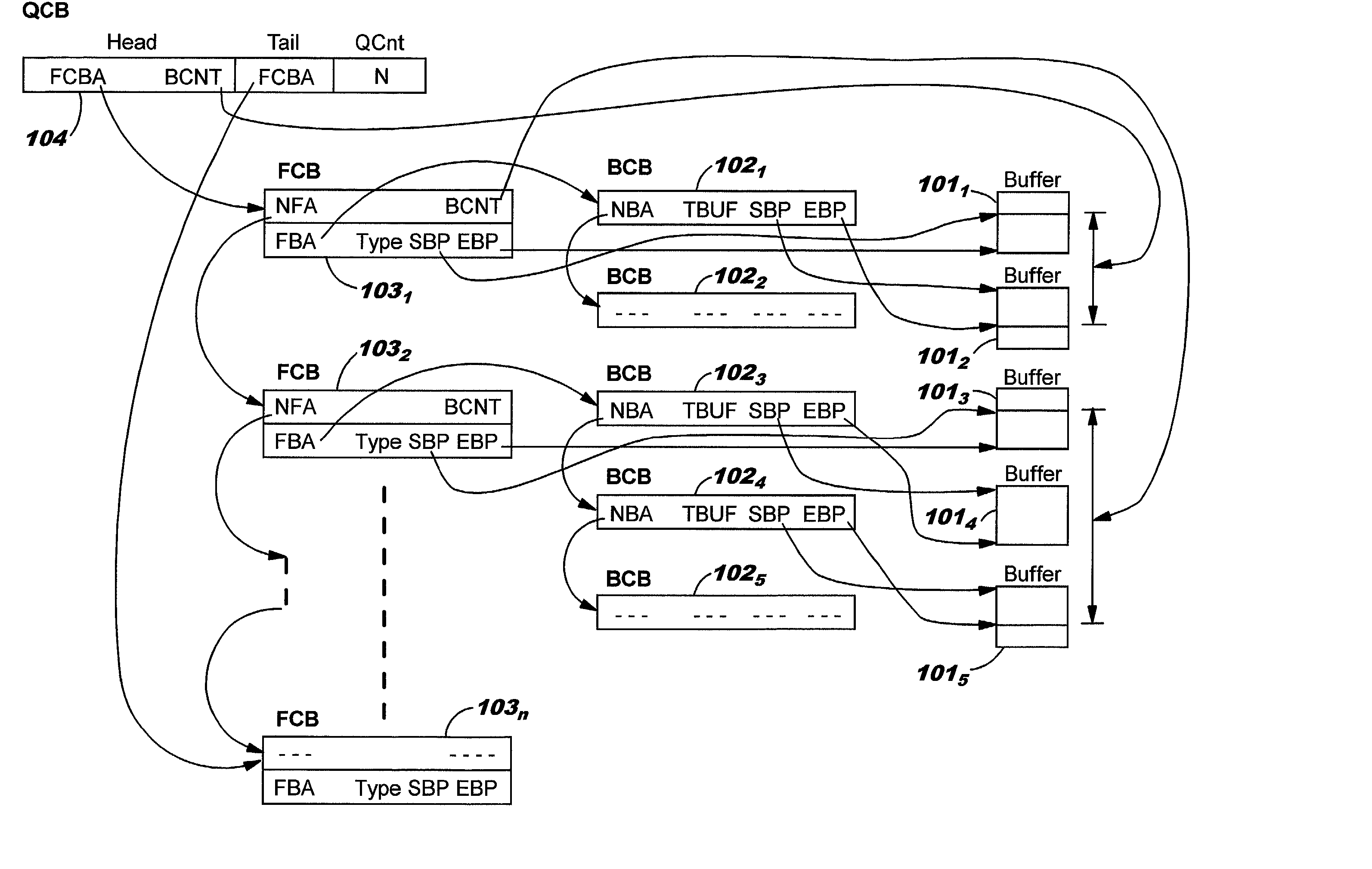

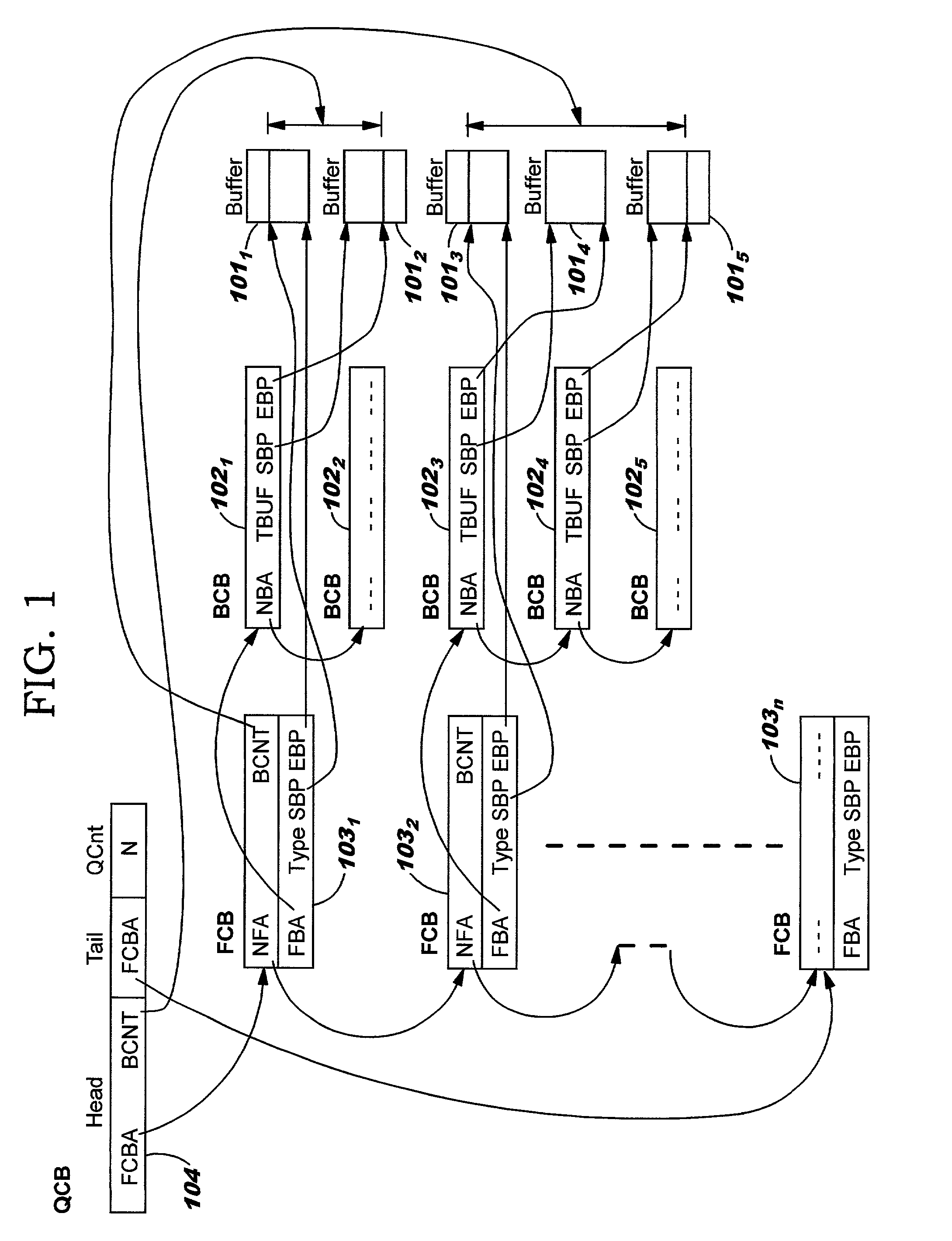

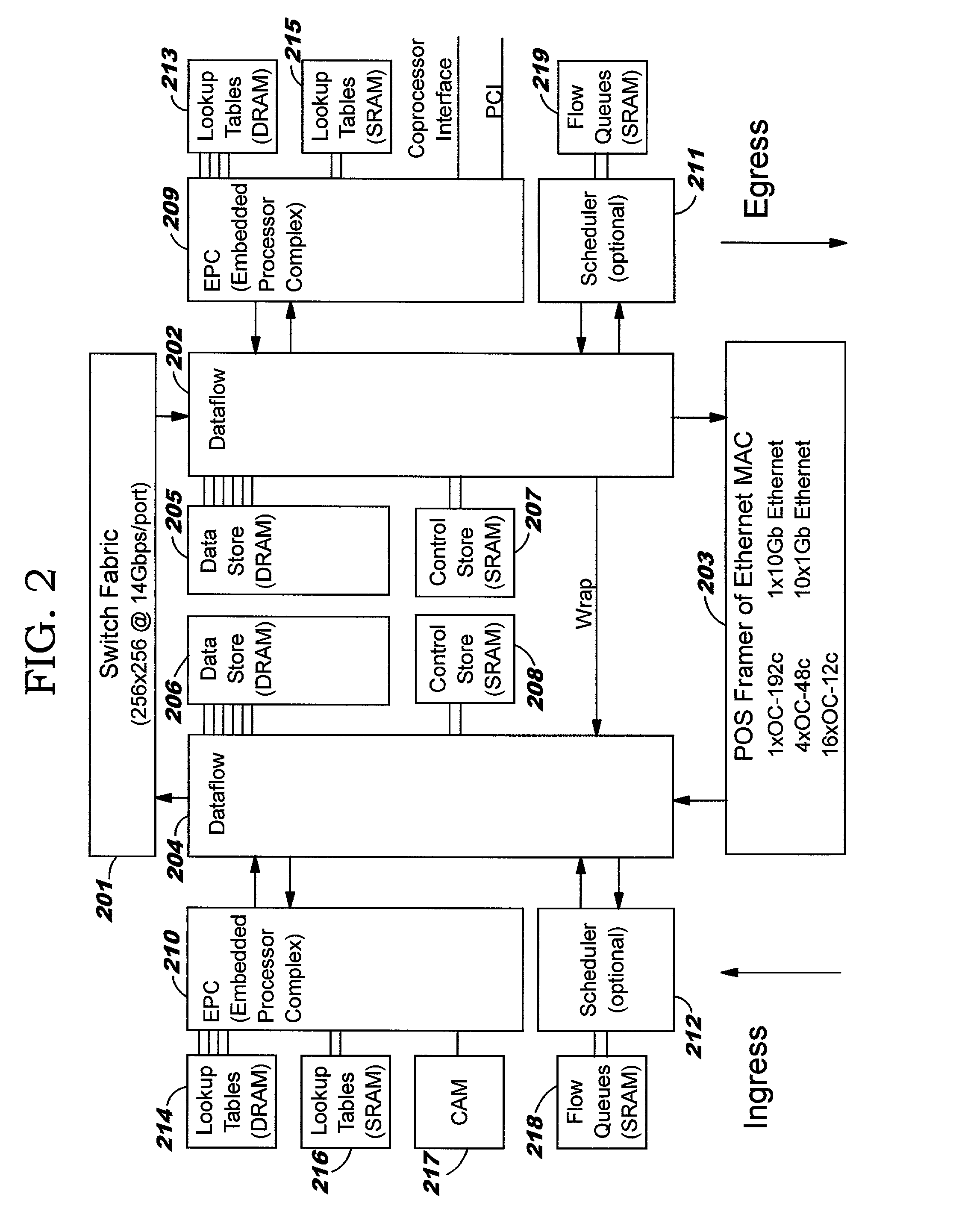

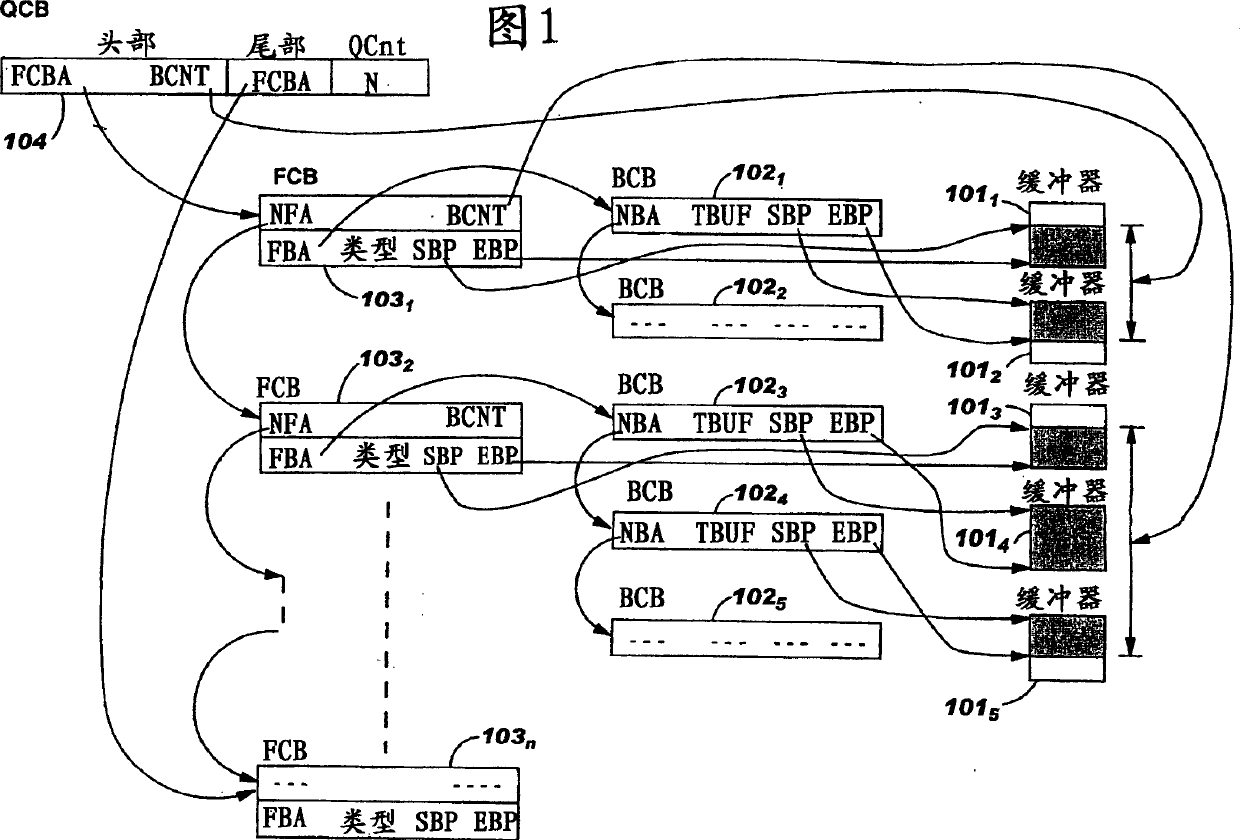

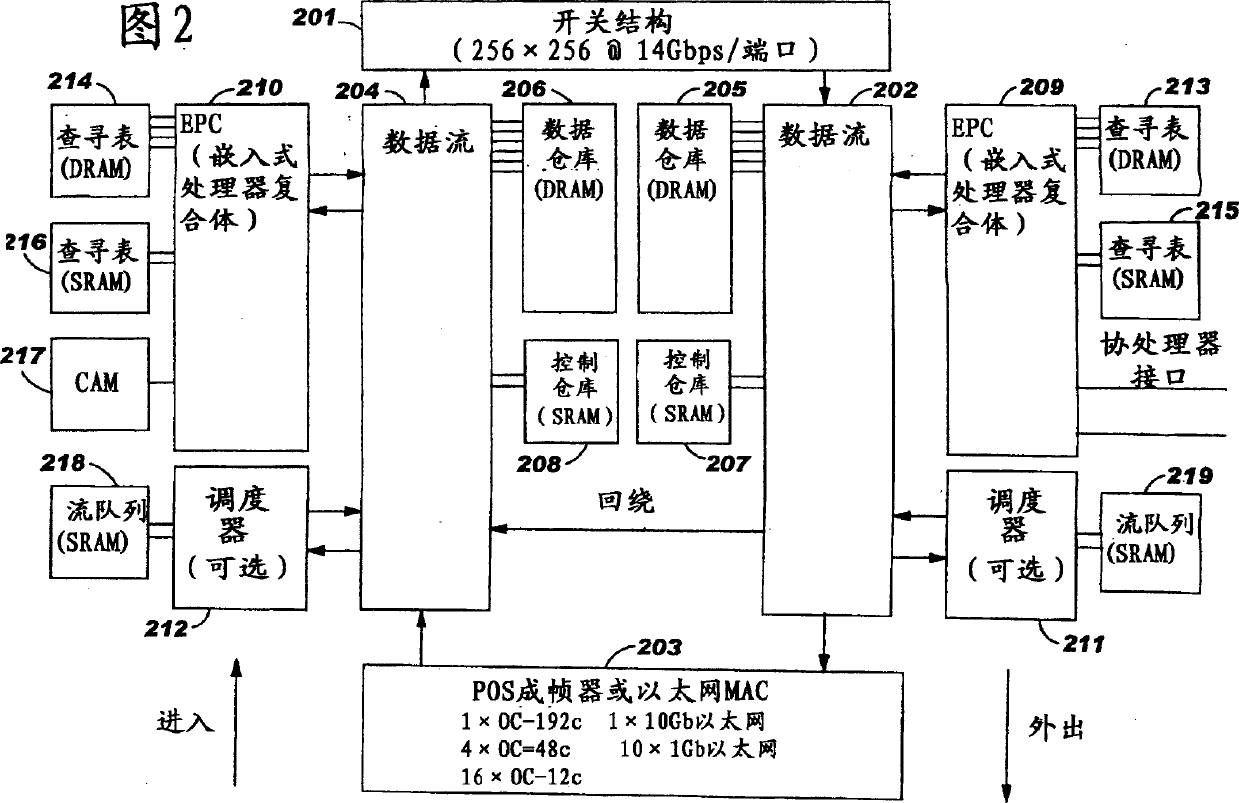

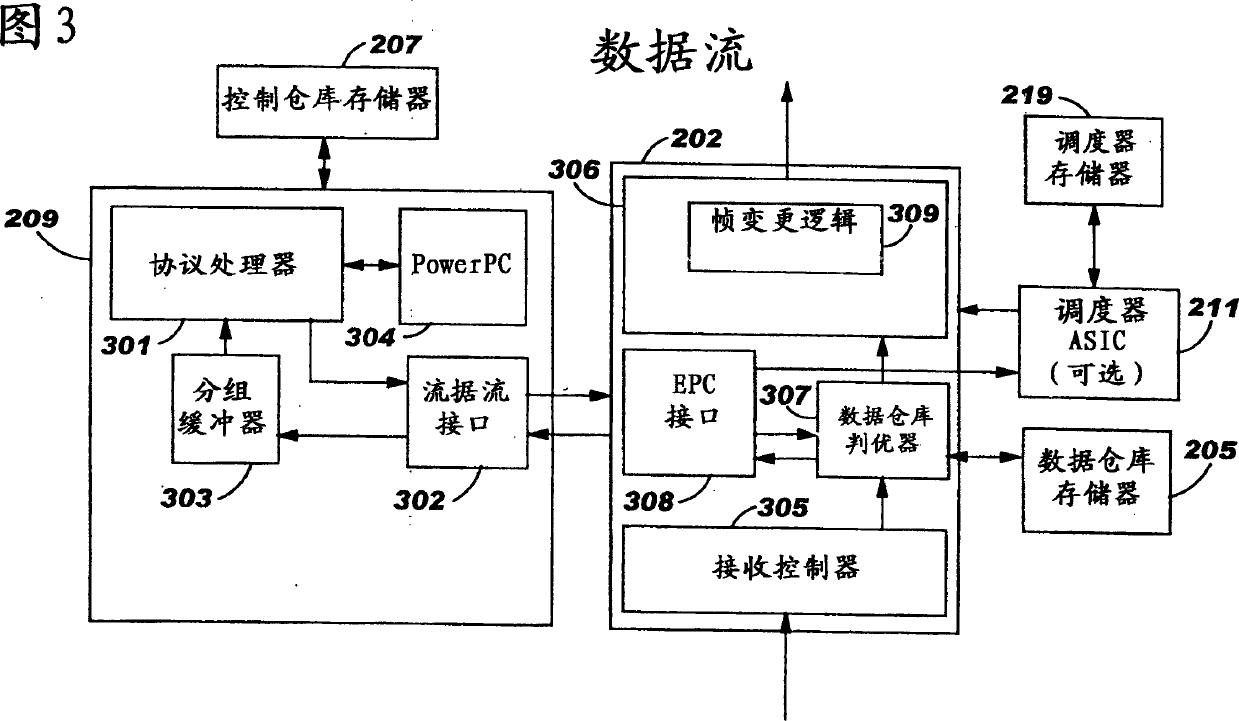

Data structures for efficient processing of multicast transmissions

InactiveUS6836480B2Reduce memory requirementsEliminate needSpecial service provision for substationTime-division multiplexArray data structureTransport system

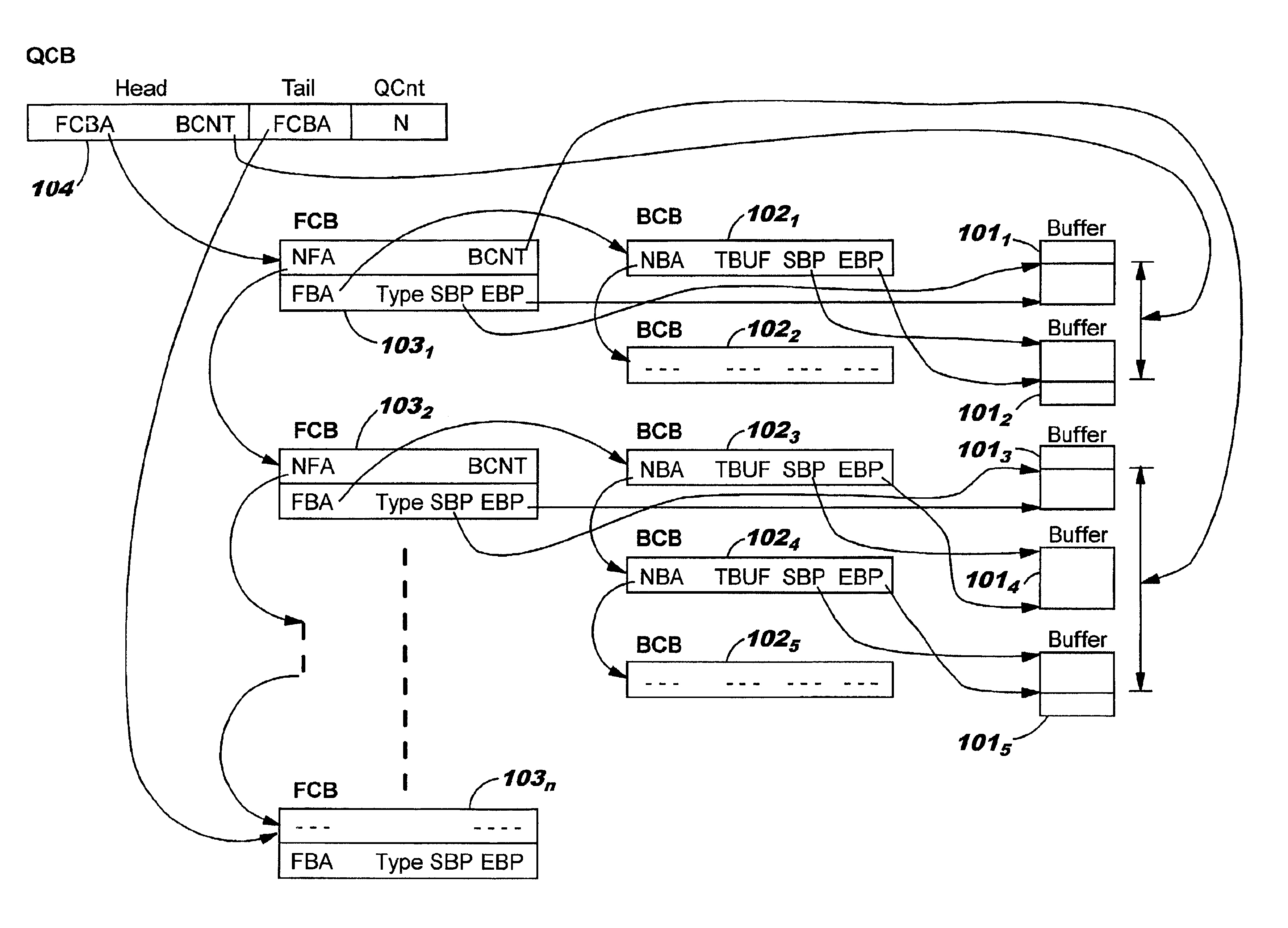

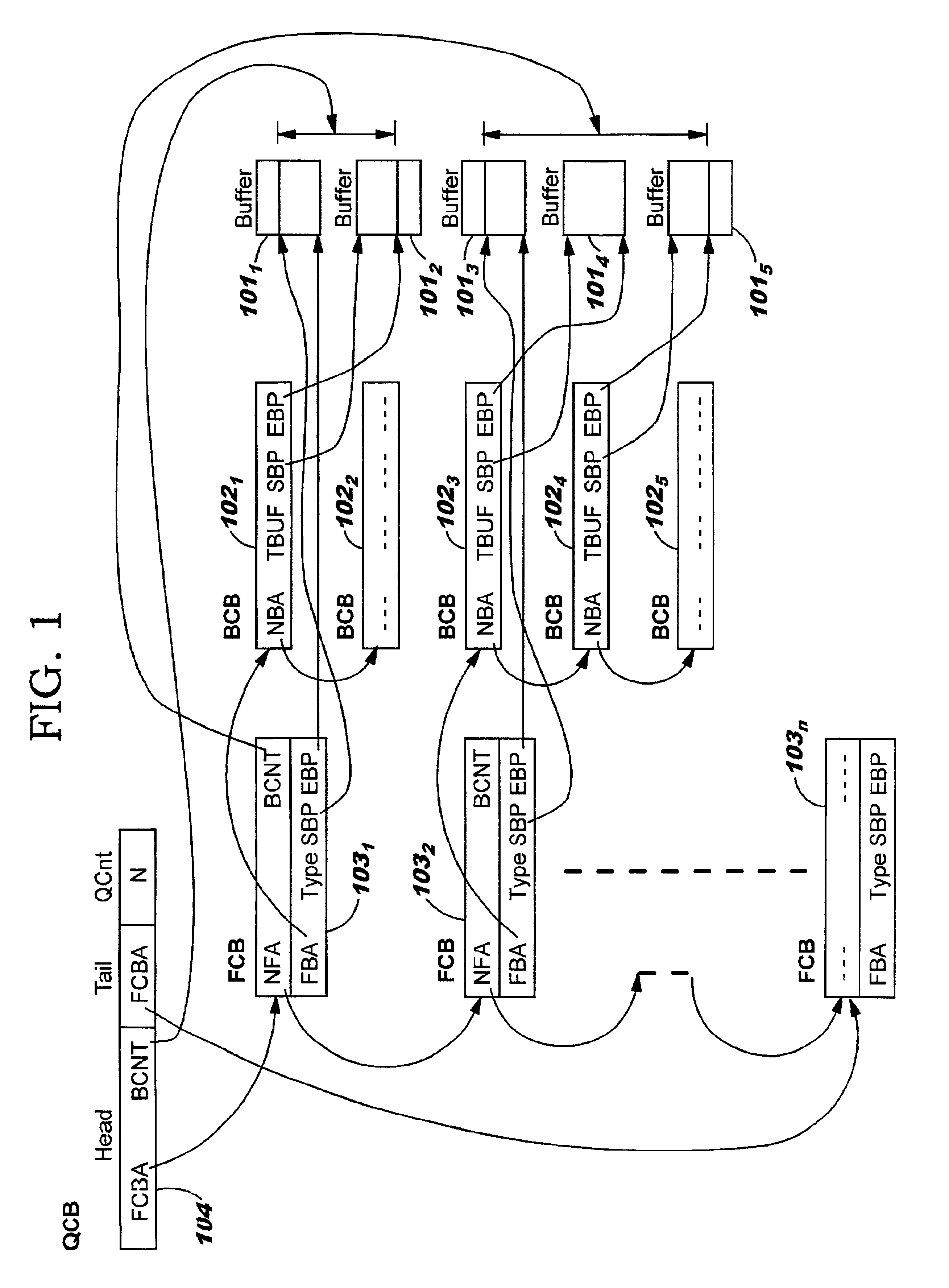

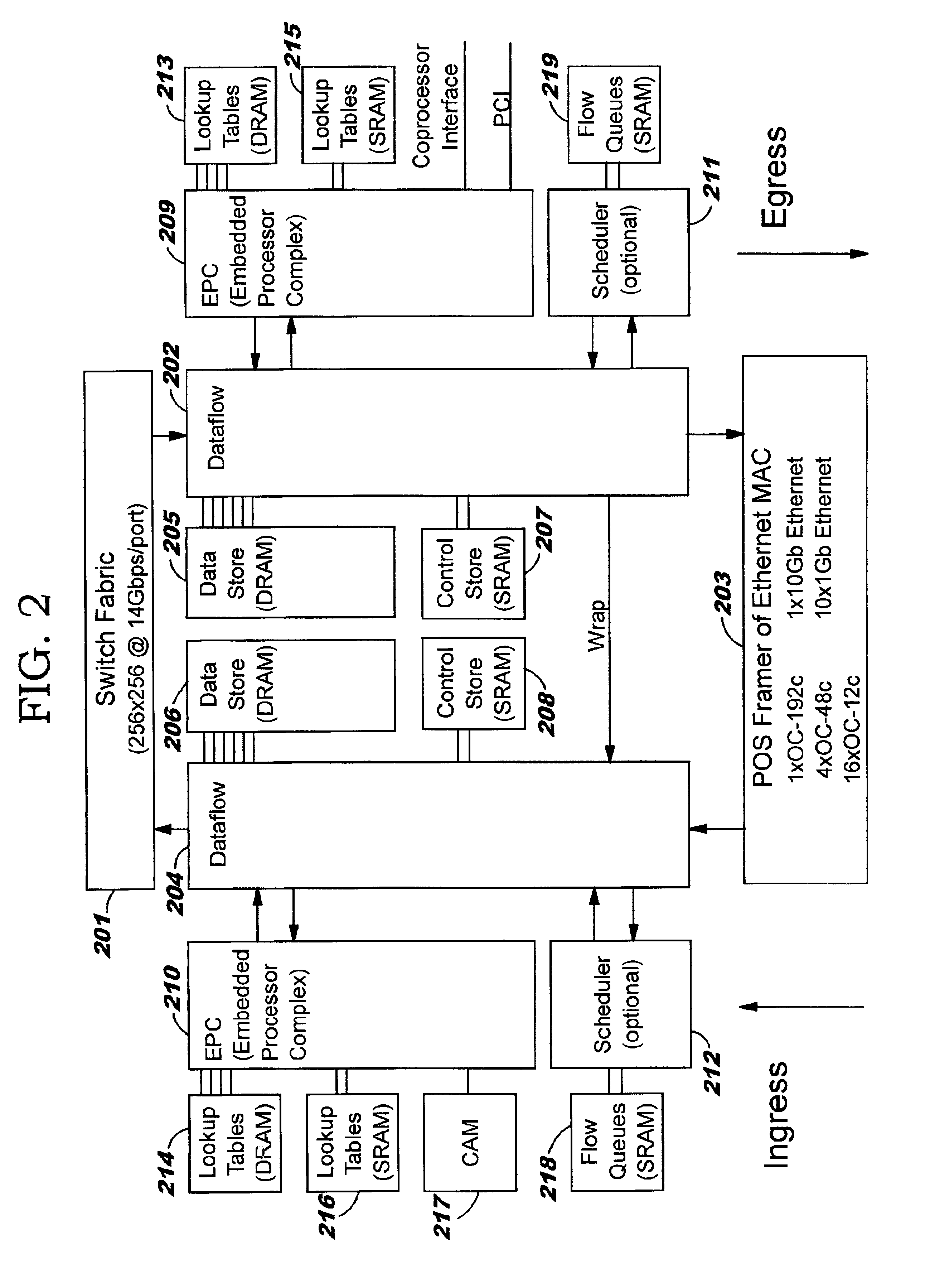

Data structures, a method, and an associated transmission system for multicast transmission on network processors in order both to minimize multicast transmission memory requirements and to account for port performance discrepancies. Frame data for multicast transmission on a network processor is read into buffers to which are associated various control structures and a reference frame. The reference frame and the associated control structures permit multicast targets to be serviced without creating multiple copies of the frame. Furthermore this same reference frame and control structures allow buffers allocated for each multicast target to be returned to the free buffer queue without waiting until all multicast transmissions are complete.

Owner:ACTIVISION PUBLISHING

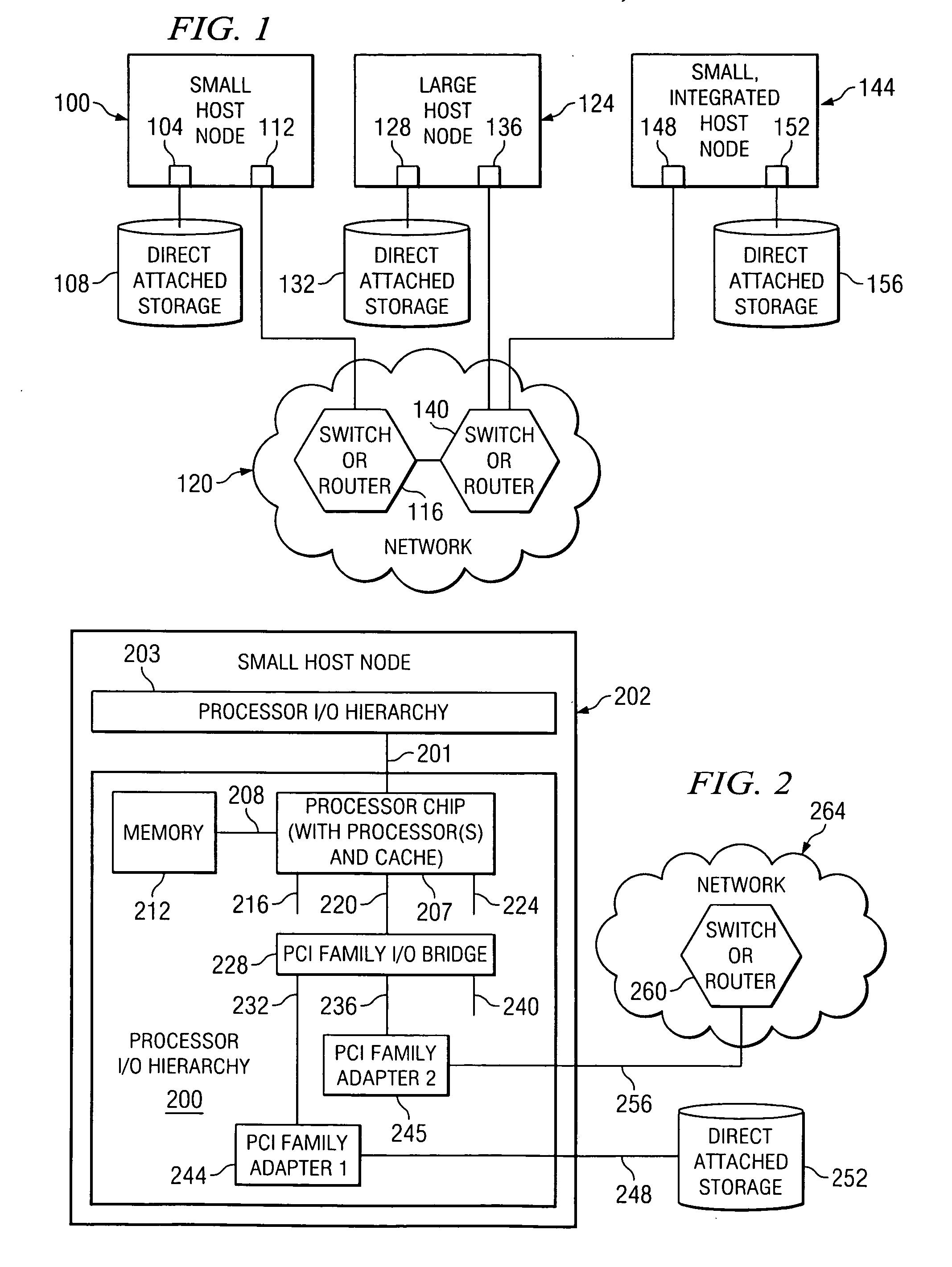

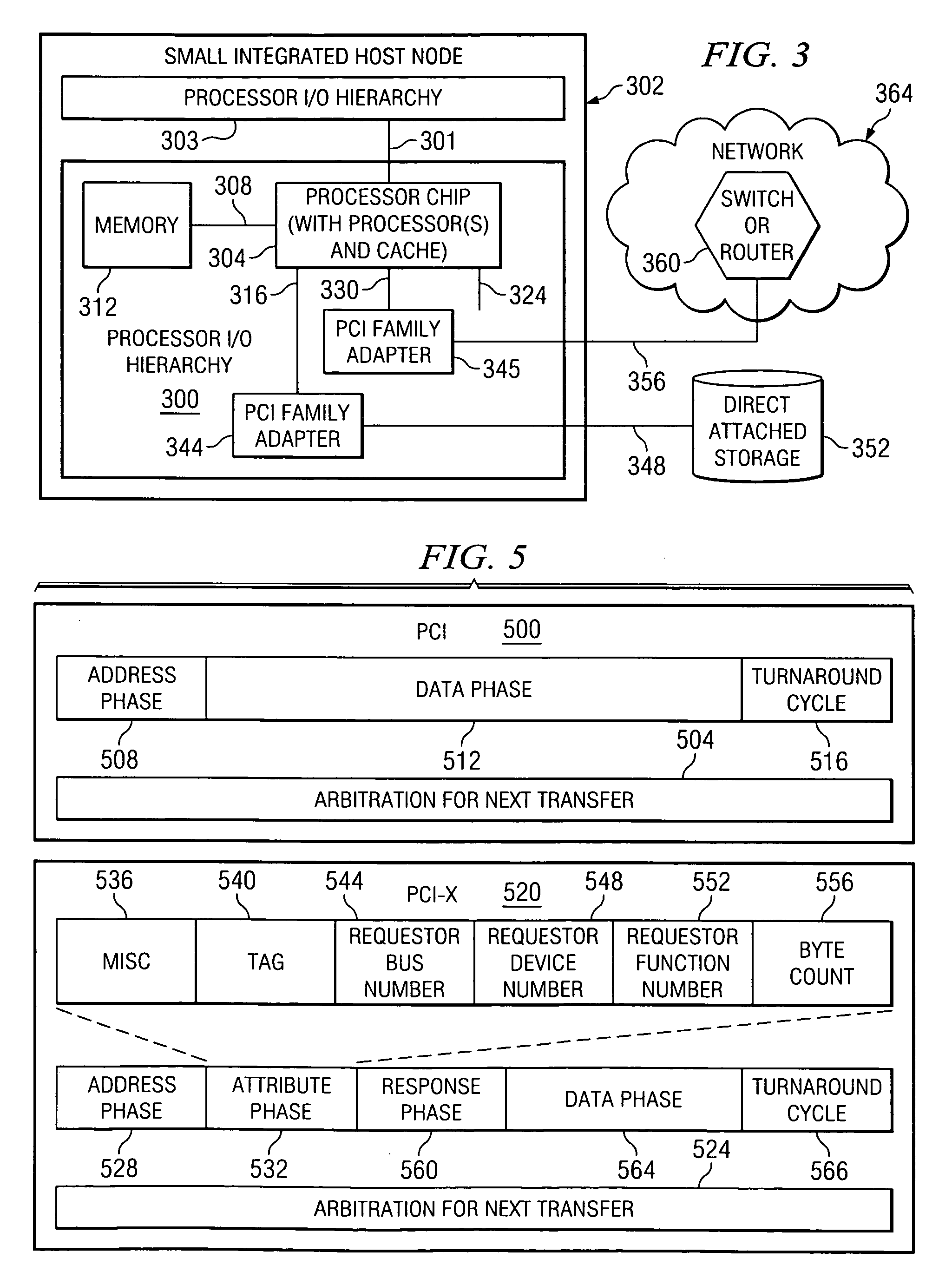

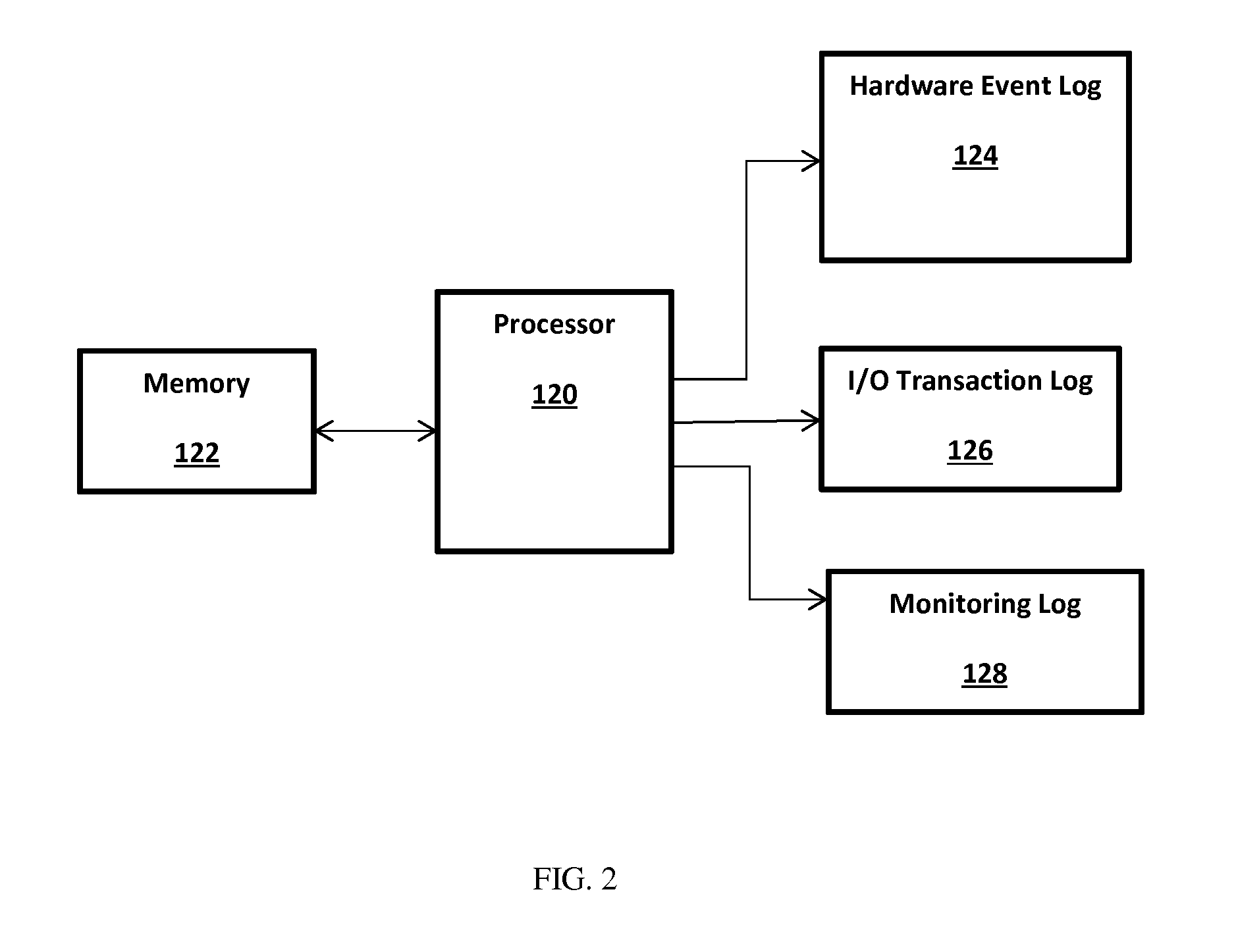

System and method for managing metrics table per virtual port in a logically partitioned data processing system

InactiveUS7308551B2Fine granularityDigital computer detailsMultiprogramming arrangementsData processing systemGranularity

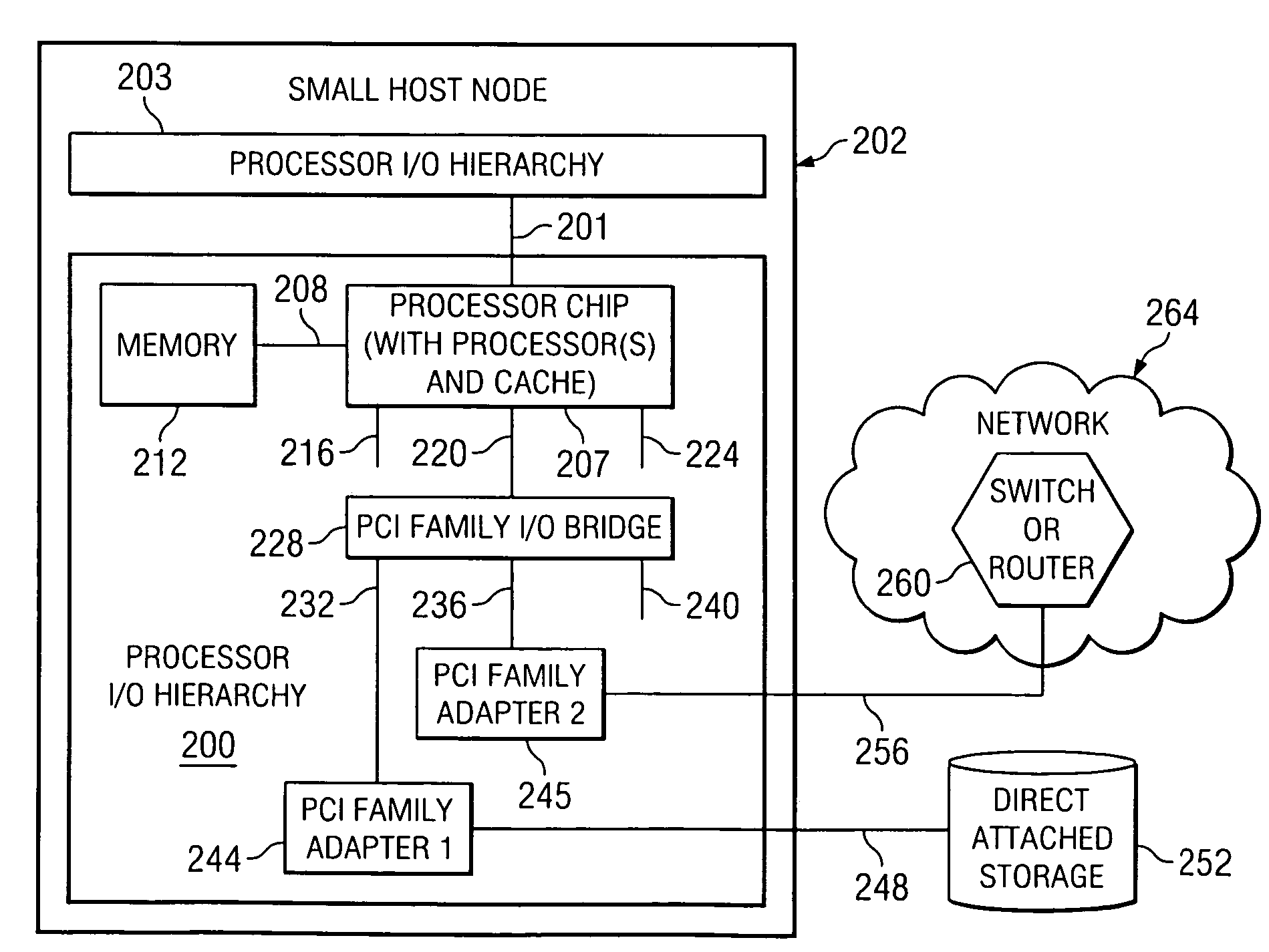

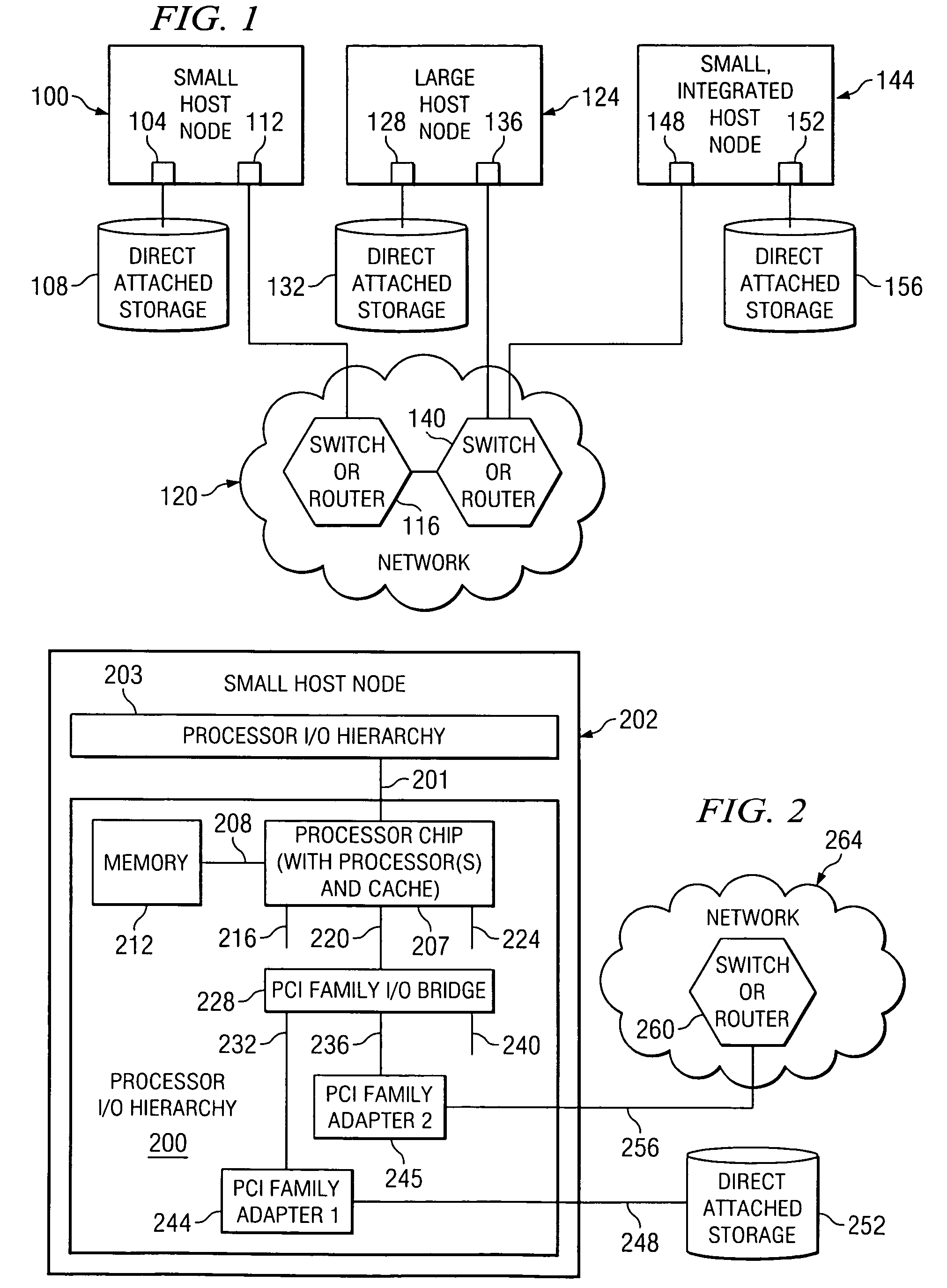

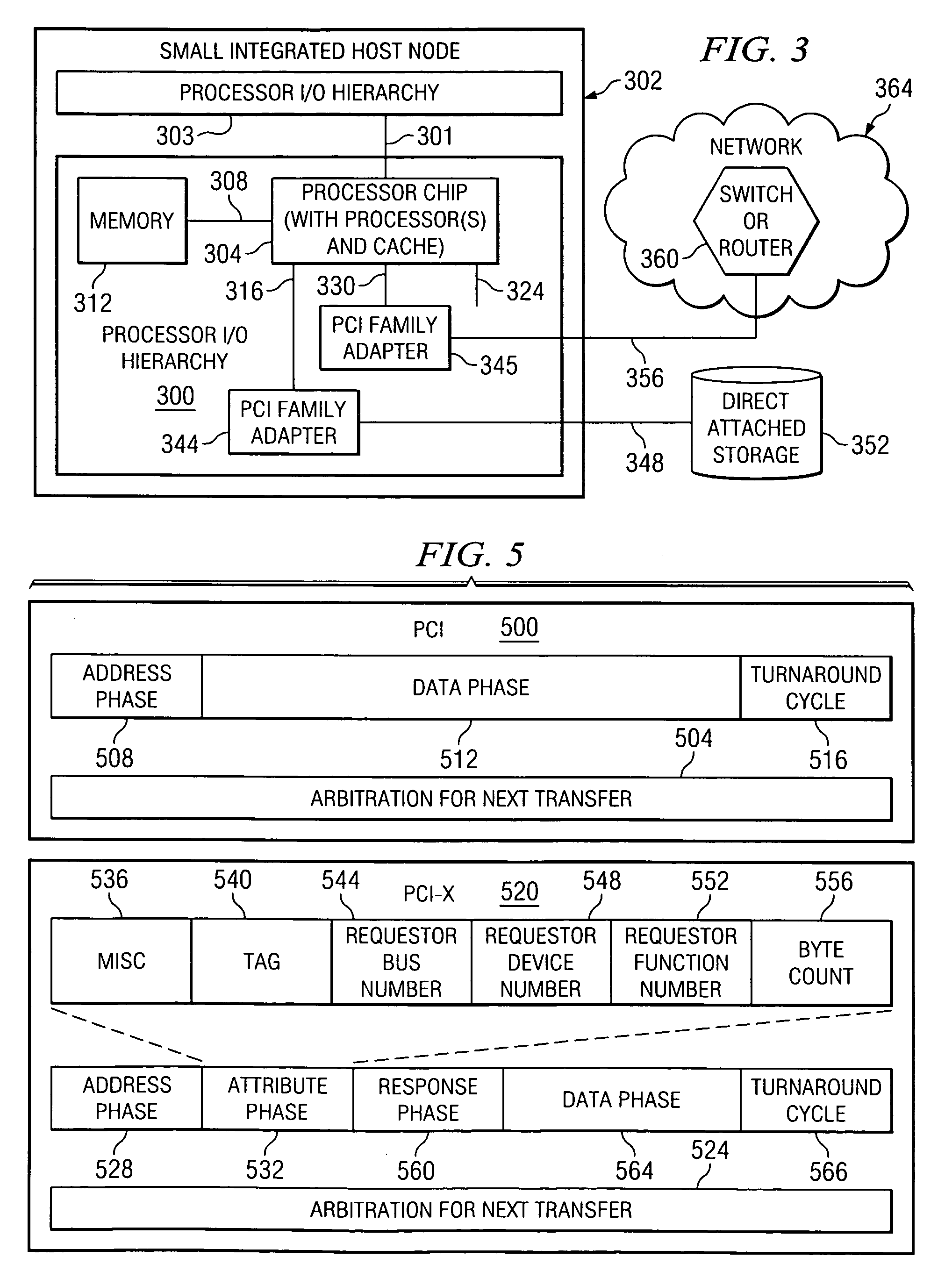

A method, computer program product, and distributed data processing system that allows a single physical I / O adapter, such as a PCI, PCI-X, or PCI-E adapter, to track performance and reliability statistics per virtual upstream and downstream port, thereby allowing a system and network management to be performed at finer granularity than what is possible using conventional physical port statistics, is provided. Particularly, a mechanism of managing per-virtual port performance metrics in a logically partitioned data processing system including allocating a subset of resources of a physical adapter to a virtual adapter of a plurality of virtual adapters is provided. The subset of resources includes a virtual port having an identifier assigned thereto. The identifier of the virtual port is associated with an address of a physical port. A metric table is associated with the virtual port, wherein the metric table includes metrics of operations that target the virtual port.

Owner:IBM CORP

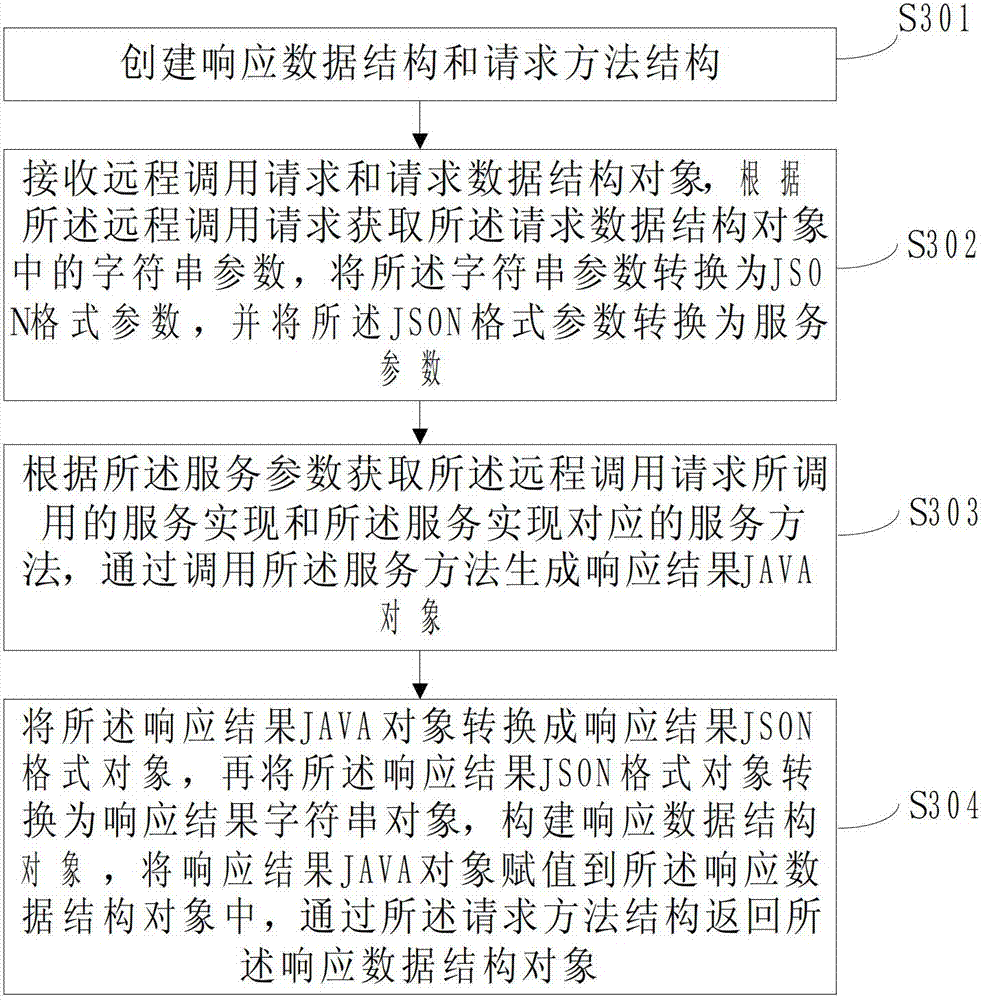

JAVA object requesting and responding methods, devices and systems and terminal

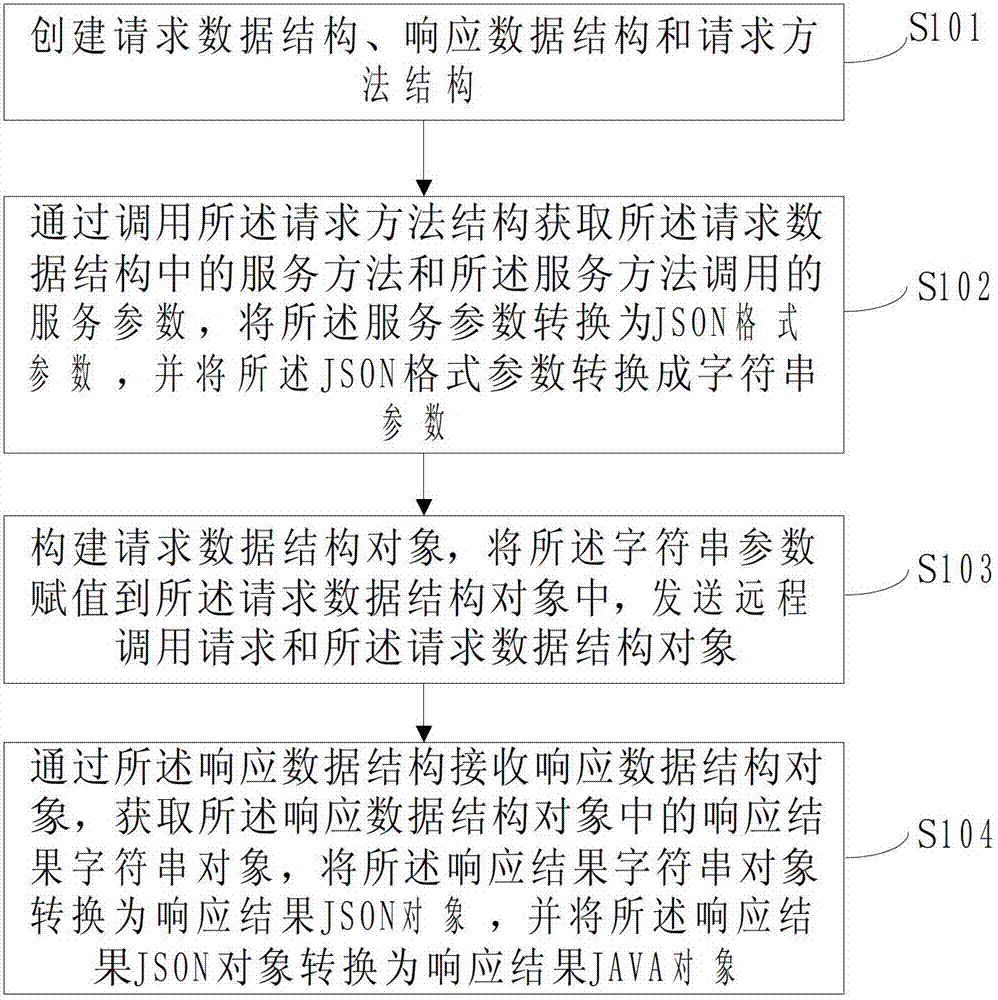

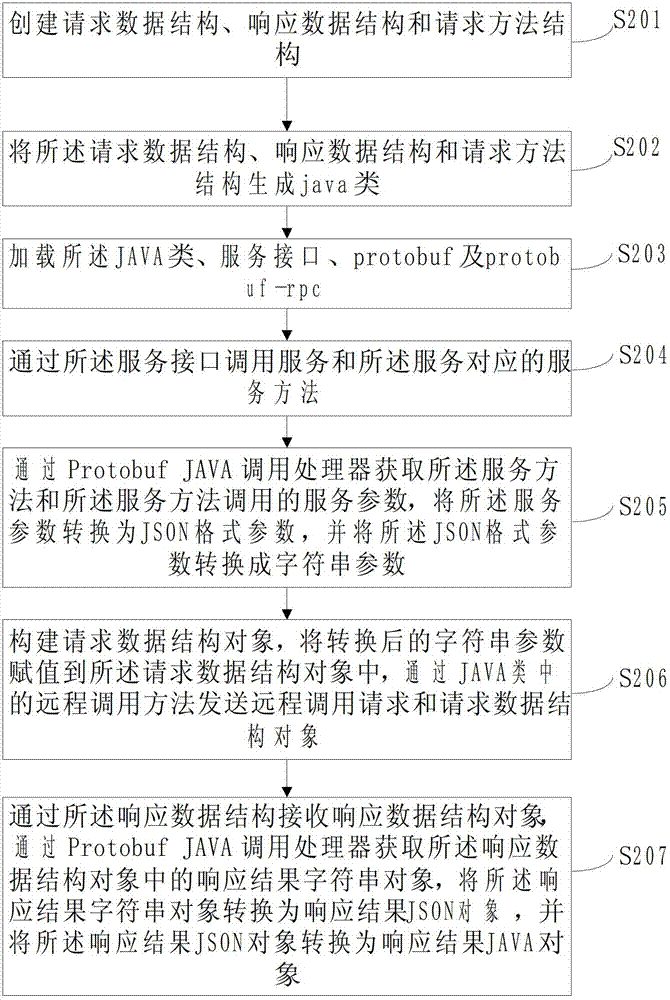

InactiveCN102810069AImprove interface performanceImprove functional requirementsMultiprogramming arrangementsJSONBusiness logic

The invention discloses JAVA object requesting and responding methods, devices and systems, and a terminal. The requesting method comprises the steps of creating a request data structure, a response data structure and a request method structure, invoking the request method structure to obtain a service method in the request data structure and service parameters invoked by the service method, sequentially converting the service parameters into parameters in a JSON (Javascript Serialized Object Notation) format and character string parameters, constructing a request data structure object, assigning the converted character string parameters into the request data structure object, receiving a response data structure object through the response data structure, obtaining response result character string objects in the response data structure object, and sequentially converting the response result character string objects into response result JSON objects and response result JAVA objects. The purpose of invoking the JAVA objects remotely is realized, port service of the original RMI (Remote Method Invocation) can be replaced, the service logic does not need to be modified, and the port performance is improved.

Owner:融创天下(上海)科技发展有限公司

Data structures for efficient processing of multicast transmissions

InactiveUS20020154634A1Reduce memory requirementsEliminate needSpecial service provision for substationTime-division multiplexArray data structureTransport system

Data structures, a method, and an associated transmission system for multicast transmission on network processors in order both to minimize multicast transmission memory requirements and to account for port performance discrepancies. Frame data for multicast transmission on a network processor is read into buffers to which are associated various control structures and a reference frame. The reference frame and the associated control structures permit multicast targets to be serviced without creating multiple copies of the frame. Furthermore this same reference frame and control structures allow buffers allocated for each multicast target to be returned to the free buffer queue without waiting until all multicast transmissions are complete.

Owner:ACTIVISION PUBLISHING

System and method for managing metrics table per virtual port in a logically partitioned data processing system

InactiveUS20060195674A1Fine granularityDigital computer detailsSoftware simulation/interpretation/emulationData processing systemGranularity

A method, computer program product, and distributed data processing system that allows a single physical I / O adapter, such as a PCI, PCI-X, or PCI-E adapter, to track performance and reliability statistics per virtual upstream and downstream port, thereby allowing a system and network management to be performed at finer granularity than what is possible using conventional physical port statistics, is provided. Particularly, a mechanism of managing per-virtual port performance metrics in a logically partitioned data processing system including allocating a subset of resources of a physical adapter to a virtual adapter of a plurality of virtual adapters is provided. The subset of resources includes a virtual port having an identifier assigned thereto. The identifier of the virtual port is associated with an address of a physical port. A metric table is associated with the virtual port, wherein the metric table includes metrics of operations that target the virtual port.

Owner:IBM CORP

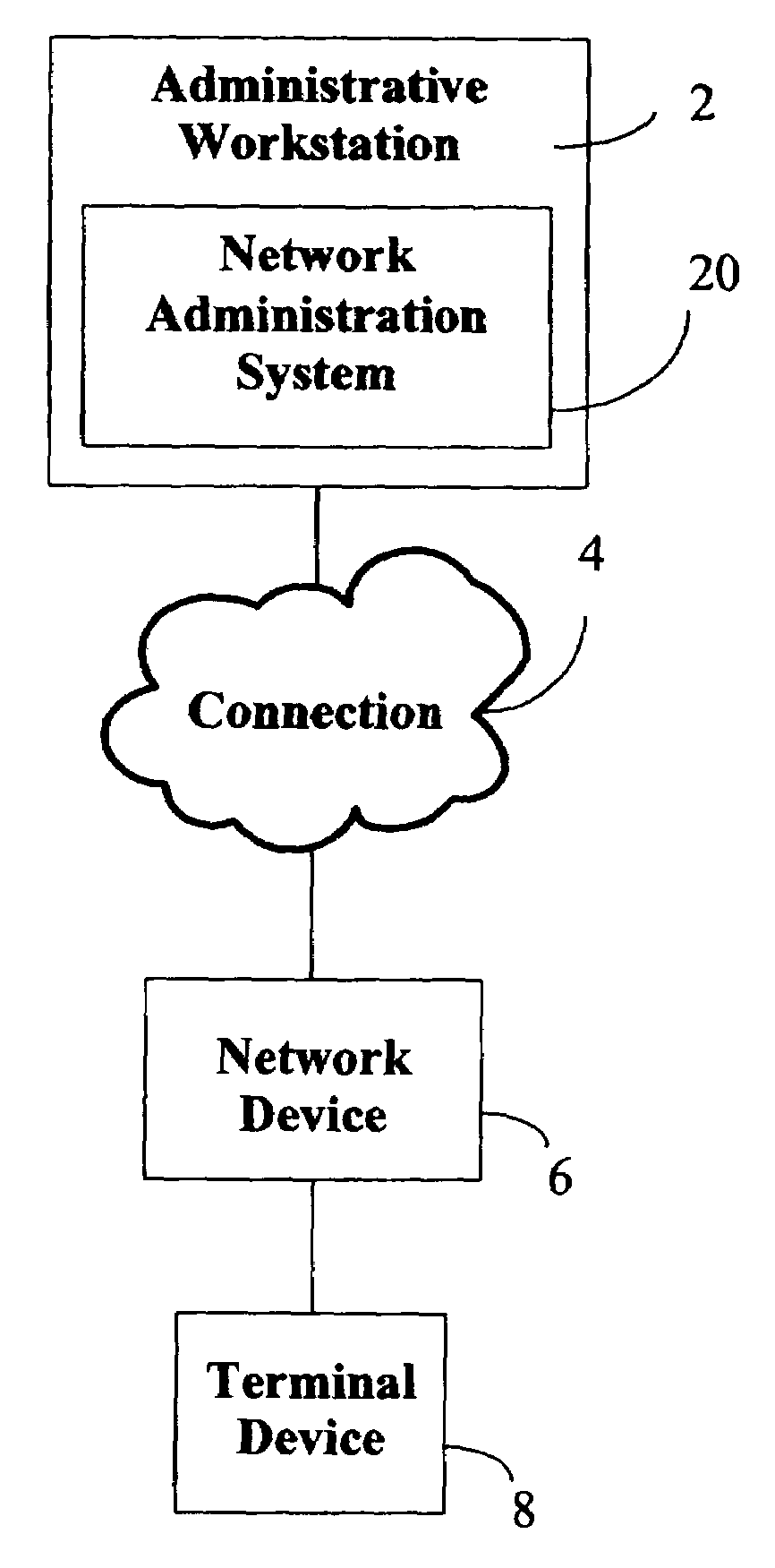

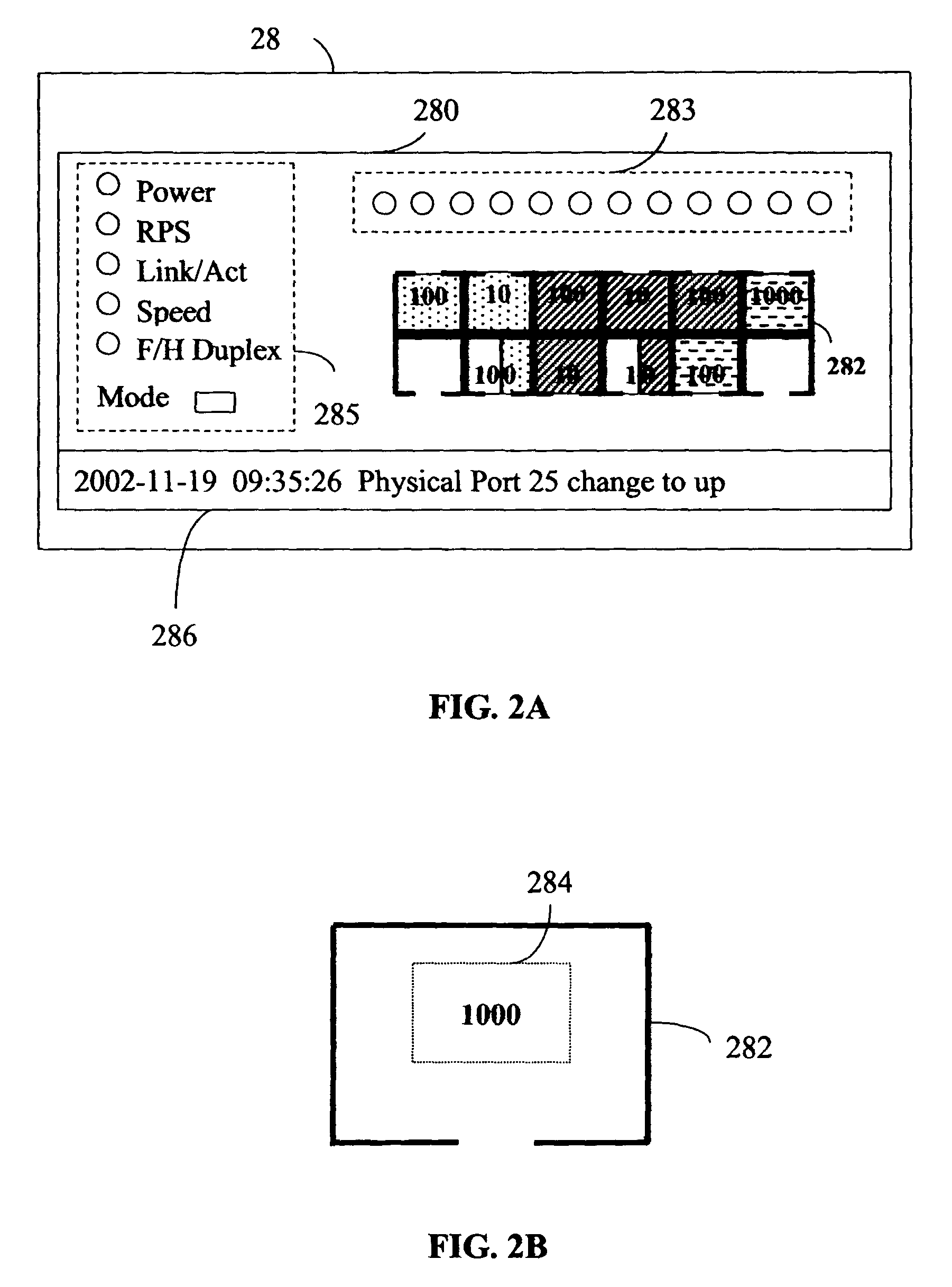

Port information display system and method for displaying port performance of network devices

A system and method for displaying port performance of networking devices (6) is provided. The system is implemented in a networking infrastructure which includes an administrative workstation (2) and at least one networking devices. The administrative workstation can obtain and display information on ports of the networking device in real time. A plurality of port information pages (28) formed according to a simulating figure (280) of the networking device are provided by the administrative workstation. The simulating figure is for simulating a front panel of a respective network device and comprises a plurality of port icons (282). The port icon is for displaying traffic volume statuses for corresponding ports respectively with different colors and image configurations. A current event bar (286) is provided for displaying the most up-date event information of the networking device.

Owner:HON HAI PRECISION IND CO LTD

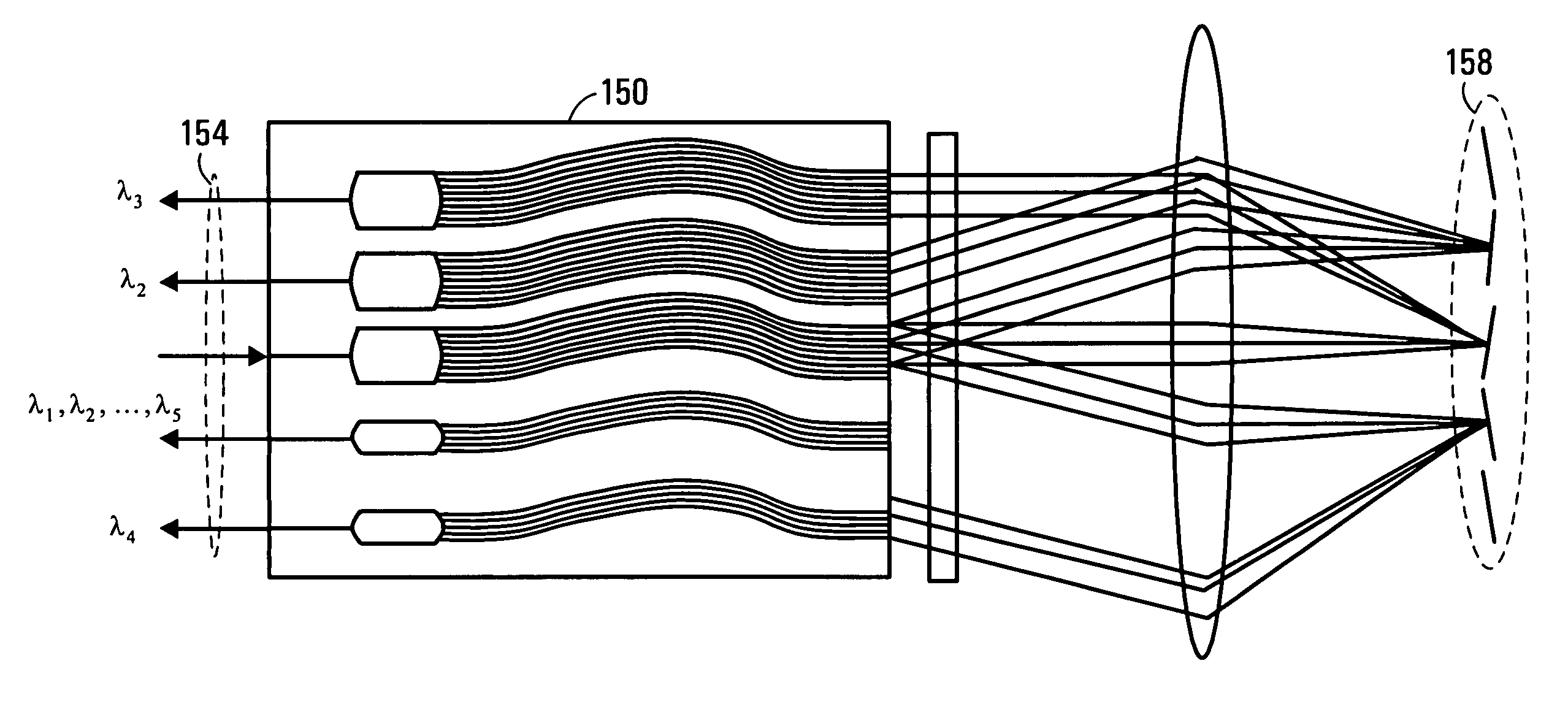

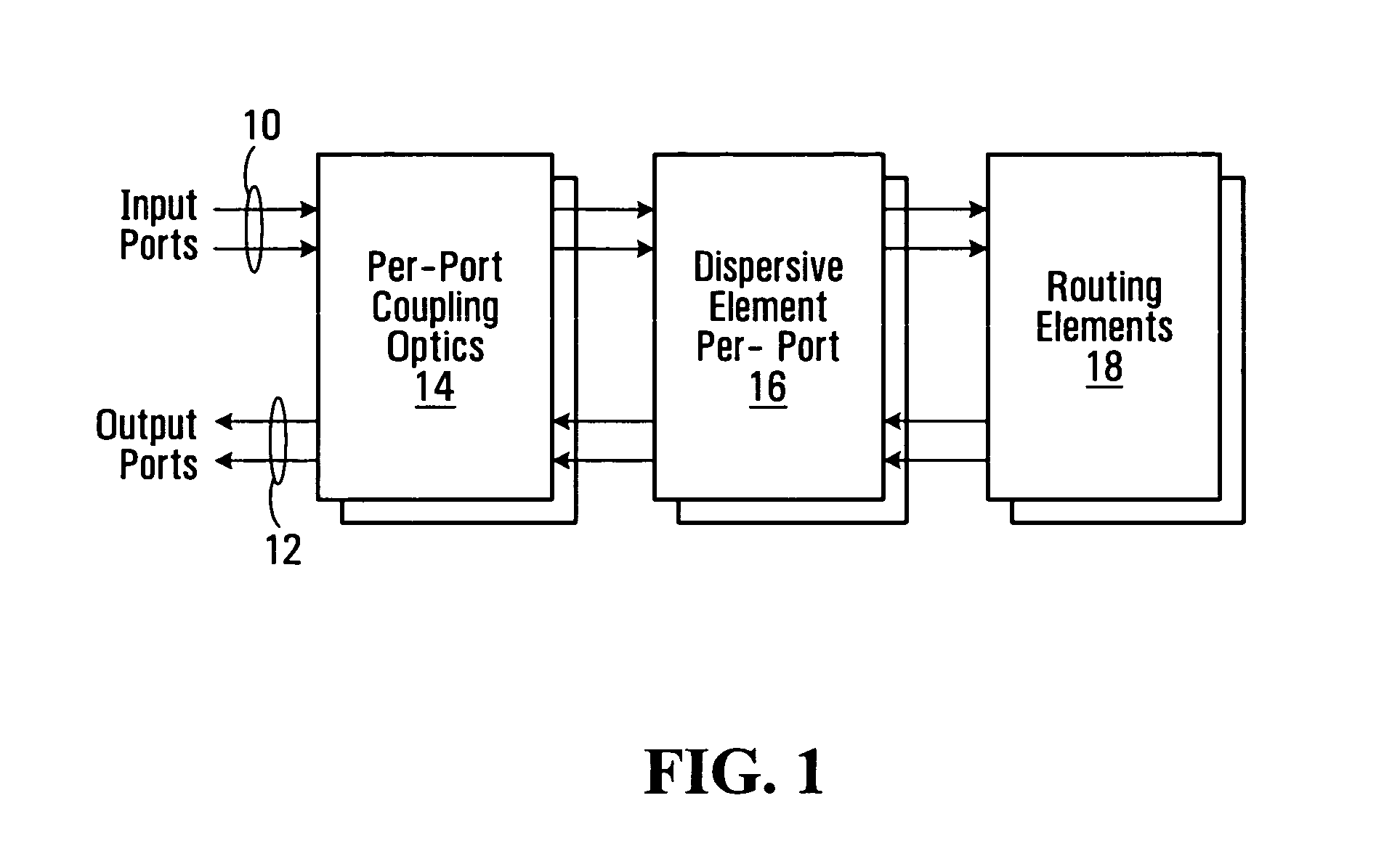

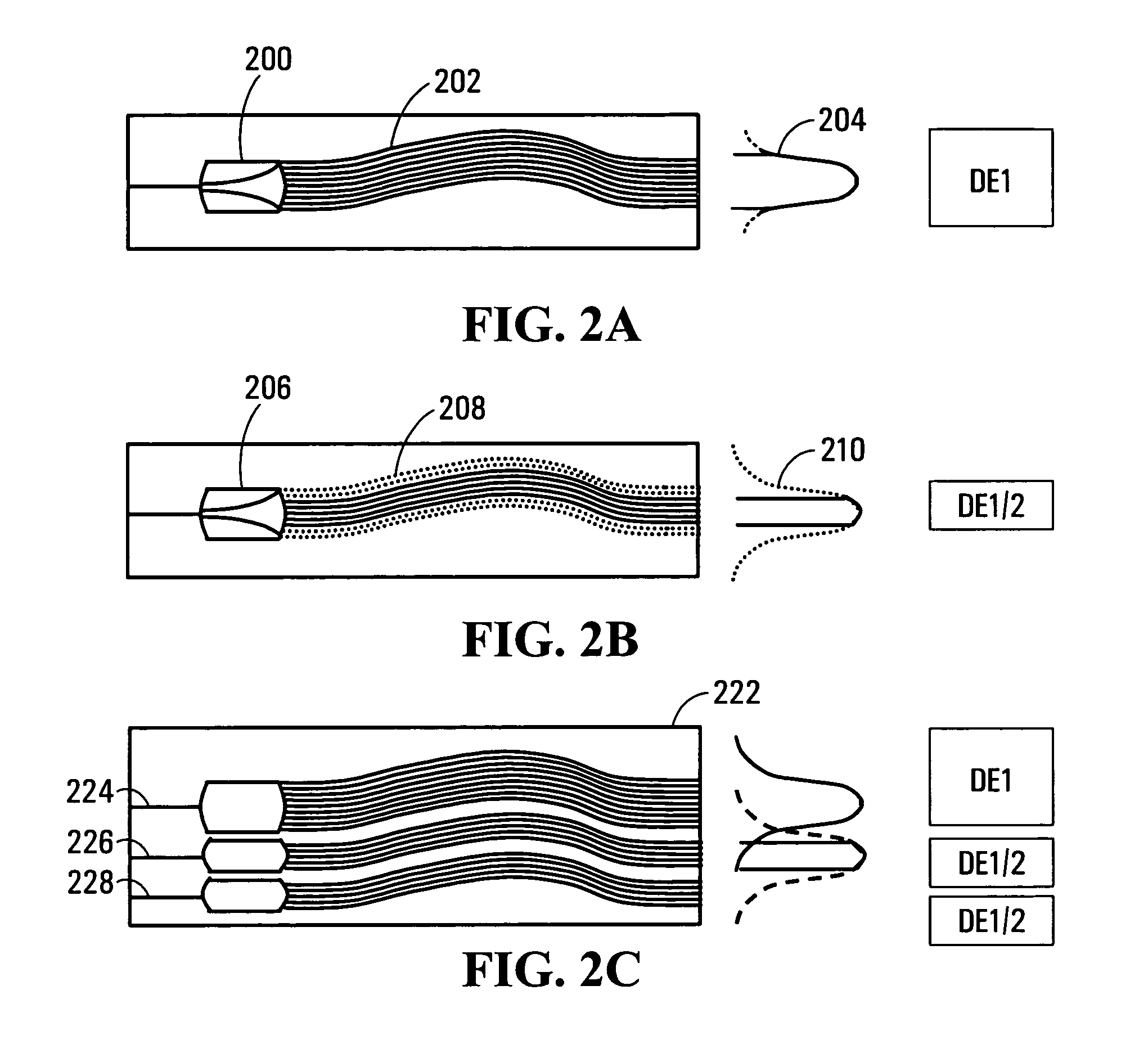

Wavelength cross connect with per port performance characteristics

InactiveUS7321704B2Multiplex system selection arrangementsWavelength-division multiplex systemsEngineeringLength wave

Owner:LUMENTUM OPERATIONS LLC

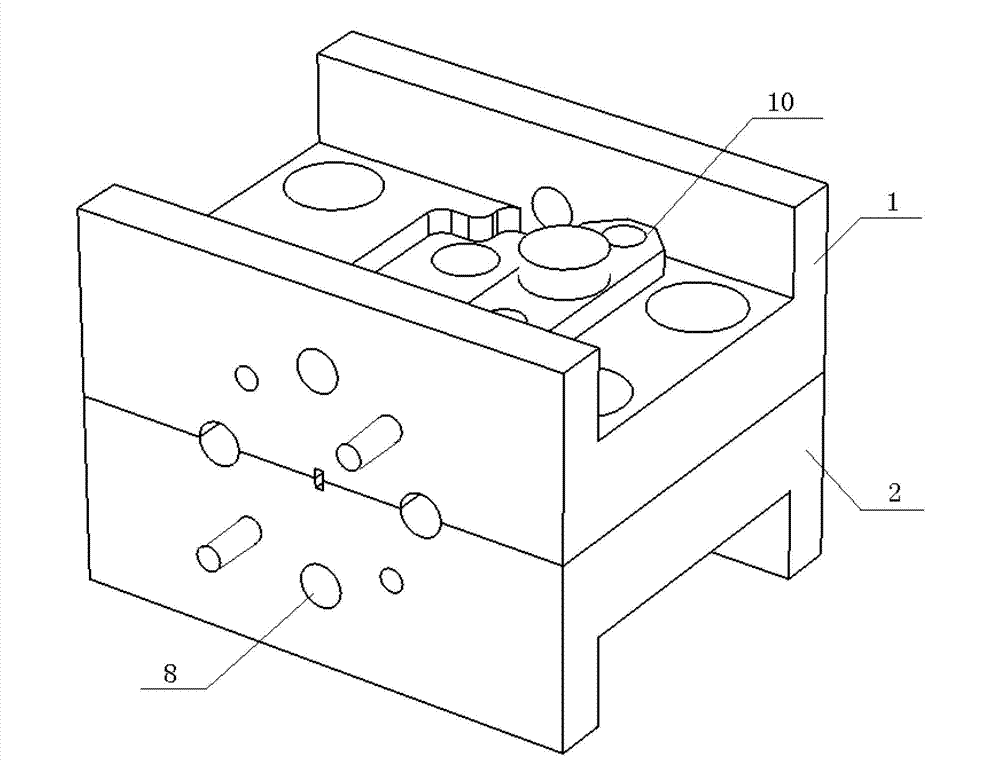

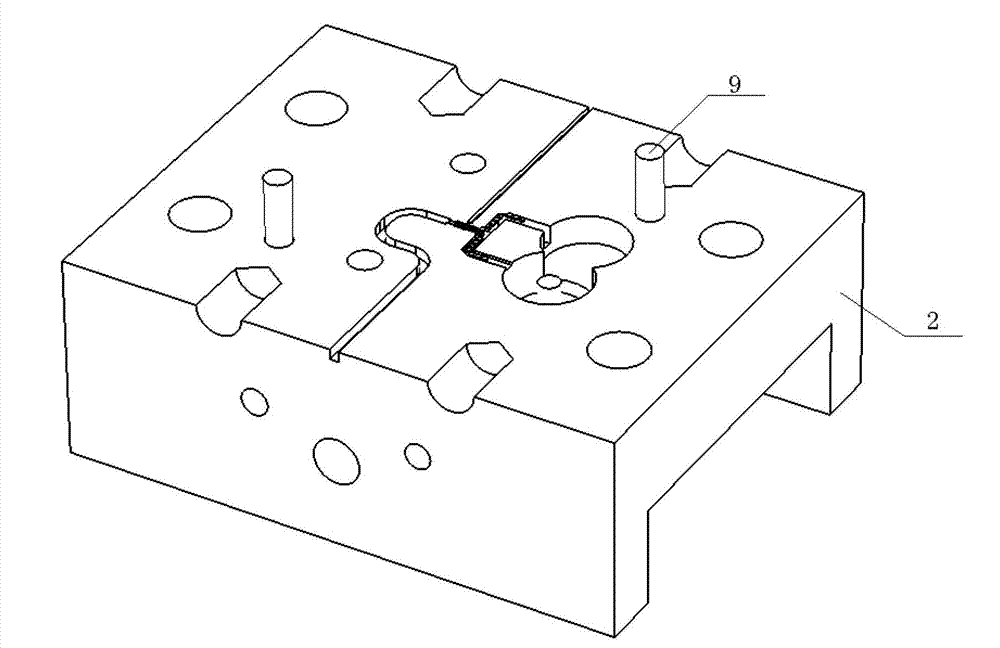

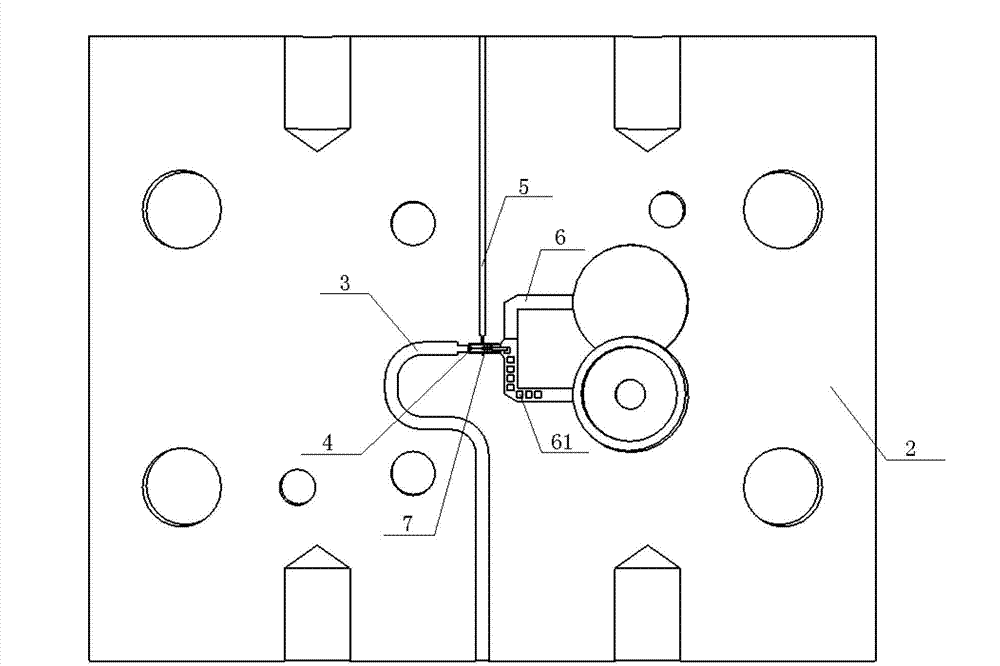

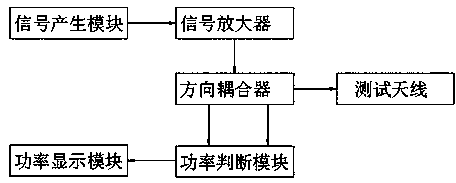

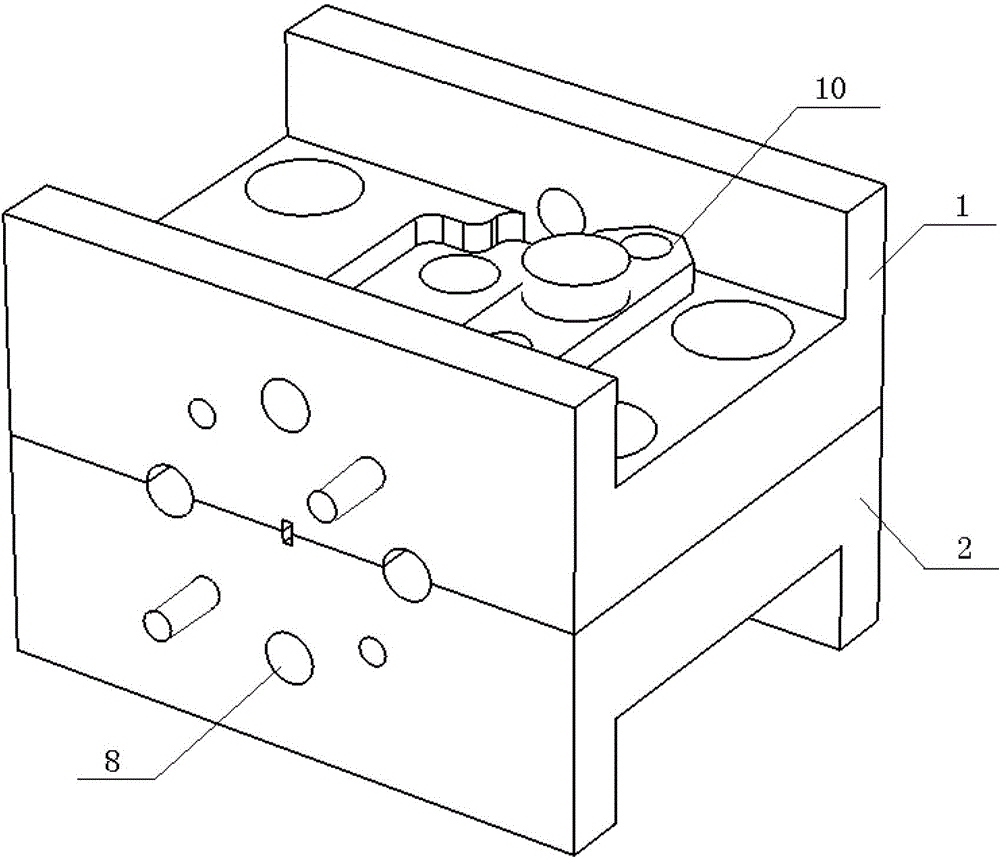

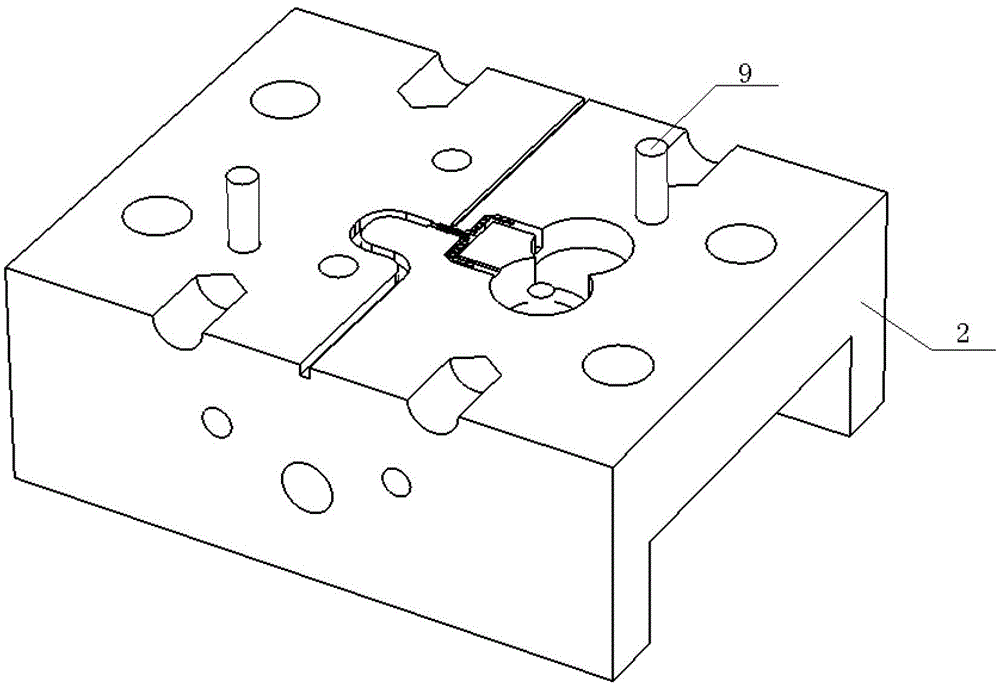

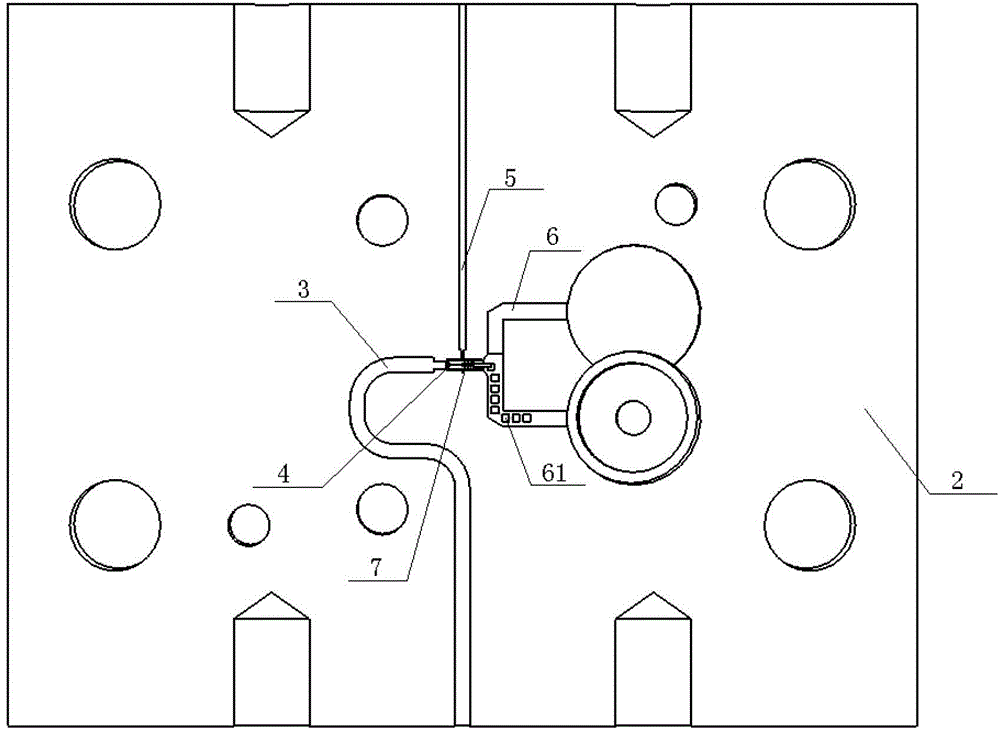

Compact terahertz power synthesis frequency multiplier circuit

ActiveCN102969976AImprove carrying capacityAchieving clutter suppressionOscillations generatorsCapacitanceFrequency multiplier

The invention discloses a compact terahertz power synthesis frequency multiplier circuit which comprises an upper metal substrate and a lower metal substrate, wherein a cavity formed by the upper and lower metal substrates is internally provided with an input waveguide structure, a synthesizing channel, an output waveguide structure and a direct current biasing circuit which are in the same structure, respectively, wherein one end of the synthesizing channel is connected with the input waveguide structure while the other end of the synthesizing channel is connected to the output waveguide structure; the synthesizing channel is internally provided with two thin film chips symmetrical in mirror; and one group of the thin film chips is connected to the upper metal substrate while the other group of the thin film chips is connected to the lower metal substrate. The direct current biasing circuit is provided with chip capacitors connected with the thin film chips. Based on a micro / nano technology, the compact terahertz power synthesis frequency multiplier circuit has the characteristics of compact structure and high integrating degree. The compact terahertz power synthesis frequency multiplier circuit has the characteristics of good port performance and higher power. The compact terahertz power synthesis frequency multiplier circuit has the characteristics of low cost and good consistency and is convenient for large-scale production.

Owner:SOUTHEAST UNIV

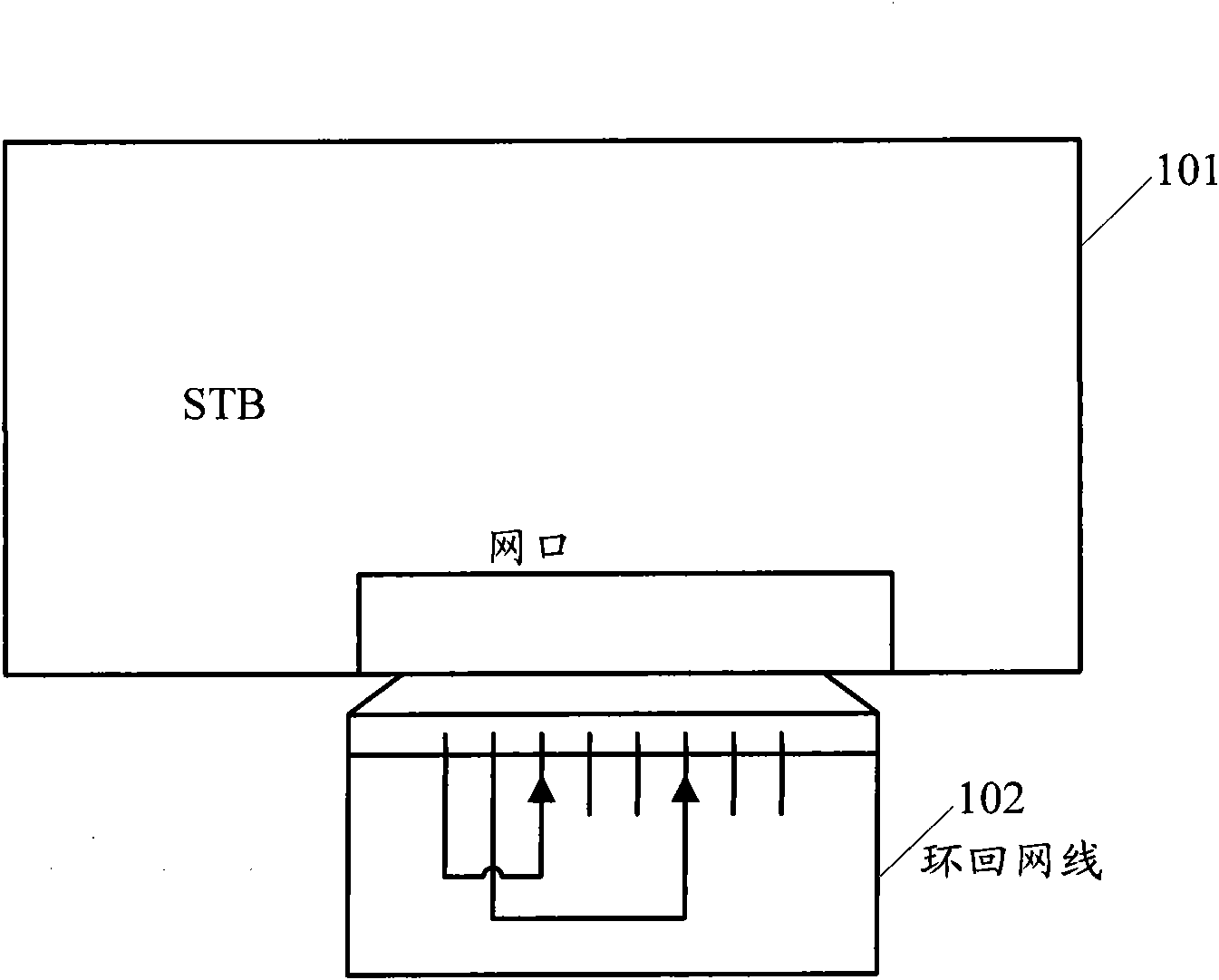

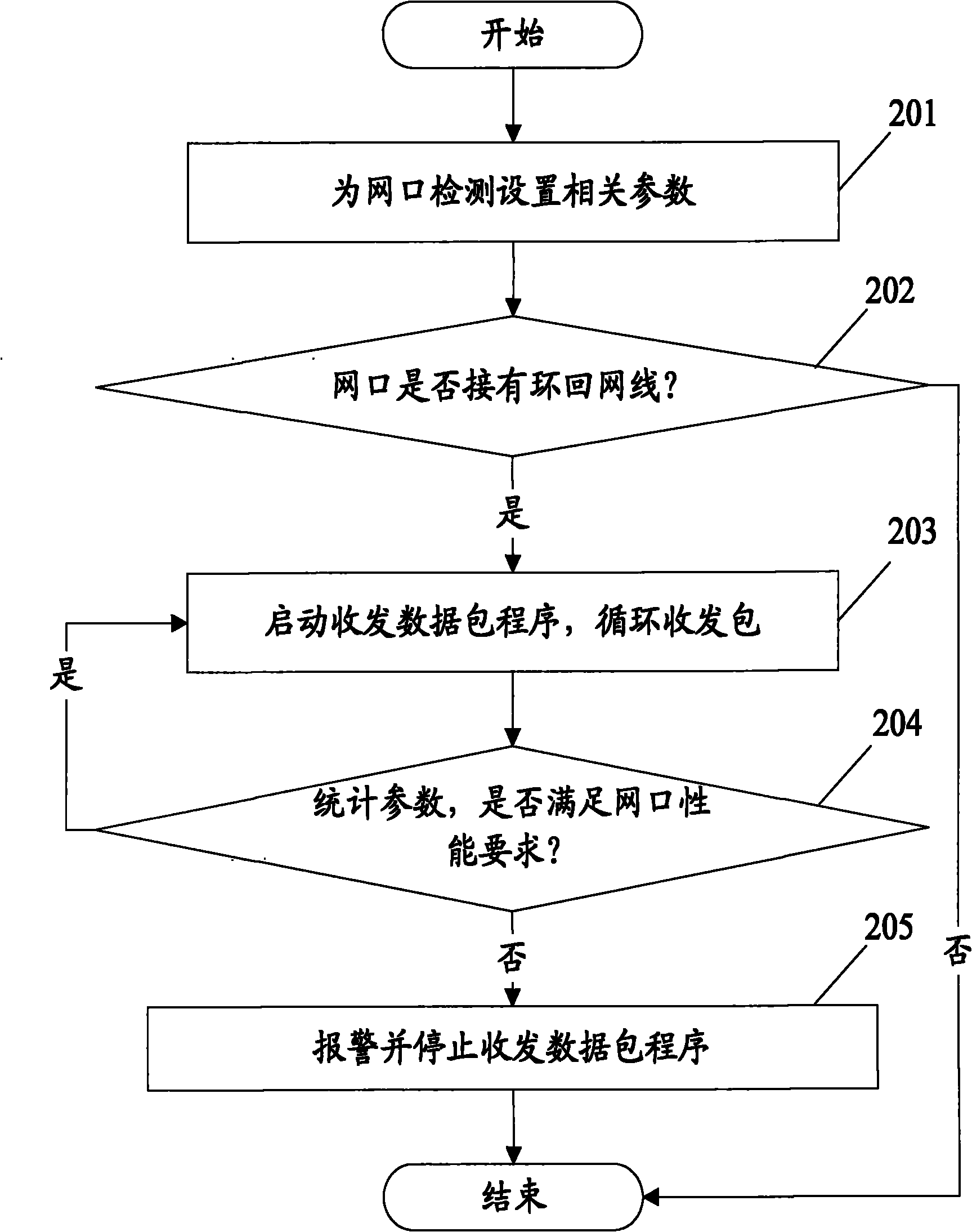

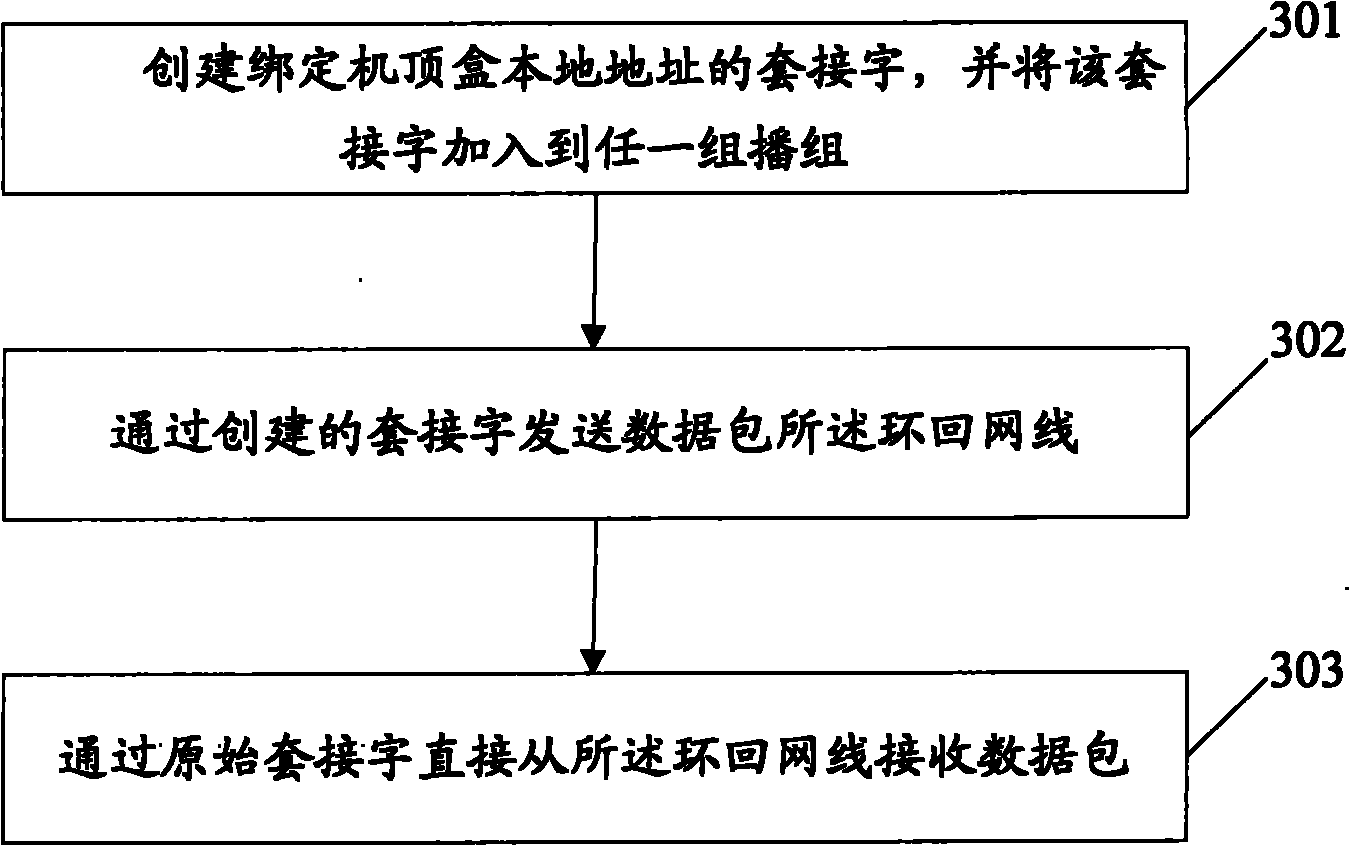

Method and device for detecting network port performance of IPTV set-top box

InactiveCN101877658AImprove performance detection efficiencyEasy to operateData switching networksNetwork packetPerformance index

The invention discloses a method for detecting network port performance of an IPTV set-top box. The device comprises the IPTV set-top box and a loop-back network cable, wherein the head end of the loop-back network cable is plugged into a network port of the IPTV set-top box (STB), so the IPTV set-top box is used for transmitting and receiving data packets through the loop-back network cable connected to the network port, and determining whether the loop-back network cable is connected correctly according to the transmitted data packets and the received data packets; and if the loop-back network cable is connected correctly, every performance index of the network port is detected in the processes of transmitting and receiving the data packets, every detected performance index is compared with a preset performance index threshold value, and the network port performance is determined whether to meet requirements or not according to a comparison result. By using the method and the device disclosed by the invention and inserting the loop-back network cable into the set-top box after the set-top box is started, the detection of every type of the performance indexes of the network port of the set-top box can be performed automatically.

Owner:ZTE CORP

Effect processing of multicast transmissions

InactiveCN1498480ALower requirementAddressing Port Performance DifferencesSpecial service provision for substationData switching by path configurationComputer networkNetwork processor

Multicast transmission on network processors is disclosed in order both to minimize multicast transmission memory requirements and to account for port performance discrepancies. Frame data for multicast transmission on a network processor is read into buffers to which are associated various control structures and a reference frame. The reference frame and the associated control structures permit multicast targets to be serviced without creating multiple copies of the frame. Furthermore this same reference frame and control structures allow buffers allocated for each multicast target to be returned to the free buffer queue without waiting until all multicast transmissions are complete.

Owner:ACTIVISION PUBLISHING

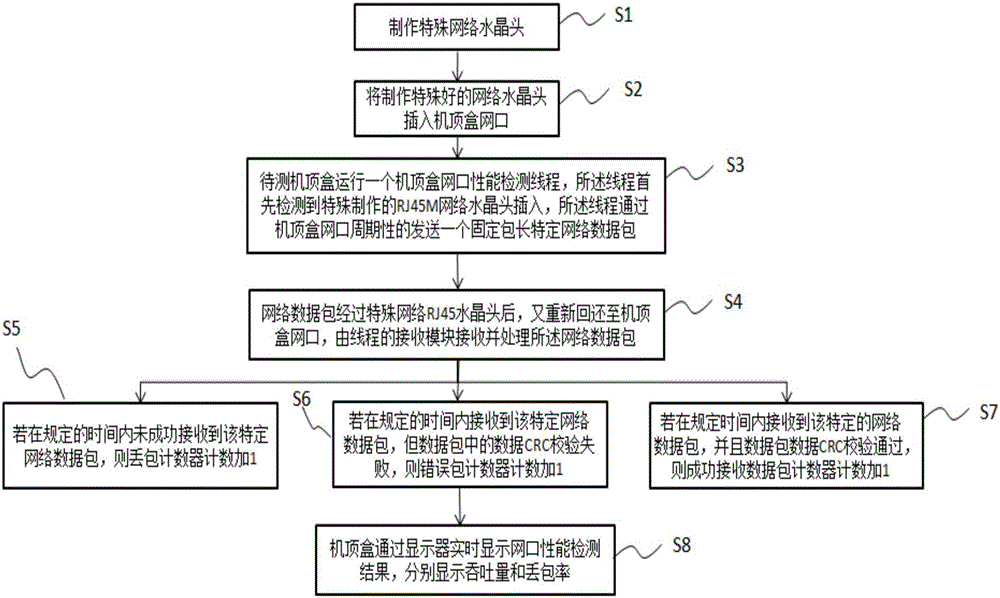

Method for testing performance of network port of set-top box

InactiveCN106657997ASolve the need for a PC serverSolve environmental problemsTelevision systemsTest performanceRegistered jack

The invention discloses a method for testing the performance of a network port of a set-top box. The method comprises the following steps: (1) preparing a special network RJ45 registered jack; (2) inserting the special network RJ45 registered jack in the network port of the to-be-tested set-top box; (3) running a set-top box network port performance detection thread by the to-be-tested set-top box; (4) transmitting a network data packet back to the network port of the set-top box after passing through the registered jack, and receiving and processing the network data packet through a receiving module of the thread; (5) if the particular network data packet is not successfully received, adding 1 to a packet loss counter; (6) if the particular network data packet is received, but the data CRC in the data packet fails the verification, adding 1 to a wrong packet counter; and (7) if the particular network data packet is received, and the data CRC in the data packet passes the verification, adding 1 to a successfully received data packet counter. By adoption of the method disclosed by the invention, the link and connection correctness of the physical network port of the set-top box can be tested, the packet loss rate and the throughput of the network port of the set-top box can also be tested, and long-time pressure burn test is facilitated.

Owner:UNIONMANTECH

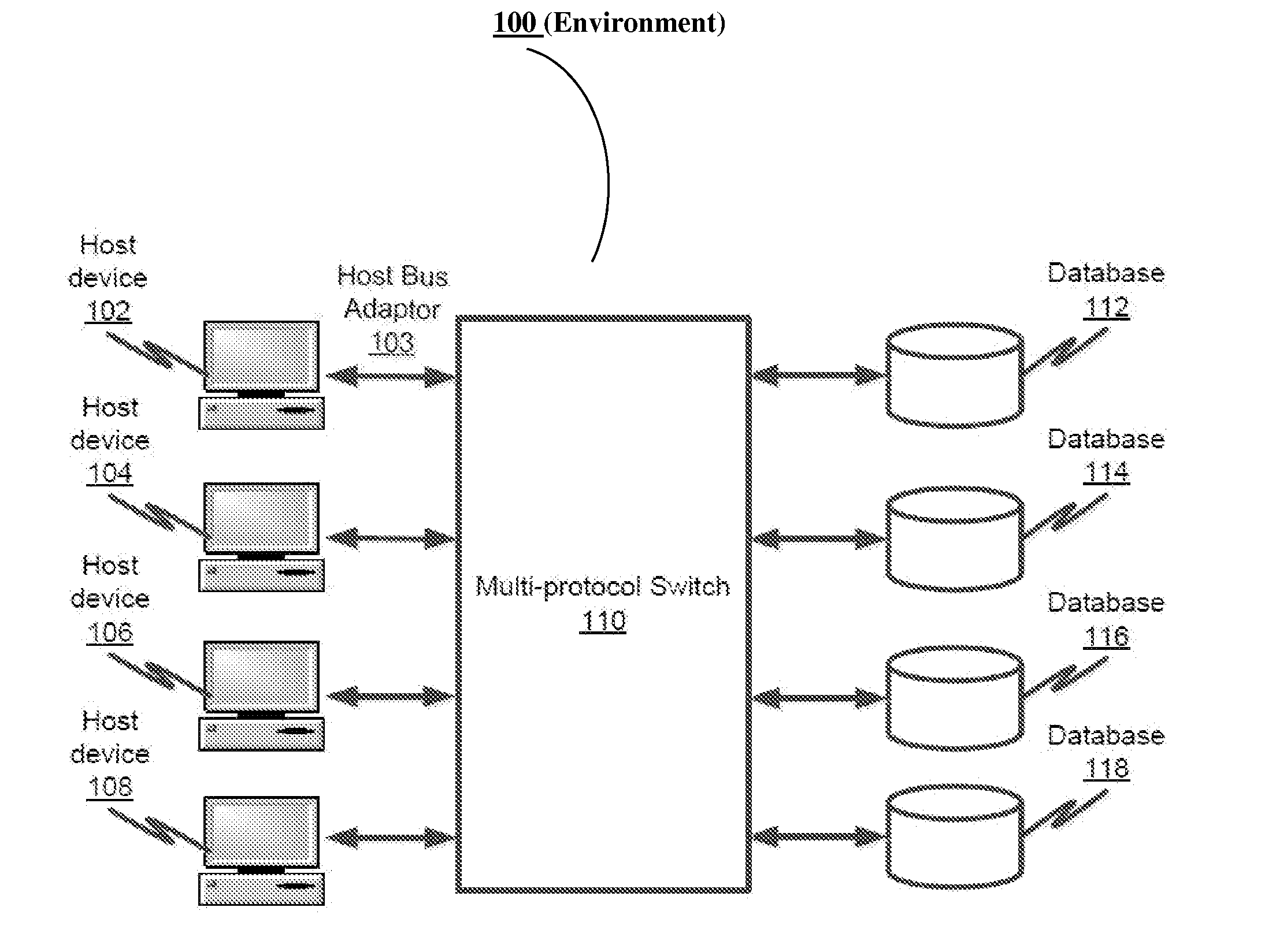

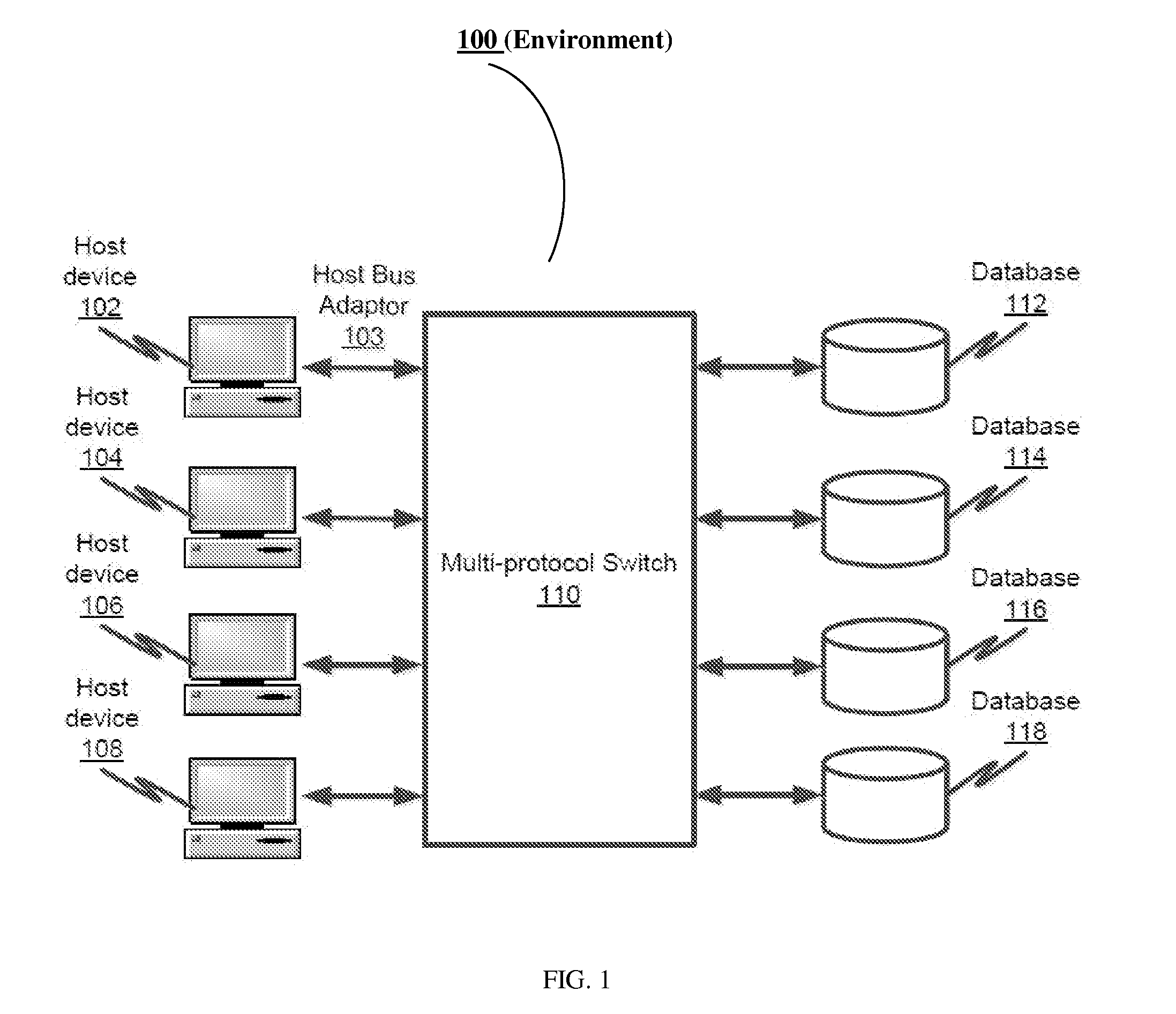

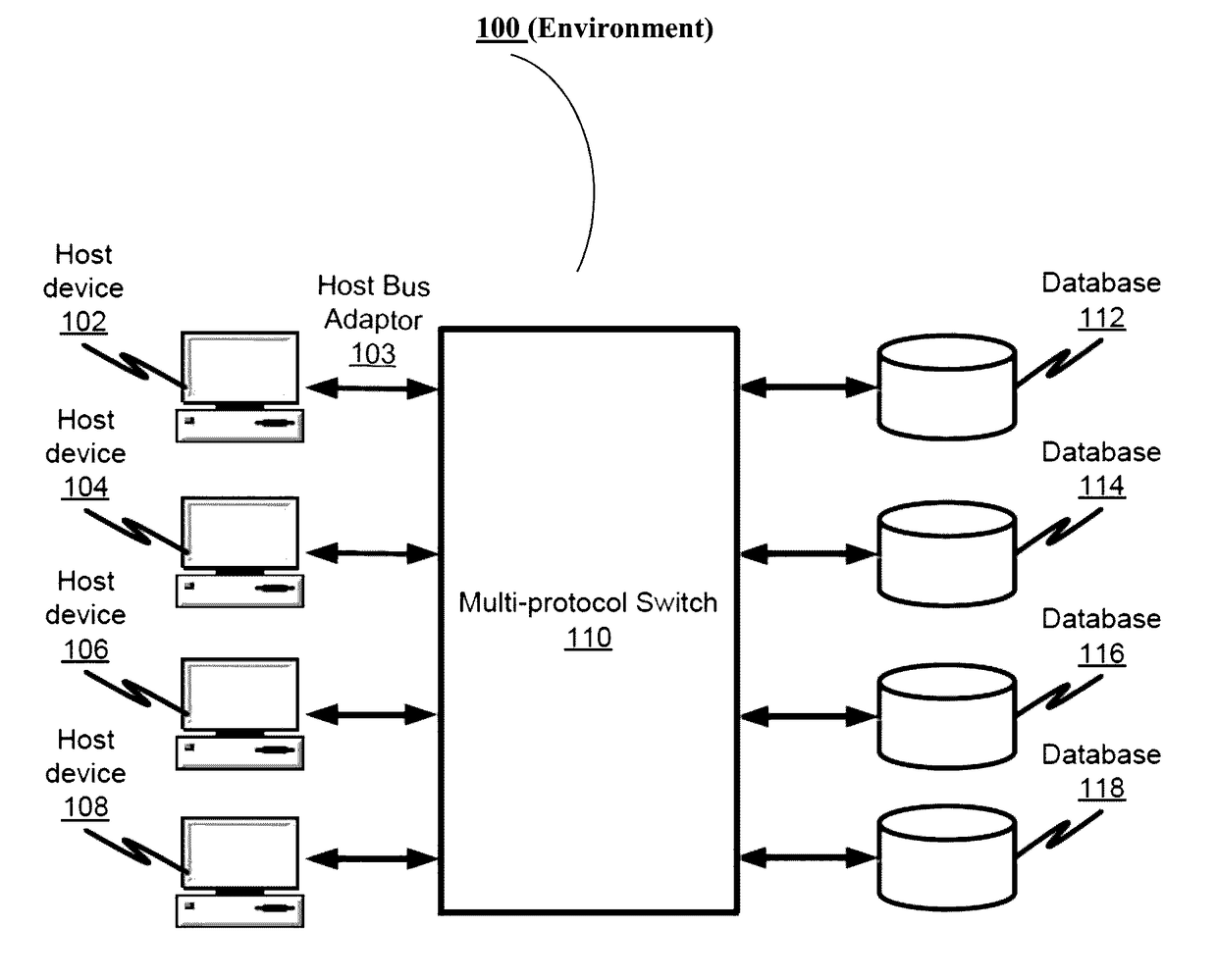

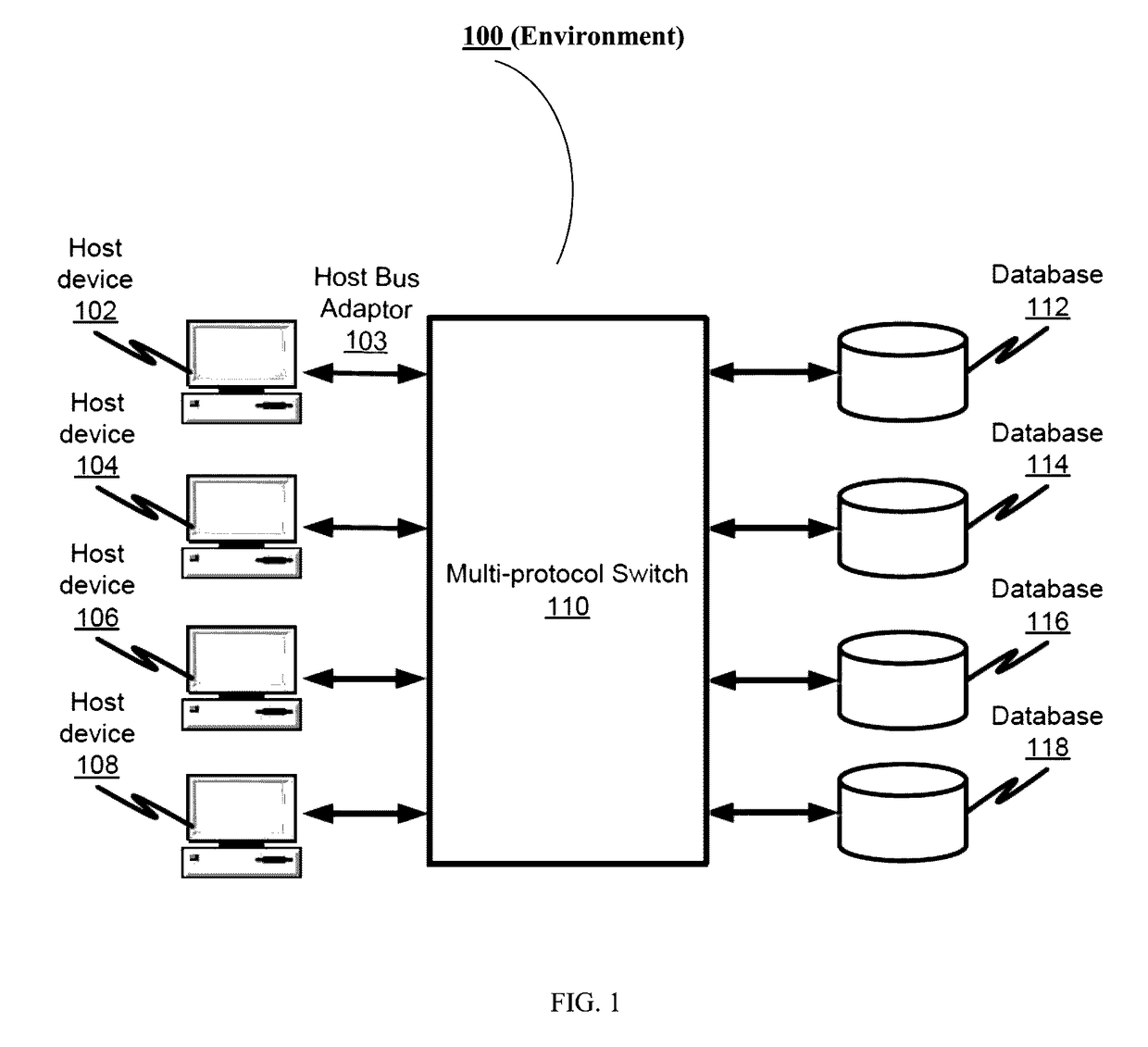

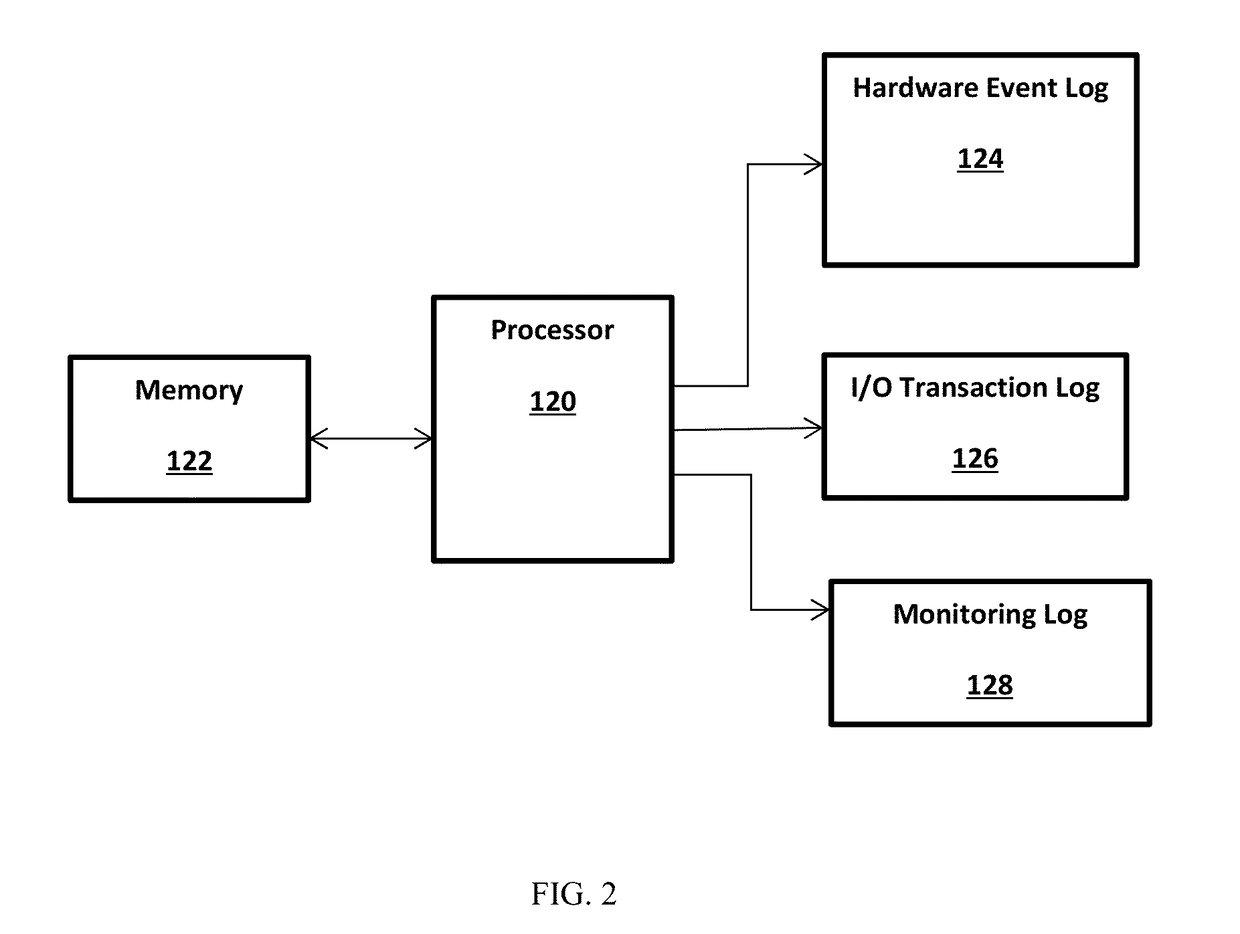

Method and system for port performance ranking in multi-protocol switch

A system and method for port performance ranking in a multi-protocol switch includes monitoring one or more first parameters, the one or more first parameters associated with operating condition of one or more ports of the multi-protocol switch. Each of the one or more first parameters is compared with an associated predefined criterion to determine deviation from the associated predefined criterion. One or more eligible ports is determined from the one or more ports based on non-deviation of each of the one or more first parameters from the associated predefined criterion. For each of the one or more eligible ports, each of one or more second parameters is compared with an associated predefined threshold, the one or more second parameters associated with port traffic statistics. The one or more eligible ports are ranked based on the comparison between each of the second parameters and the associated predefined threshold.

Owner:BIN 2022 SERIES 822 OF ALLIED SECURITY TRUST I

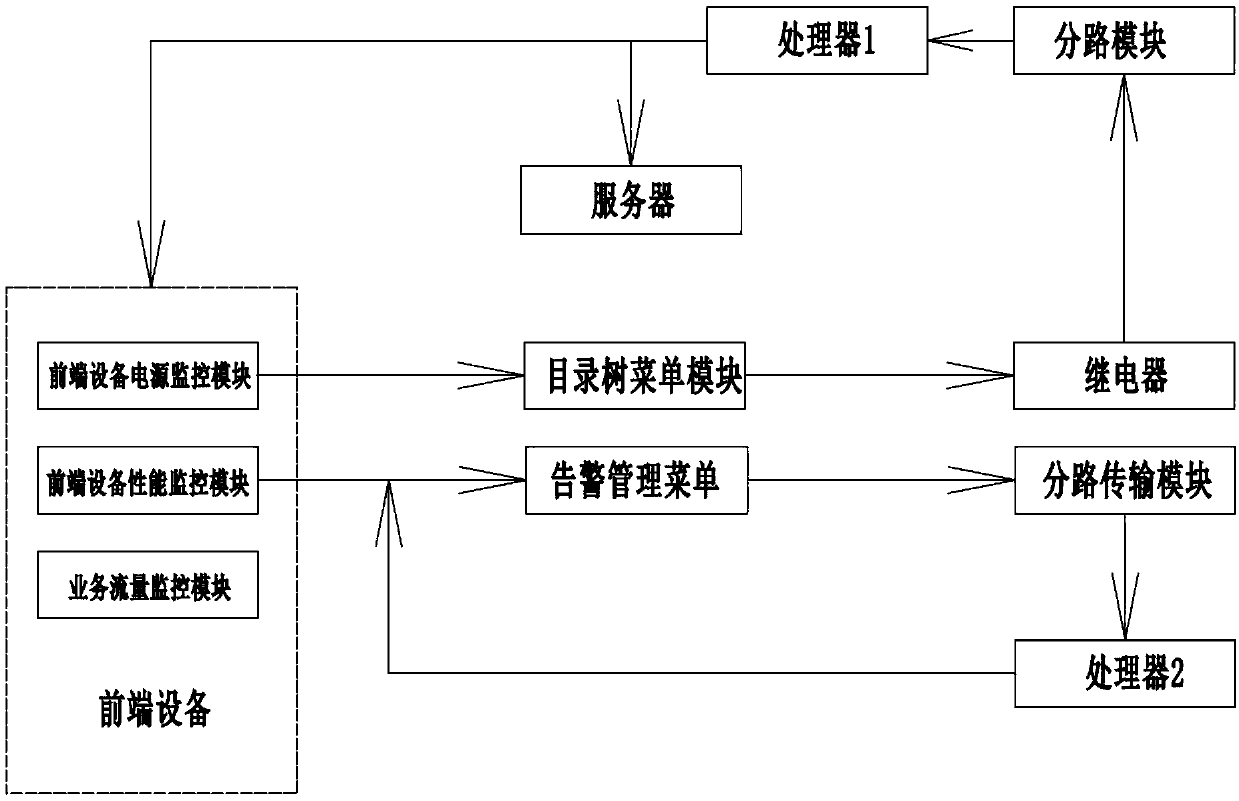

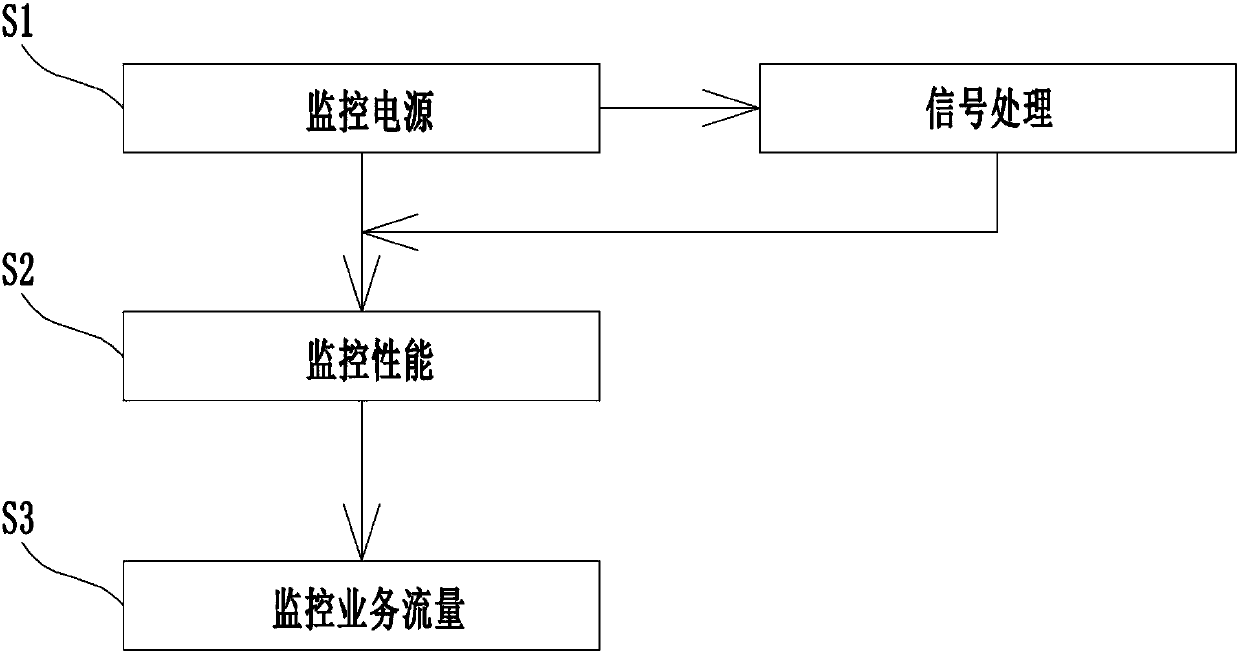

Intelligent monitoring front-end equipment operation and maintenance management and control system and method

InactiveCN107942796AQuick analysisReal-time operation and maintenance controlProgramme controlComputer controlIntelligent lightingMaintenance management

The invention provides an intelligent monitoring front-end equipment operation and maintenance management and control system comprising a front-end equipment power supply monitoring module for carrying out real-time state monitoring of a power supply and simultaneously monitoring a voltage status value of each output power supply, a front-end equipment performance monitoring module for monitoringa CPU usage state, a memory usage rate, and temperature of equipment; and a service traffic monitoring module for monitoring the port traffic and optical port performance of the equipment. In addition, the invention also provides an intelligent monitoring front-end equipment operation and maintenance management and control method. Compared with the prior art, the system and method have the following beneficial effects: a fault cause is analyzed quickly; real-time operation and maintenance control is realized; and the operation and maintenance costs are lowered.

Owner:苏州天华信息科技股份有限公司

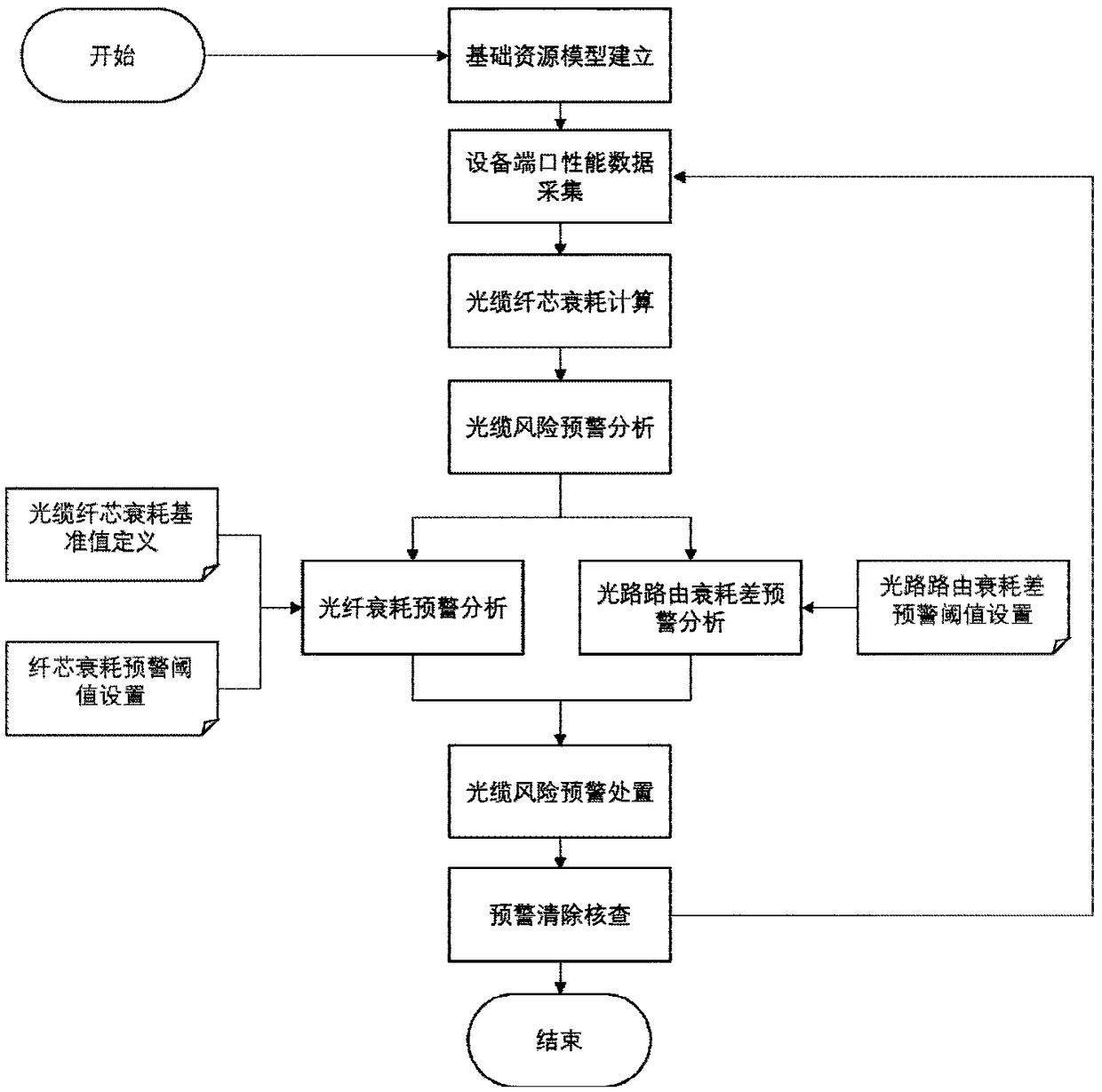

A method for early war and disposal of optical cable risk in electric power communication network

InactiveCN108988938AImprove running qualityImprove applicabilityElectromagnetic transmissionData switching networksUltrasound attenuationEngineering

The invention discloses a method for early warning and disposal of optical cable risk in electric power communication network, in particular, the method comprises seven steps of establishing basic resource model, collecting equipment port performance data, calculating optical cable core attenuation, defining optical cable core attenuation reference value, performing early warning analysis of optical cable risk, disposing optical cable risk early warning list, and clearing early warning and insepcting. The invention has obvious beneficial effect and strong practicability, and greatly improvesthe operation and maintenance working level and the network operation quality.

Owner:INFORMATION COMM COMPANY STATE GRID SHANDONG ELECTRIC POWER +1

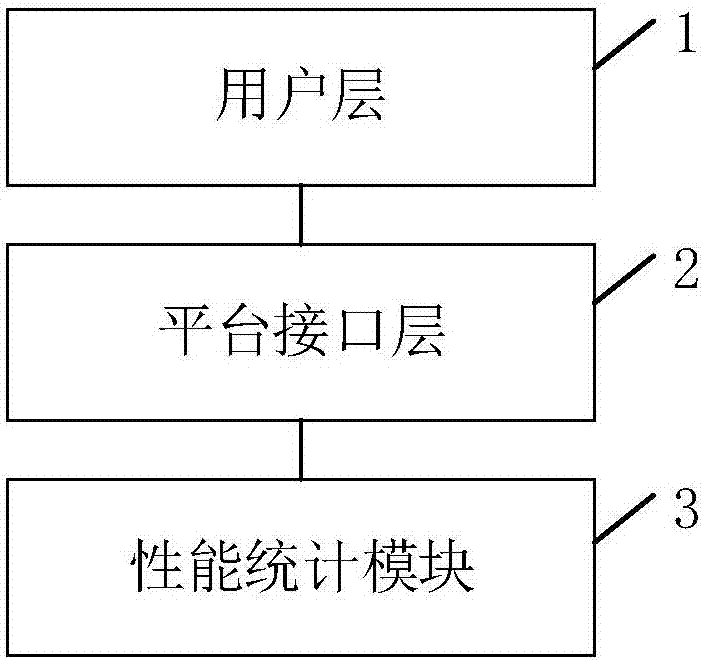

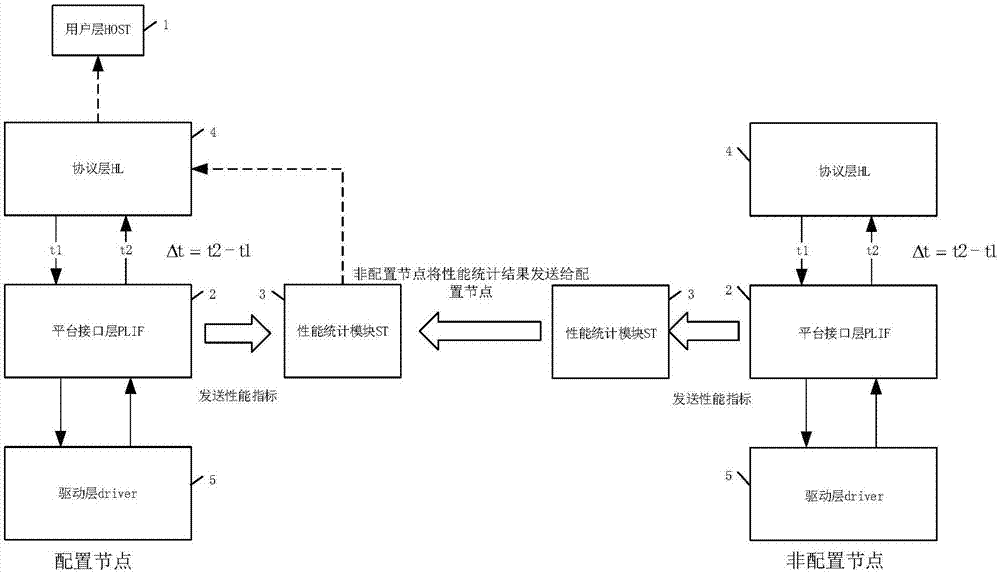

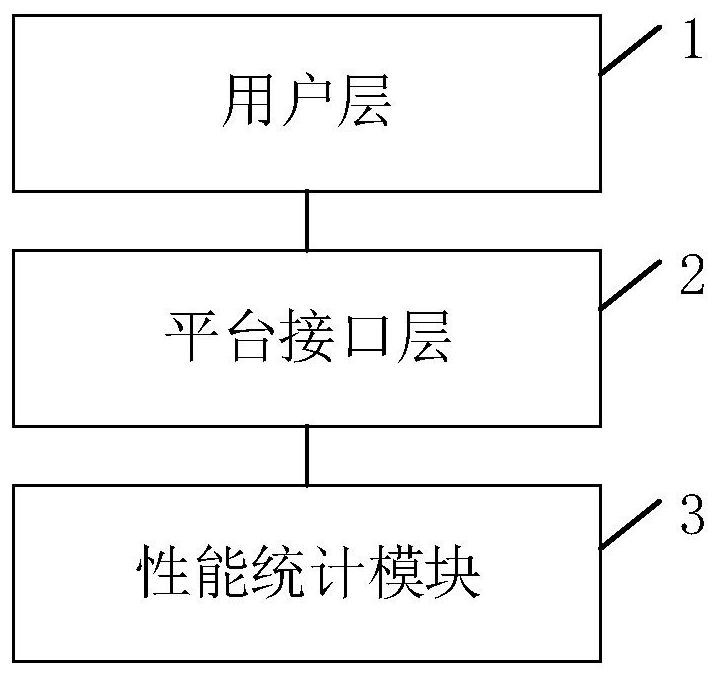

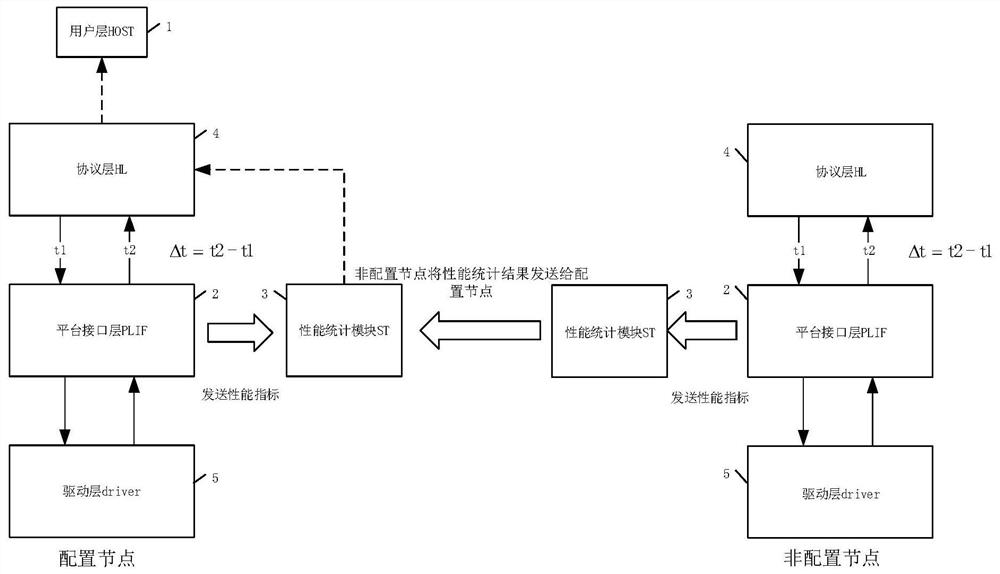

Port performance statistics system

ActiveCN107465579AReduce load pressureEasy statisticsData switching networksInterface layerComputer module

The invention discloses a port performance statistics system. The system comprises a user layer, a platform interface layer and a performance statistics module, wherein the platform interface layer is separately connected with the user layer and the performance statistics module; the platform interface layer is used for obtaining a first time value that each IO arrives at a destination port and enters a queue, determining the current number of the IOs in the queue when the IOs are allocated to a thread, determining a second time value that each IO leaves the destination port after being processed at the storage end, determining each delay, and sending each delay and the current number of the IOs to the performance statistics module; and the performance statistics module is used for calculating the port performance of the destination port, wherein the port performance includes the average delay of the destination port and the real-time number of the IOs in the queue. By adopting the port performance statistics system disclosed by the embodiment of the invention, the port performance of the destination port is calculated in the platform interface layer and the performance statistics module, and thus the load pressure of a driver layer can be reduced; and the system is simple in statistical process and more accurate in statistical result.

Owner:INSPUR SUZHOU INTELLIGENT TECH CO LTD

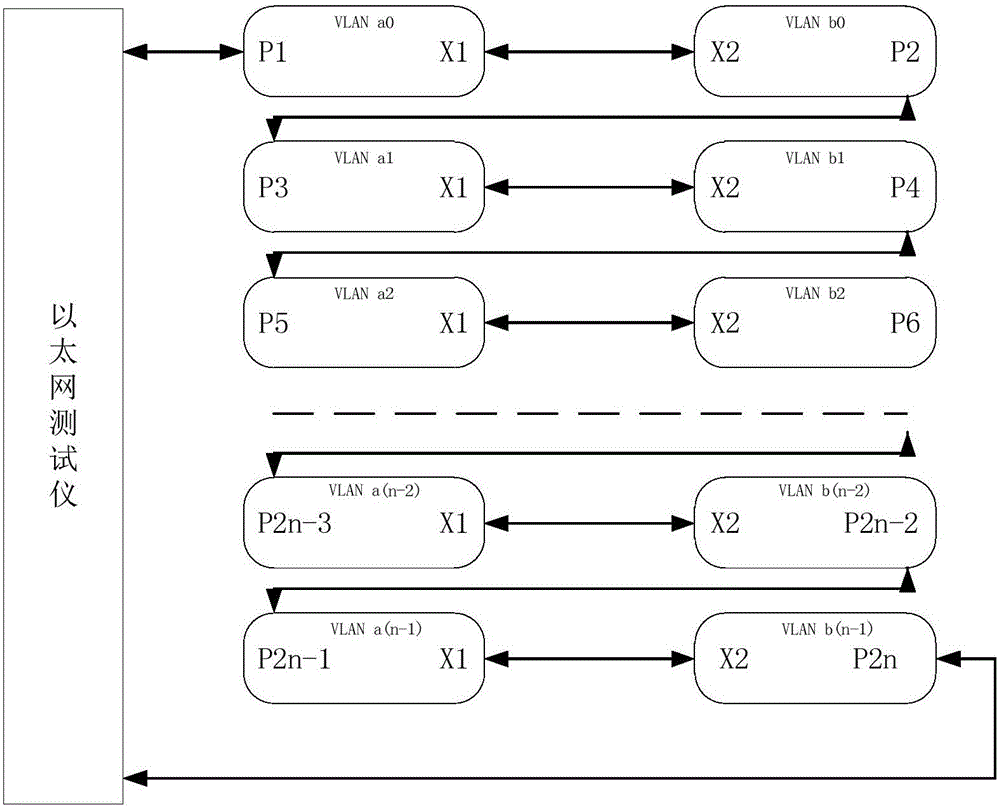

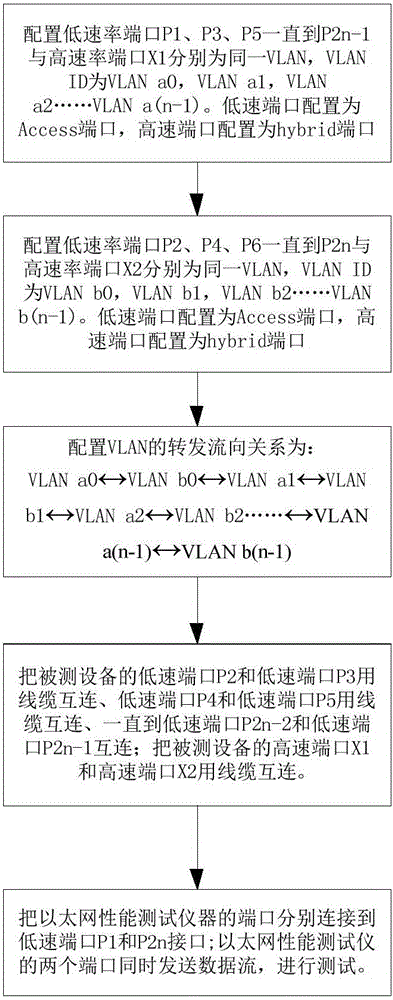

Method for testing high-speed port performance on basis of low-speed port of Ethernet switch

InactiveCN106789433AReduce usageAvoid using low-bandwidth Ethernet performance testsNetworks interconnectionLow speedTester device

The invention discloses a method for testing the high-speed port performance on the basis of low-speed ports of an Ethernet switch. The method comprises the following steps that a VLAN (virtual local area network) is configured for the low-speed ports and high-speed ports of the Ethernet switch, wherein the product of the number of the low-speed ports and the port speed is equal to the high-speed port speed; the forwarding flow direction relationship of the VLAN is configured; for the low-speed ports, except the first port and the last port, other low-speed ports are mutually connected, and the high-speed ports are mutually connected; one port of an Ethernet performance test instrument is connected with a first low-speed port of a switch to be tested; the other port of the Ethernet performance test instrument is connected with the last low-speed port of the switch to be tested, so that the test is performed. The method has the advantages that the performance test of the high-speed port of the Ethernet switch can be completed by the Ethernet performance test instrument with low bandwidth; the development cost is reduced; the test method is simplified.

Owner:武汉微创光电股份有限公司

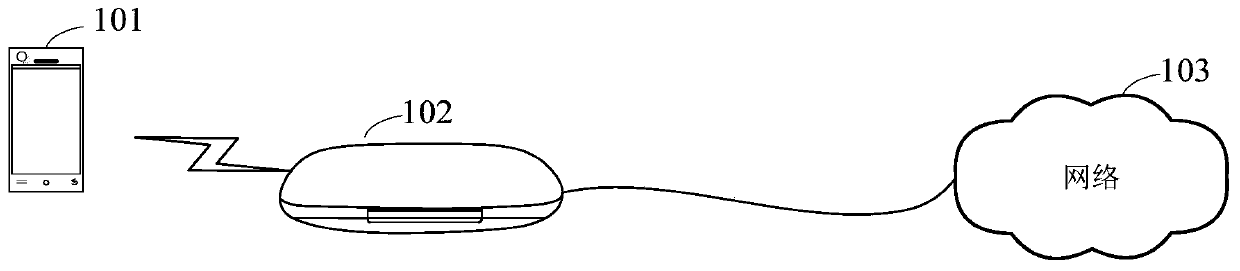

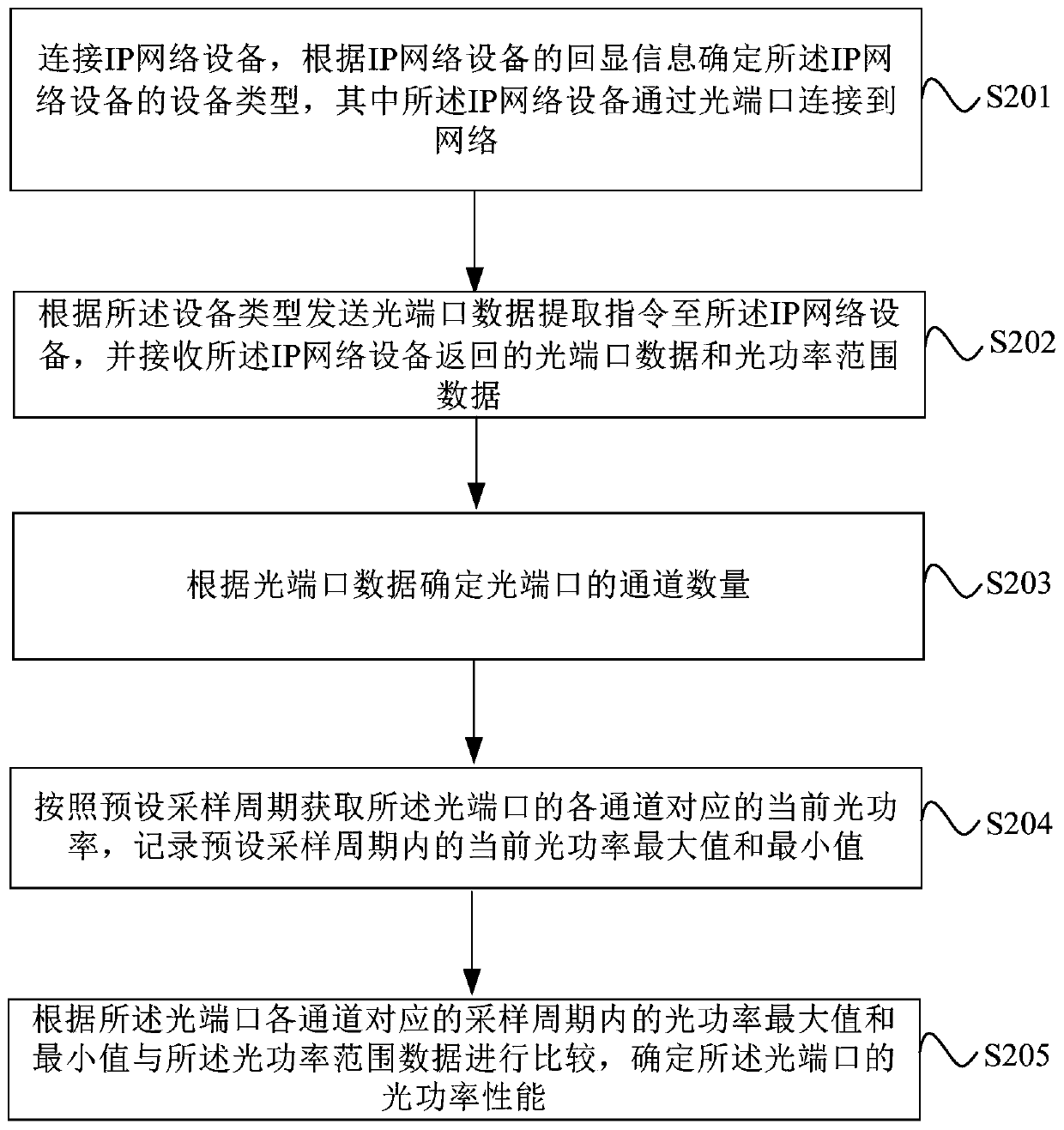

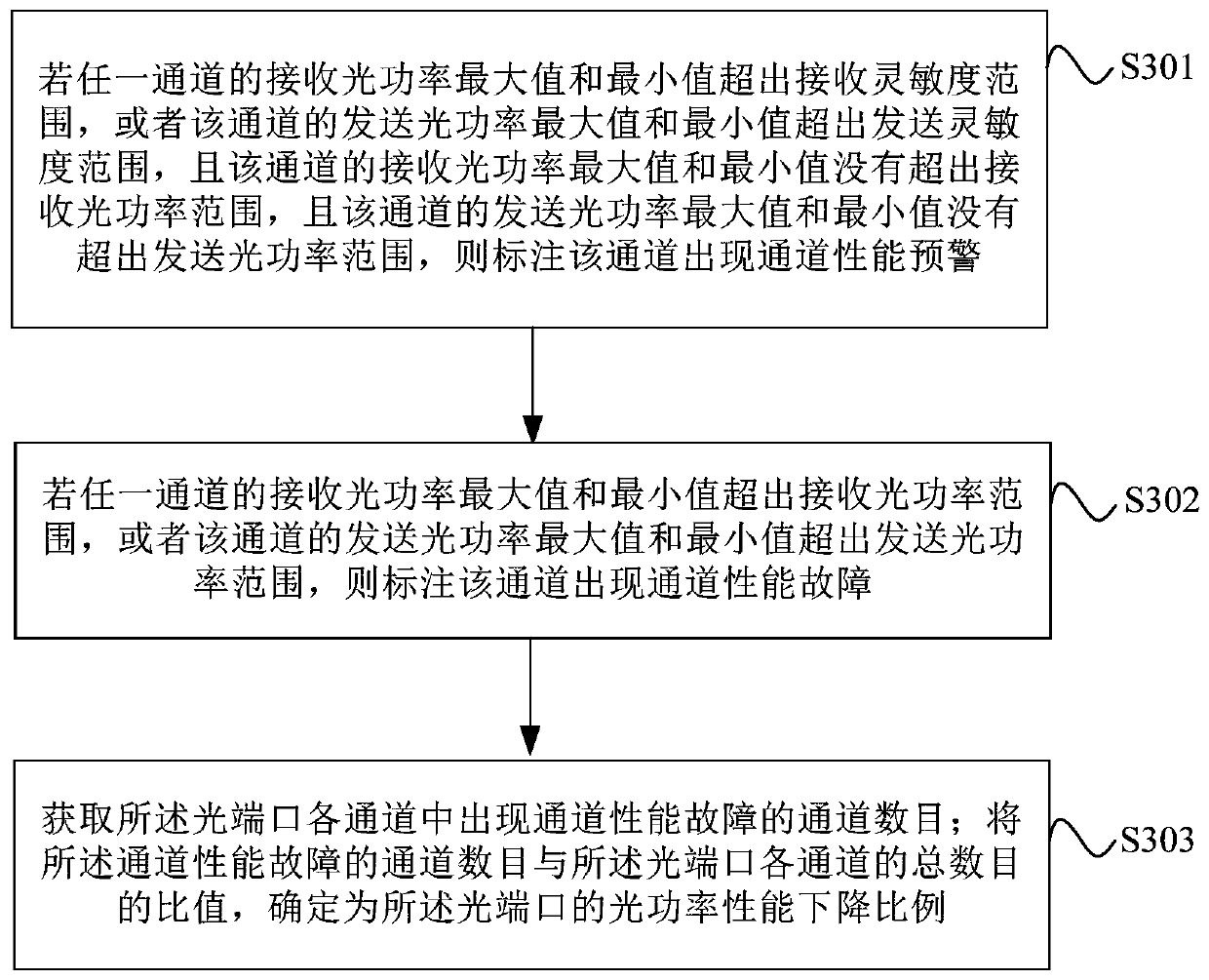

IP network optical port performance evaluation method and equipment

ActiveCN110365406AEasy to useImprove test efficiencyElectromagnetic transmissionTest efficiencyOptical power

The embodiment of the invention provides an IP network optical port performance evaluation method and equipment. The method comprises the following steps: receiving optical port data and optical powerrange data of an optical port returned by IP network device; determining the number of channels of the optical port according to the optical port data; acquiring current optical power corresponding to each channel of the optical port according to a preset sampling period, and recording a maximum value and a minimum value of the current optical power in the preset sampling period; and determiningthe optical power performance of the optical port by comparing the maximum value and the minimum value of the current optical power in the sampling period corresponding to each channel of the opticalport with the optical power range data, so that the normal use of IP network device is not influenced, a test with a service and a batch test can be carried out, and the test efficiency is relativelyhigh.

Owner:CHINA UNITED NETWORK COMM GRP CO LTD

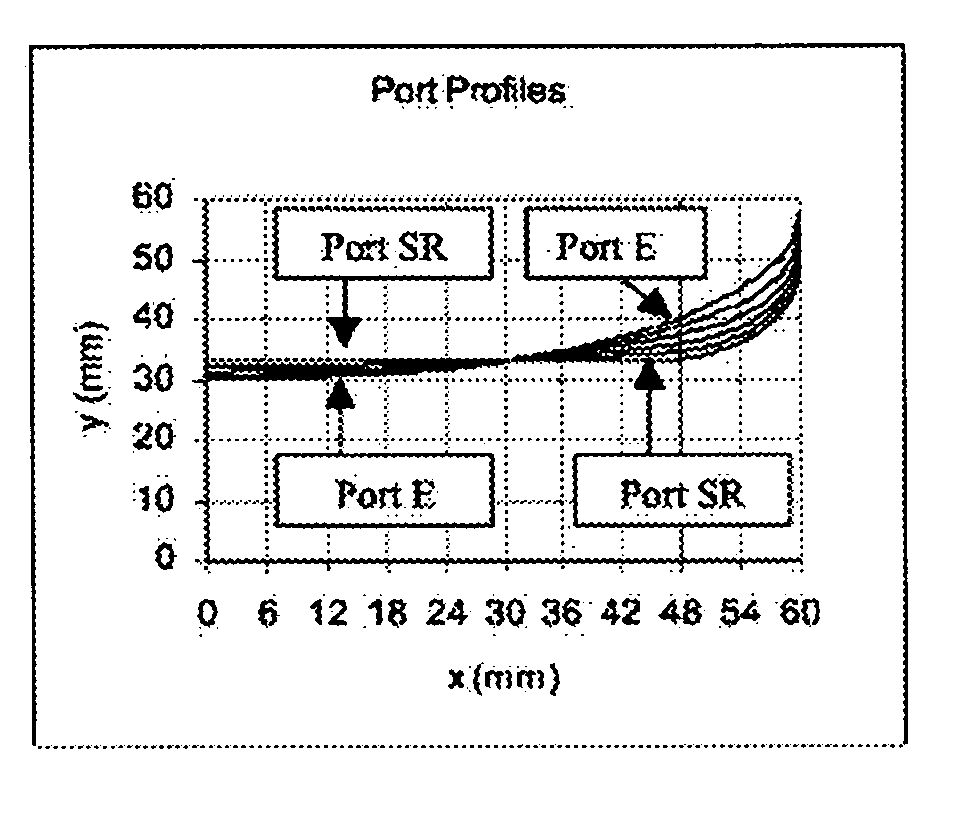

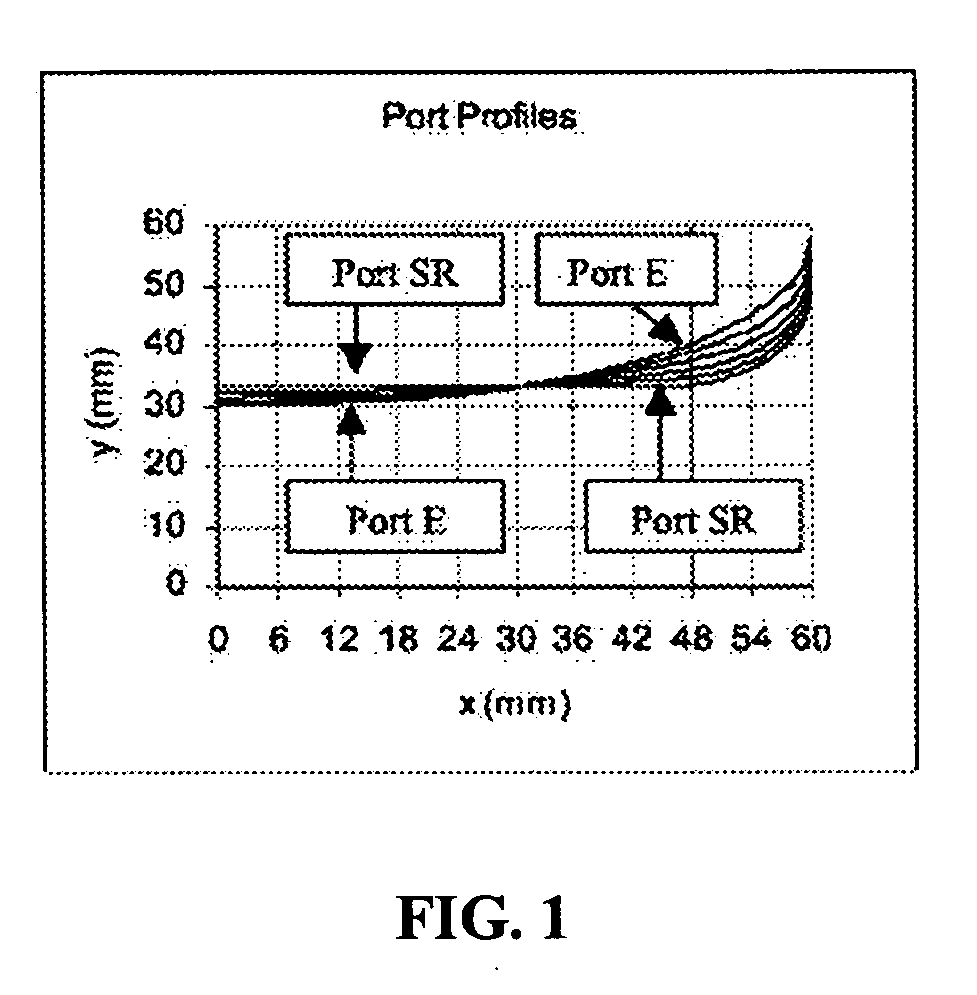

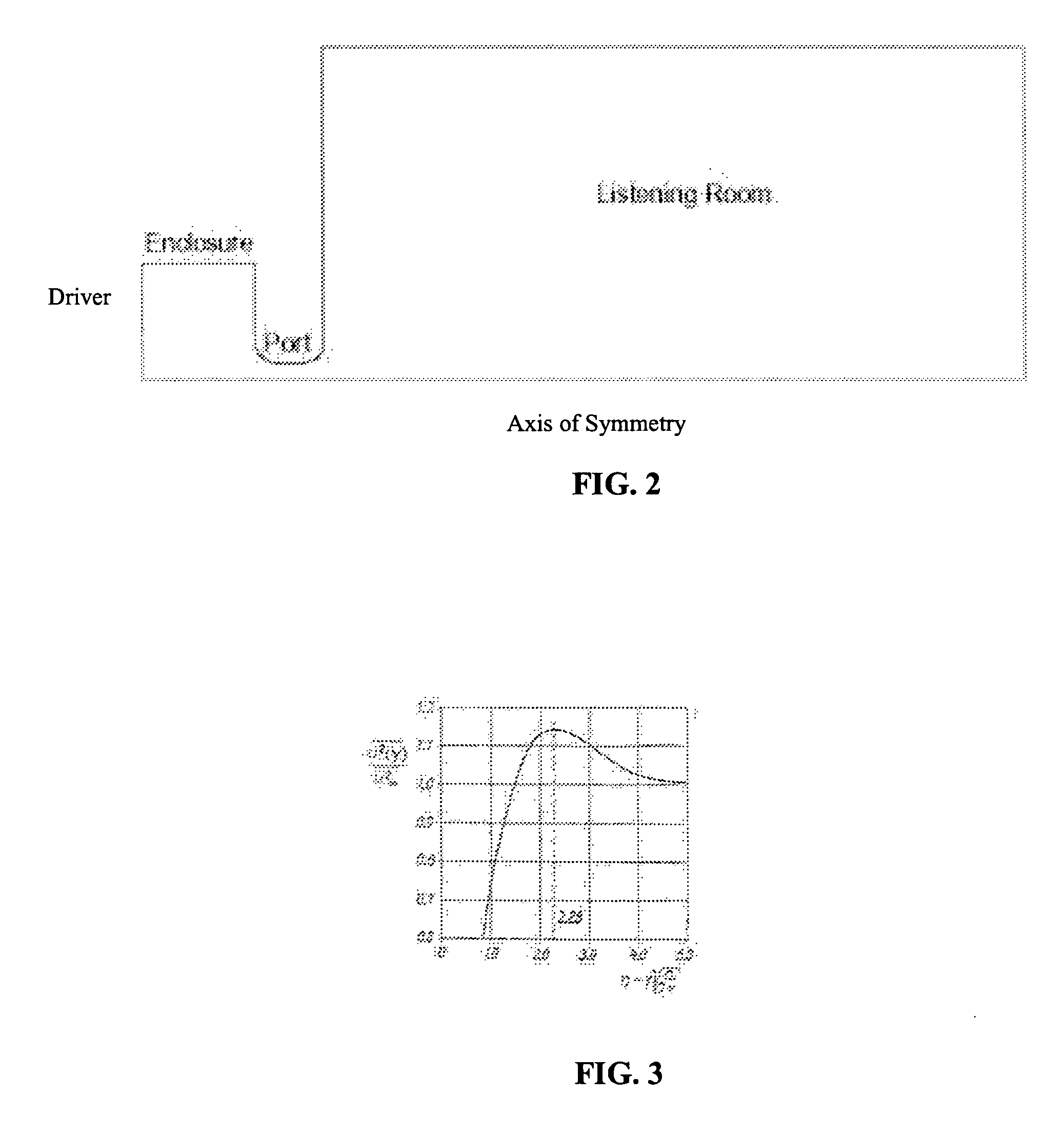

Method for predicting loudspeaker port performance and optimizing loudspeaker port designs utilizing bi-directional fluid flow principles

InactiveUS20060052992A1Optimizing port designPredictive performanceTransducer detailsSpecial data processing applicationsEngineeringLoudspeaker

A method is provided for predicting the performance of a loudspeaker port and optimizing port design. The method involves defining the geometries of a loudspeaker port, modeling the bi-directional fluid flow in the defined port utilizing a modeling method known as Computation Fluid Dynamics (“CFD”) and analyzing the flow model to determine whether the flow characteristic displayed in the model represent optimum flow characteristics for port performance. To optimize port design, the geometries of the port may be altered and modeled until the flow characteristic represents flow indicative of optimum port performance.

Owner:HARMAN INT IND INC

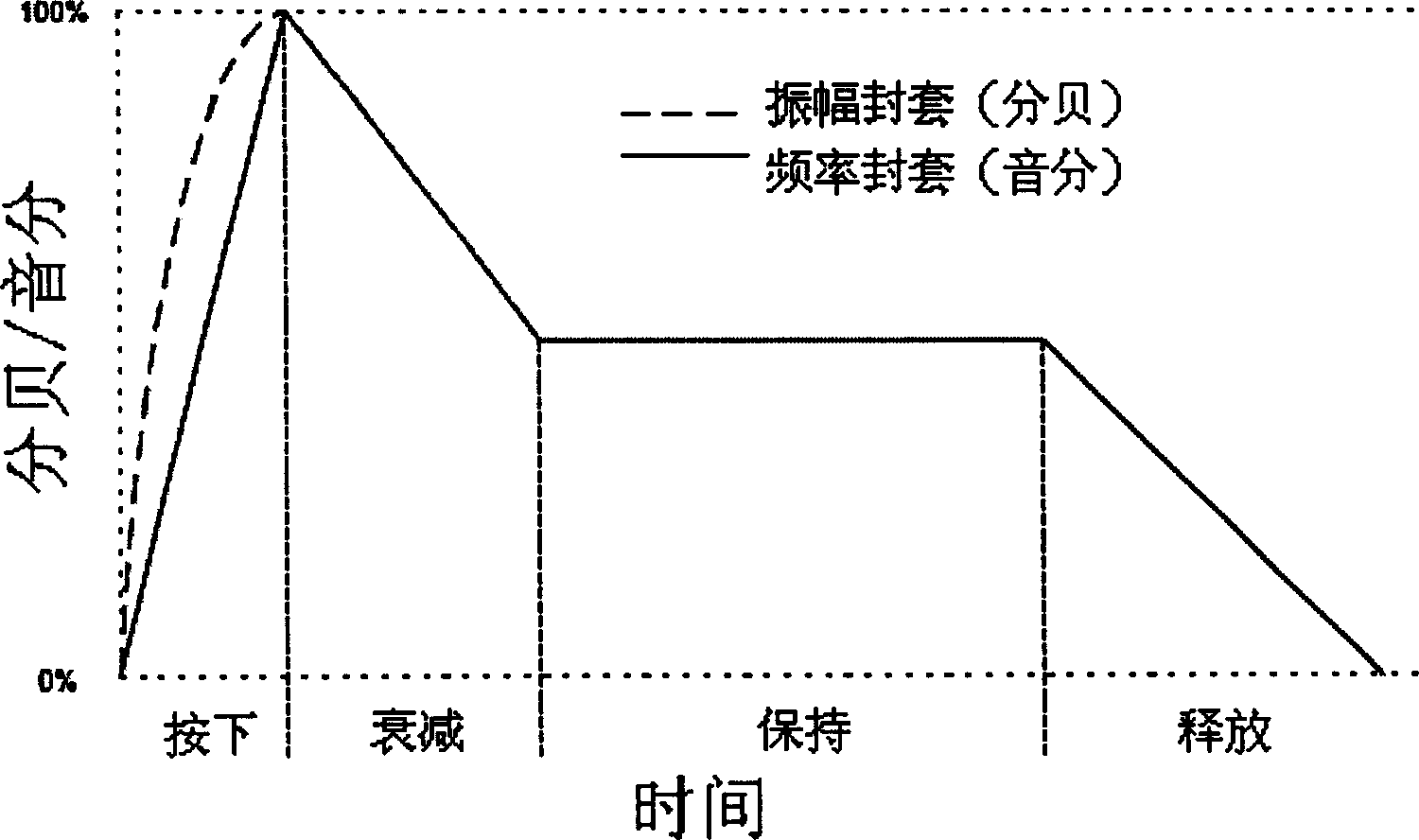

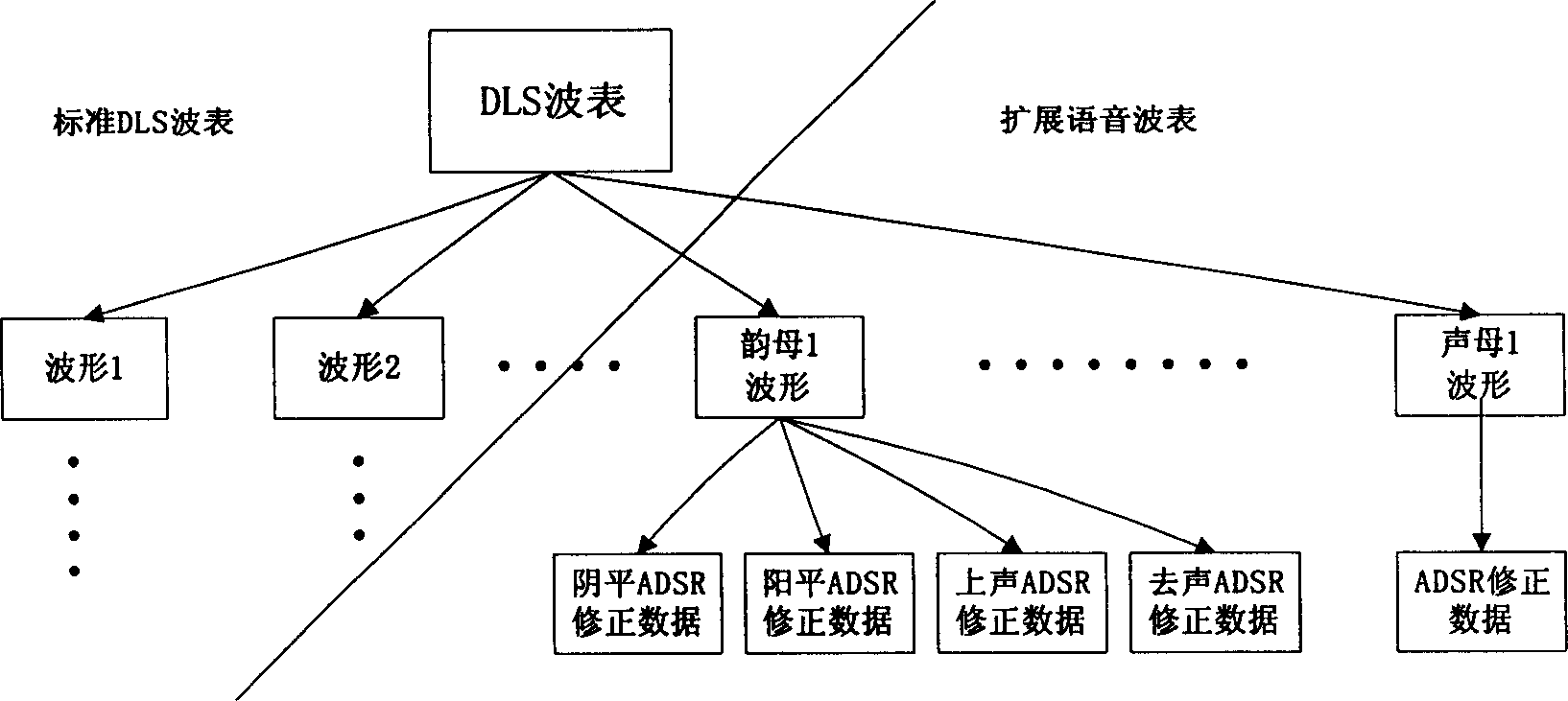

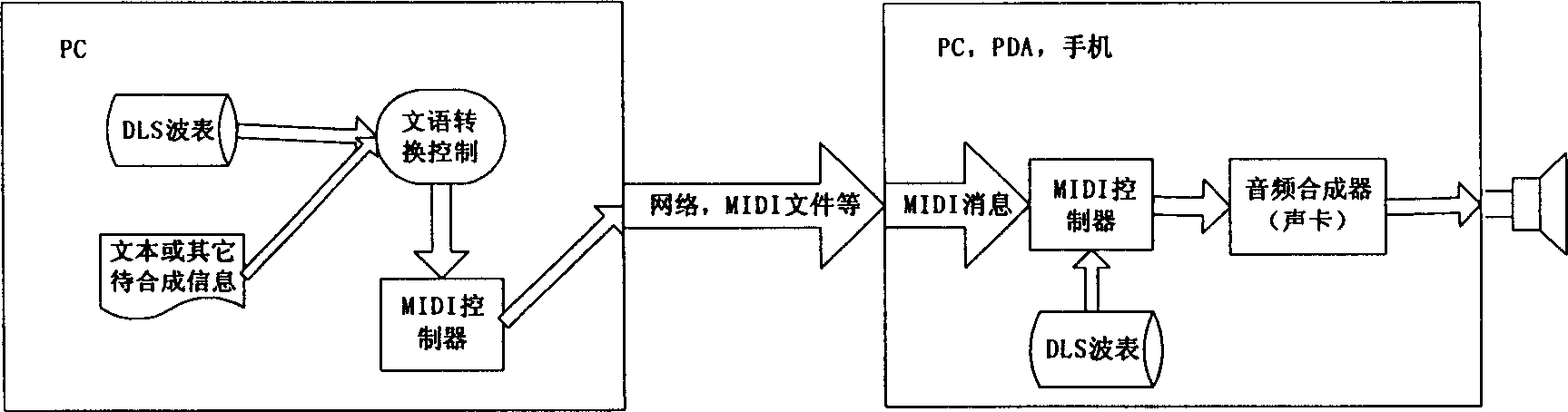

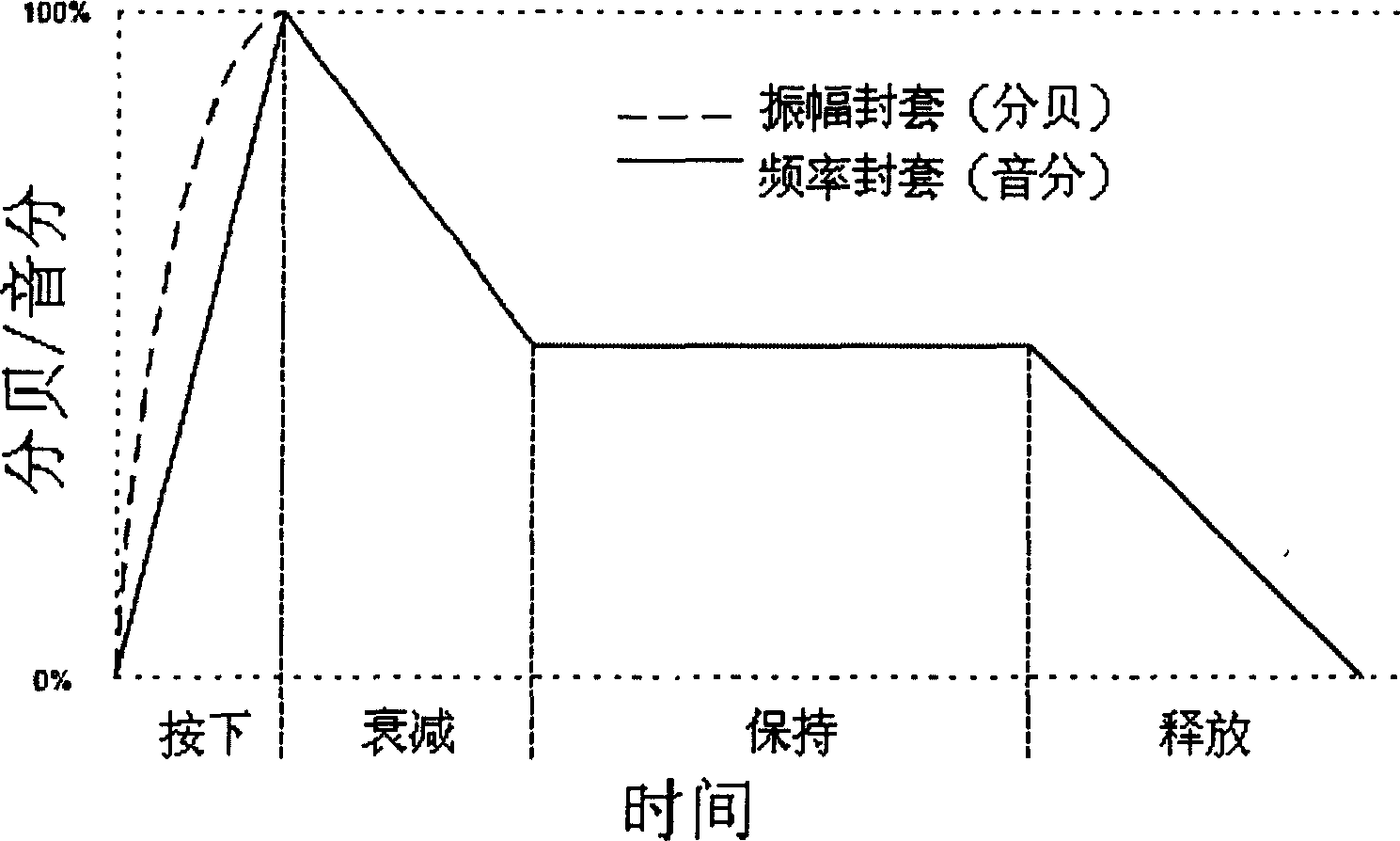

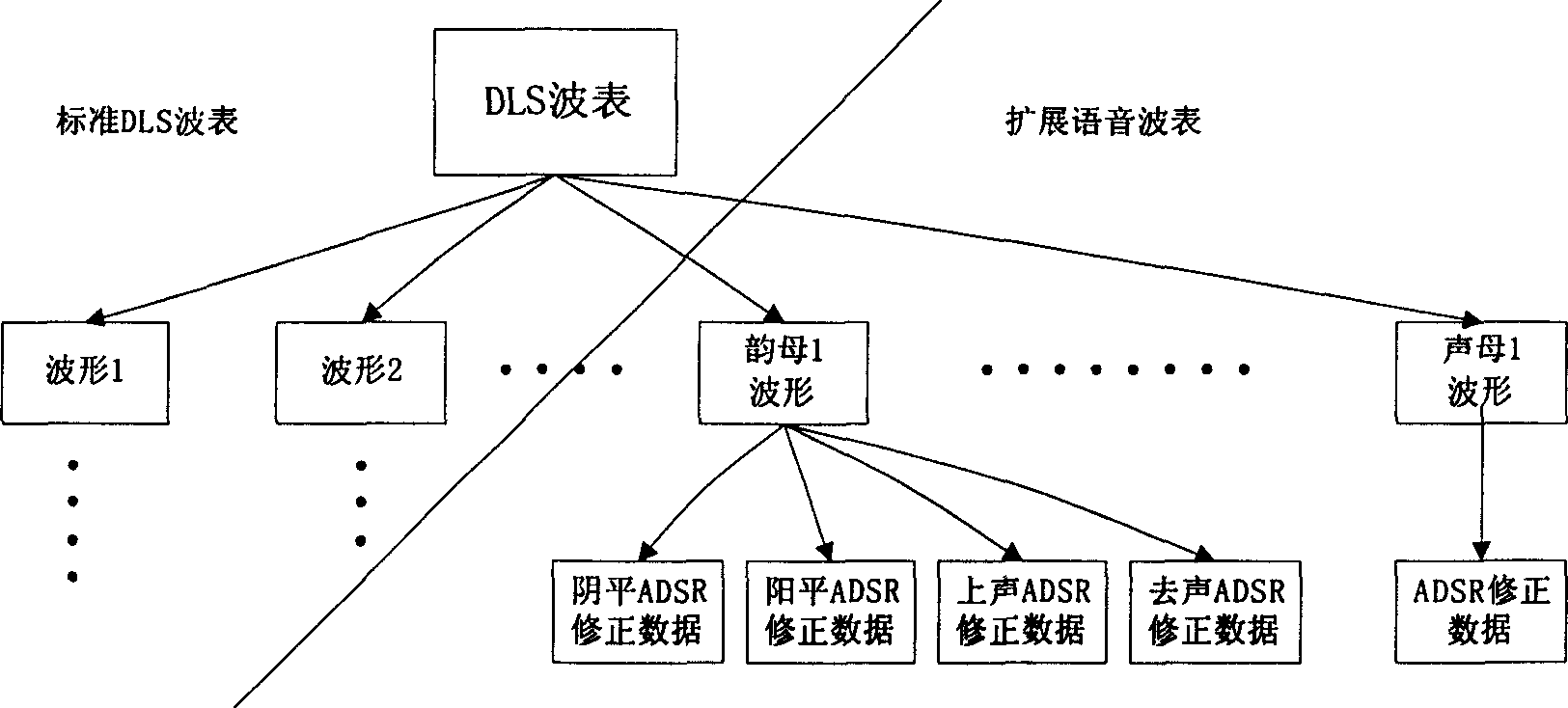

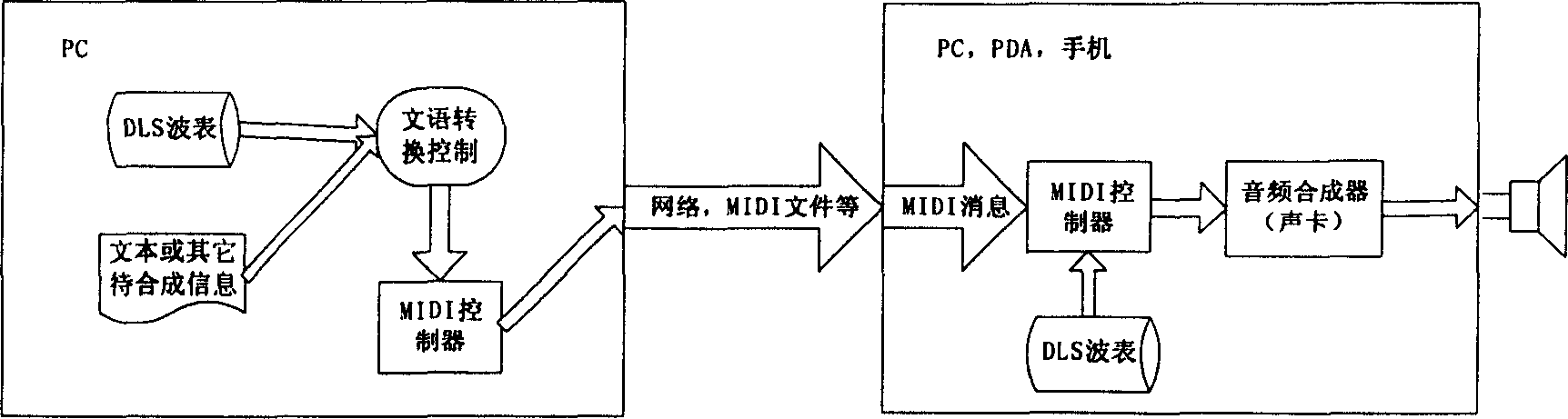

Chinese voice synthesis method based on music instrument digital interface algorithm

InactiveCN1487499AGuaranteed portabilityGuaranteed scalabilitySpeech synthesisExtensibilityChinese characters

The present invention is one kind of Chinese voice synthesis method based on MIDI algorithm. The method includes establishing waveform library via storing Chinese voice including 23 initial consonants and 34 vowels in DLS wavetable, attaching the waveform library to the tail of the standard DLS wavetable, performing ADSR correction to vowels, converting text first into spelling and then into MIDI message, and final synthesizing Chinese character voice via sound card or other MIDI backing-up player. The present invention can compress greatly the memory space, reduce operation amount and save system cost, and has excellent porting performance and expandability.

Owner:FUDAN UNIV

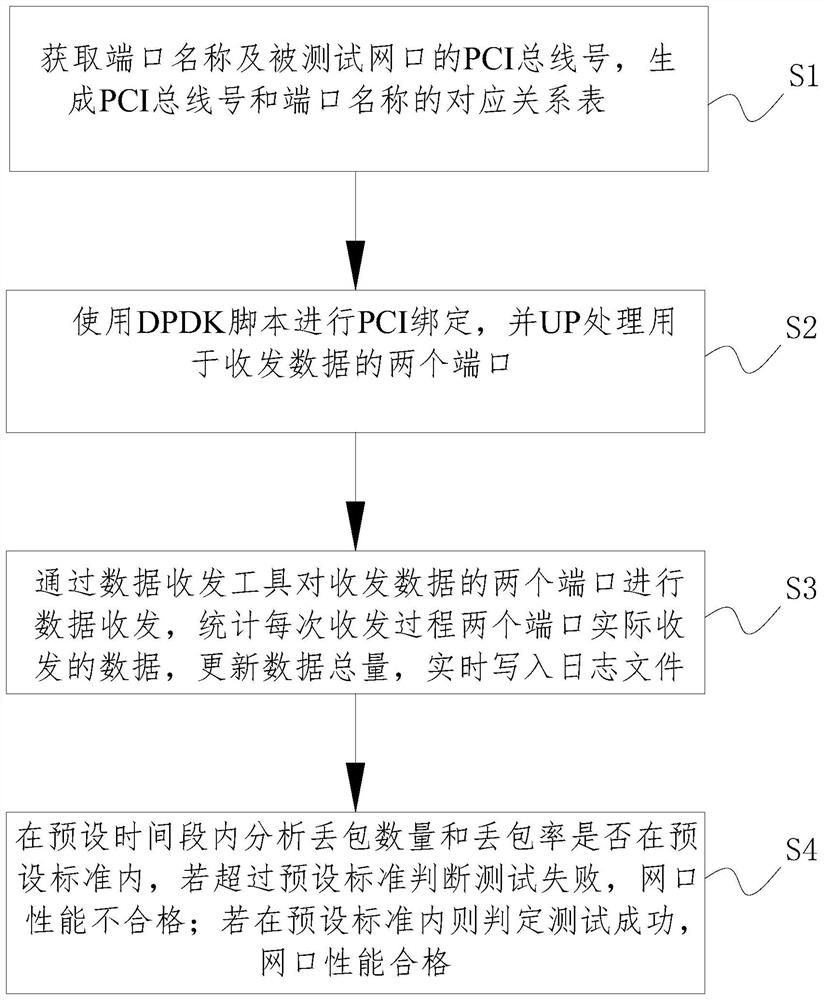

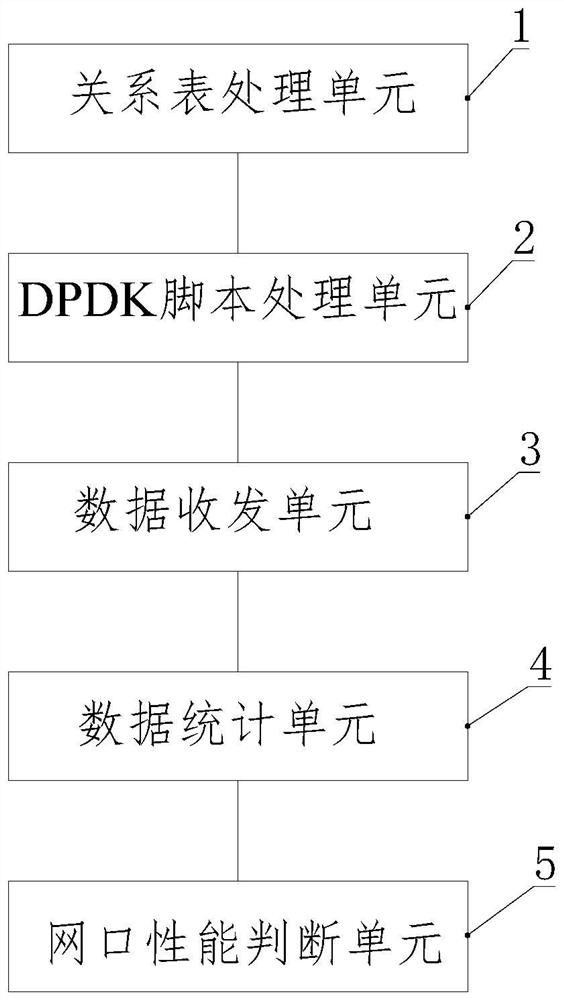

X86 platform network port performance test method and device based on DPDK technology

PendingCN114301808AImprove test efficiencyRealize data sending and receivingTransmissionDatabase modelsTest efficiencyPacket loss rate

The invention discloses an X86 platform network port performance test method and device based on a DPDK technology, and the method comprises the steps: obtaining a port name and a PCI bus number of a tested network port, and generating a corresponding relation table of the PCI bus number and the port name; performing PCI binding by using a DPDK script, and performing UP processing on two ports for receiving and transmitting data; performing data receiving and transmitting on two ports for receiving and transmitting data through a data receiving and transmitting tool, counting data actually received and transmitted by the two ports in each receiving and transmitting process, updating the total amount of the data, and writing the data into a log file in real time; analyzing whether the packet loss quantity and the packet loss rate are in a preset standard in a preset time period, and if the packet loss quantity and the packet loss rate exceed the preset standard, judging that the test fails and the network port performance is unqualified; and if yes, determining that the test is successful and the network port performance is qualified. According to the method, the flow, the success rate and the packet loss rate of the two ports in a period of time can be automatically counted, the test efficiency of the network port function is greatly improved, and a sufficient basis is provided for the network port performance.

Owner:BEIJING GEMOTECH INTELLIGENT TECH

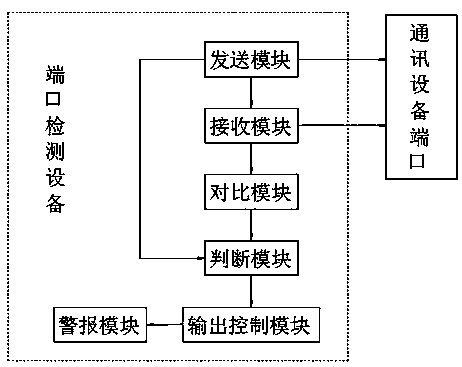

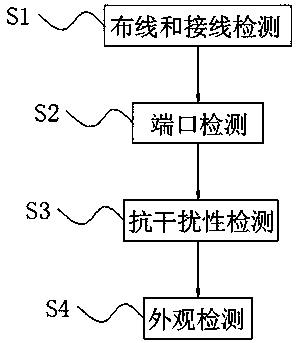

Leaving-factory detection device based on communication equipment production and detection method thereof

InactiveCN109586809AStrengthen supervisionThe detection method is simpleTransmitters monitoringReceivers monitoringComputer scienceProduction quality

The invention discloses a leaving-factory detection device based on communication equipment production and a detection method thereof, which relate to the technical field of communication equipment production. The leaving-factory detection device based on communication equipment production comprises a port detection device and anti-interference detection device. The detection method comprises thefollowing steps of S1, wire arrangement and wire connection detection, S2, port detection, S3, anti-interference detection and S4, appearance detection. Wire arrangement, wire connection, port performance and anti-interference performance of leaving-factory communication equipment can be detected, supervision on the production quality of the communication equipment is further enhanced, the detection method of the detection device is simple, detection alone can be realized, a computer does not need to be used, the occupied resources are few, the cost is low, the operation is simple, the time isshort, and the efficiency is high.

Owner:湖南宸睿通信科技有限公司

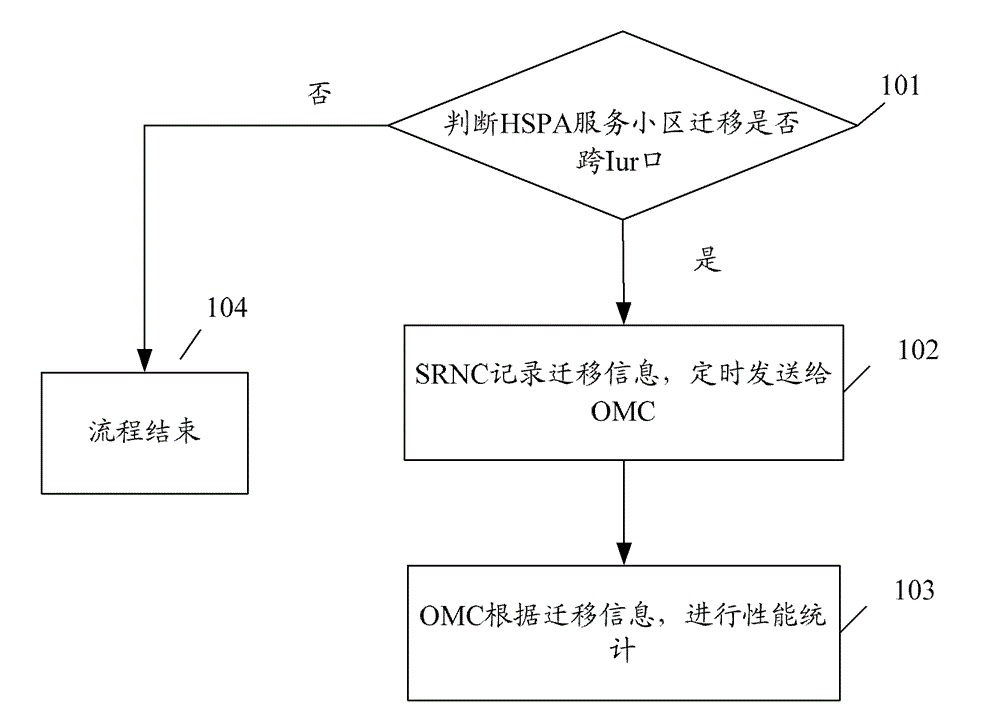

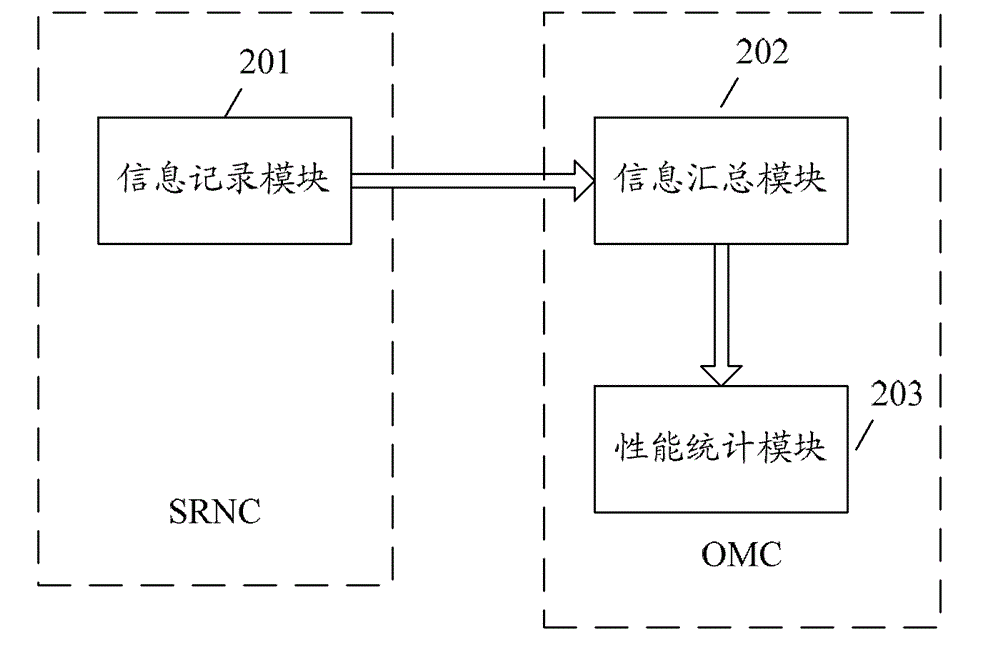

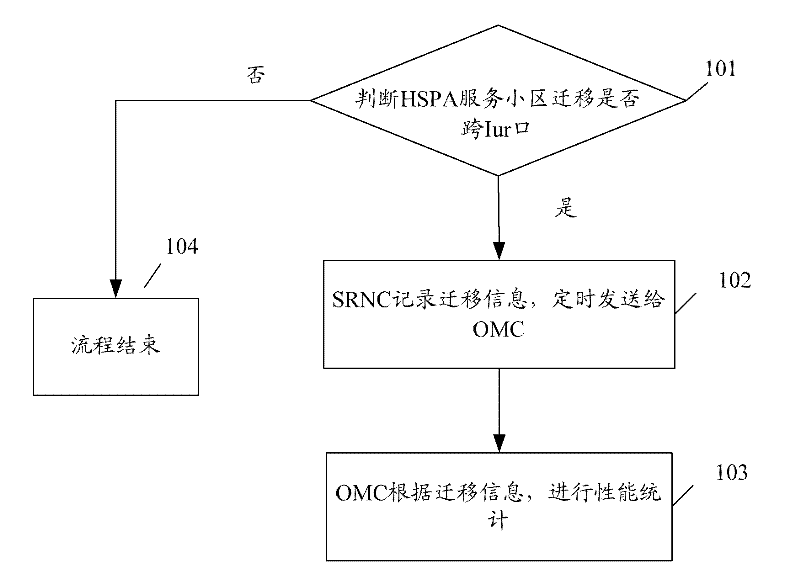

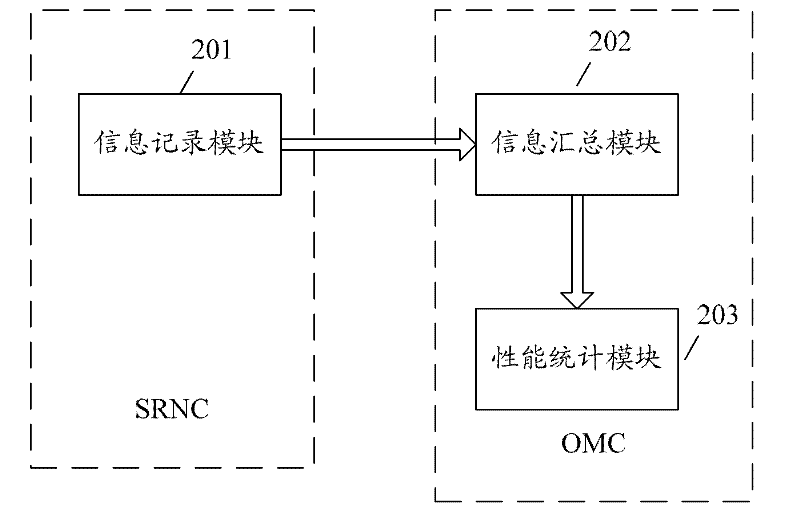

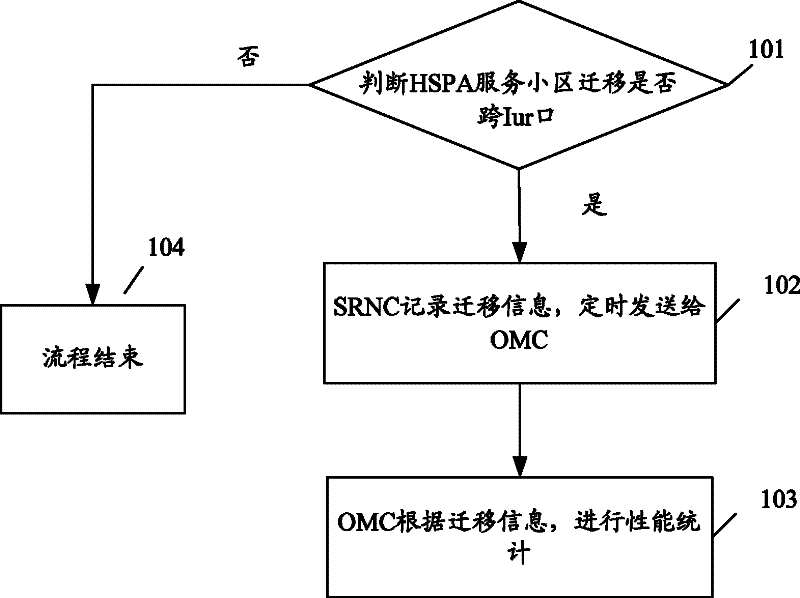

Iur-crossing port performance management method and system

InactiveCN102651880BEasy to analyzeEasy maintenanceWireless communicationHigh Speed Packet AccessRadio Network Controller

The invention discloses an Iur-crossing port performance management method and system. The method comprises the steps as follows: a service radio network controller (SRNC) determines the migration Iur-crossing port of an HSPA (High Speed Packet Access) service cell, records and regularly transmits migration information to an OMC (Operation Maintenance Center) during migration process; and the OMC regularly summarizes the migration information, carries out performance management, and acquires a management result. The invention also discloses the Iur-crossing port performance management system. The method and system with the performances is favorable for an operator to analyze the performance of the system, and maintain and improve a network.

Owner:ZTE CORP

Method and system for port performance ranking in multi-protocol switch

A system and method for port performance ranking in a multi-protocol switch includes monitoring one or more first parameters, the one or more first parameters associated with operating condition of one or more ports of the multi-protocol switch. Each of the one or more first parameters is compared with an associated predefined criterion to determine deviation from the associated predefined criterion. One or more eligible ports is determined from the one or more ports based on non-deviation of each of the one or more first parameters from the associated predefined criterion. For each of the one or more eligible ports, each of one or more second parameters is compared with an associated predefined threshold, the one or more second parameters associated with port traffic statistics. The one or more eligible ports are ranked based on the comparison between each of the second parameters and the associated predefined threshold.

Owner:PALO ALTO NETWORKS INC

Chinese voice synthesis method based on music instrument digital interface algorithm

The present invention is one kind of Chinese voice synthesis method based on MIDI algorithm. The method includes establishing waveform library via storing Chinese voice including 23 initial consonants and 34 vowels in DLS wavetable, attaching the waveform library to the tail of the standard DLS wavetable, performing ADSR correction to vowels, converting text first into spelling and then into MIDI message, and final synthesizing Chinese character voice via sound card or other MIDI backing-up player. The present invention can compress greatly the memory space, reduce operation amount and save system cost, and has excellent porting performance and expandability.

Owner:FUDAN UNIV

Iur-crossing port performance management method and system

InactiveCN102651880AEasy to analyzeEasy maintenanceWireless communicationNetwork controlHigh Speed Packet Access

The invention discloses an Iur-crossing port performance management method and system. The method comprises the steps as follows: a service radio network controller (SRNC) determines the migration Iur-crossing port of an HSPA (High Speed Packet Access) service cell, records and regularly transmits migration information to an OMC (Operation Maintenance Center) during migration process; and the OMC regularly summarizes the migration information, carries out performance management, and acquires a management result. The invention also discloses the Iur-crossing port performance management system. The method and system with the performances is favorable for an operator to analyze the performance of the system, and maintain and improve a network.

Owner:ZTE CORP

Compact terahertz power synthesis frequency multiplier circuit

ActiveCN102969976BCompact structureHighly integratedOscillations generatorsCapacitanceFrequency multiplier

The invention discloses a compact terahertz power synthesis frequency multiplier circuit which comprises an upper metal substrate and a lower metal substrate, wherein a cavity formed by the upper and lower metal substrates is internally provided with an input waveguide structure, a synthesizing channel, an output waveguide structure and a direct current biasing circuit which are in the same structure, respectively, wherein one end of the synthesizing channel is connected with the input waveguide structure while the other end of the synthesizing channel is connected to the output waveguide structure; the synthesizing channel is internally provided with two thin film chips symmetrical in mirror; and one group of the thin film chips is connected to the upper metal substrate while the other group of the thin film chips is connected to the lower metal substrate. The direct current biasing circuit is provided with chip capacitors connected with the thin film chips. Based on a micro / nano technology, the compact terahertz power synthesis frequency multiplier circuit has the characteristics of compact structure and high integrating degree. The compact terahertz power synthesis frequency multiplier circuit has the characteristics of good port performance and higher power. The compact terahertz power synthesis frequency multiplier circuit has the characteristics of low cost and good consistency and is convenient for large-scale production.

Owner:SOUTHEAST UNIV

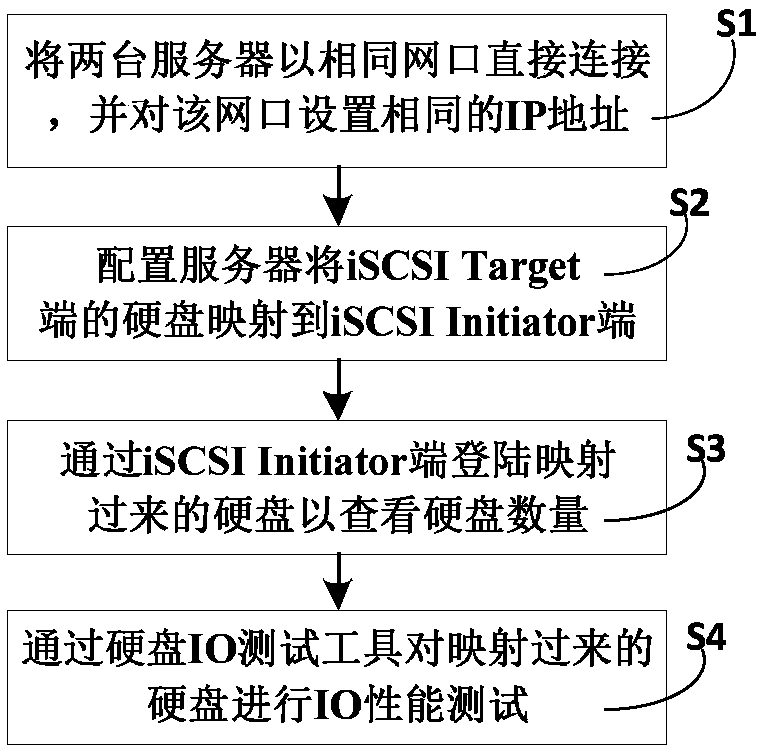

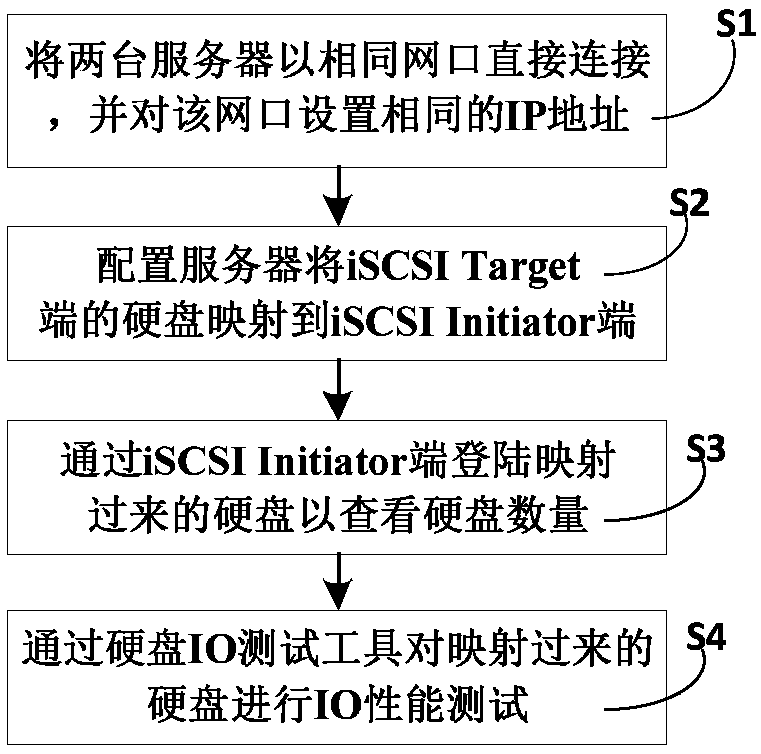

A network port performance testing method and system of a server under a Linux system

ActiveCN106055441BSimple test methodEasy to compareDetecting faulty computer hardwareComputer hardwareGNU/Linux

The invention provides an internet access performance testing method and system of servers under a linux system. The internet access performance testing method comprises the following steps: step S1, directly connecting two servers with the same internet access, and setting the same network segment IP address for the internet access; step S2, configuring the server to map the hard disk at the iSISC Target terminal to the iSCSI Initiator terminal; step S3, logging to the iSCSI Initiator terminal mapped hard disk through the iSCSI Initiator end so as to check the hard disk number; step S4, performing IO performance testing on the mapped hard disk through a hard disk IP testing tool. The testing method provided by the invention is simple, the result is visual and easy to compare, and the internet access IO performance is directly reflected through the hard disk IO performance, the performance states of the internet access in actual use under different scenes can be simulated, and the targeted testing can be performed according to actual demand.

Owner:SHENZHEN TONGTAIYI INFORMATION TECH CO LTD

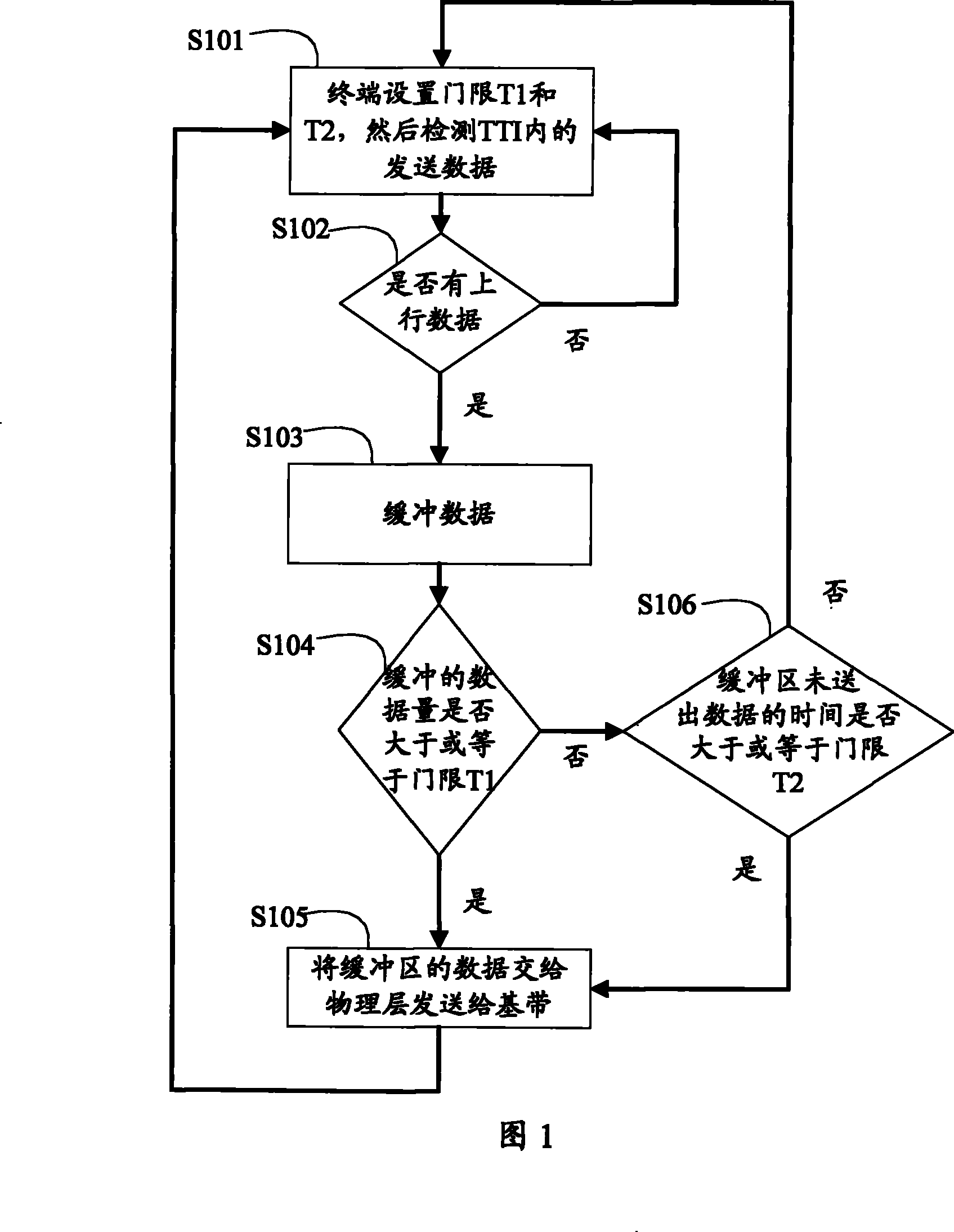

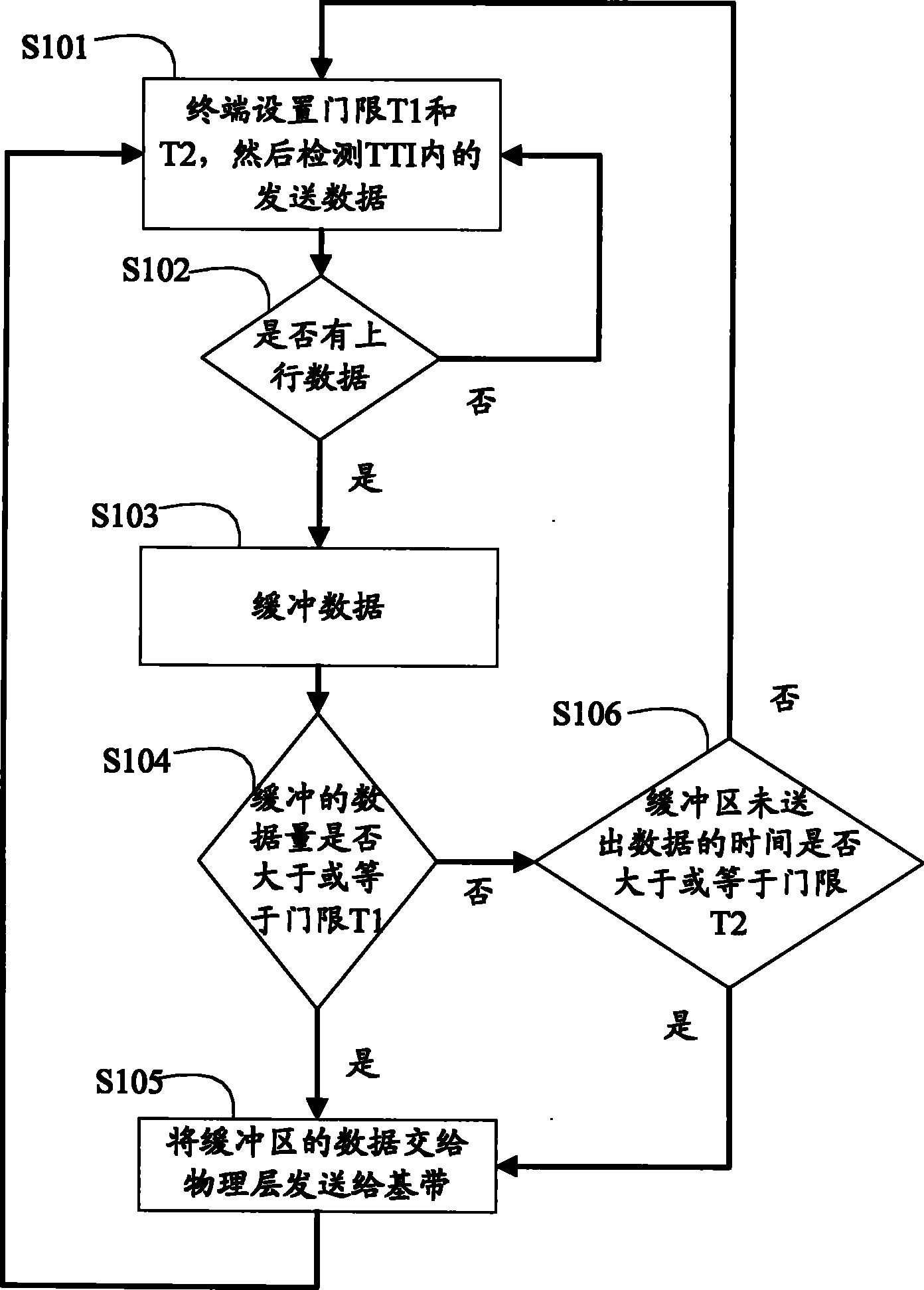

Electricity saving method for TD-SCDMA terminal

The invention discloses a power-saving method for time-division synchronous code-division multi-access terminals. The method comprises the following steps: (1) a threshold is arranged on a time-division synchronous code-division multi-access terminal; (2) the time-division synchronous code-division multi-access terminal caches uplink original data, and when the cached uplink original data reachesthe threshold, the cached uplink original data is sent to a baseband. The method caches data between an original rate source and the baseband so as to complete expected rate adjustment, and can obtain effects of saving power and improving empty-port performance.

Owner:ZTE CORP

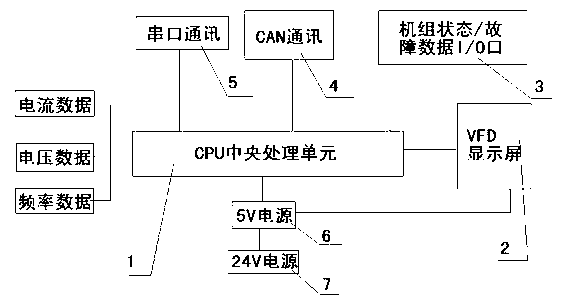

Comprehensive displaying device

InactiveCN103165060AHigh display accuracyGood communication transmission effectStatic indicating devicesLow voltageDisplay device

The invention relates to a comprehensive displaying device which comprises a CPU. A VFD displaying screen is connected with a displaying end of the CPU. The VFD displaying screen is connected with a low-voltage power supply. An output end of the low-voltage power supply is connected with the CPU. An input end of the low-voltage power supply is connected with a high-voltage power supply. The CPU is connected with a unit state / stoppage data I / O port, a CAN communication end and a serial port communication end. Current data, voltage data and frequency data which are detected are processed by the CPU and displayed through the VFD displaying screen. Meanwhile, the CPU can exchange data with other equipment through the serial communication end, the CAN communication end and the unit state / stoppage data I / O port. The comprehensive displaying device has the advantages of being high in displaying precision, low in energy consumption, high in port performance and long in service life.

Owner:XIAN LONGDE TECH

A port performance statistics system

ActiveCN107465579BReduce load pressureEasy statisticsData switching networksEngineeringReal-time computing

The invention discloses a port performance statistics system. The system includes: a user layer, a platform interface layer and a performance statistics module. The platform interface layer is respectively connected with the user layer and the performance statistics module, wherein the platform interface layer is used to obtain the The first time value of arriving at the target port and entering the queue; determining the current number of IOs in the queue when assigned to a thread; obtaining the second time value of each IO leaving the target port after being processed by the storage terminal; determining each time delay; and the current number of IOs are sent to the performance statistics module; the performance statistics module is used to count the port performance of the target port, and the port performance includes: the average delay of the target port; the real-time number of IOs in the queue. By using the port performance statistics system provided by the embodiment of the present invention, the port performance of the target port is counted in the platform interface layer and the performance statistics module, which reduces the load pressure on the driver layer, makes the statistics simple, and the statistical results are more accurate.

Owner:INSPUR SUZHOU INTELLIGENT TECH CO LTD