Stack architecture of multiple chips

A stack structure, multi-chip technology, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problems of increasing the projected area, violating the requirements of small size and multi-functional characteristics of electronic products, affecting the area of electronic products, etc. Number, effect of promoting convenience

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

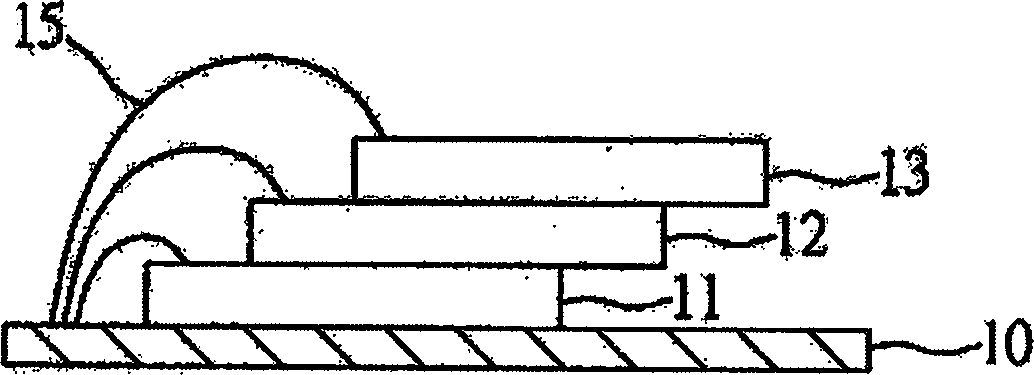

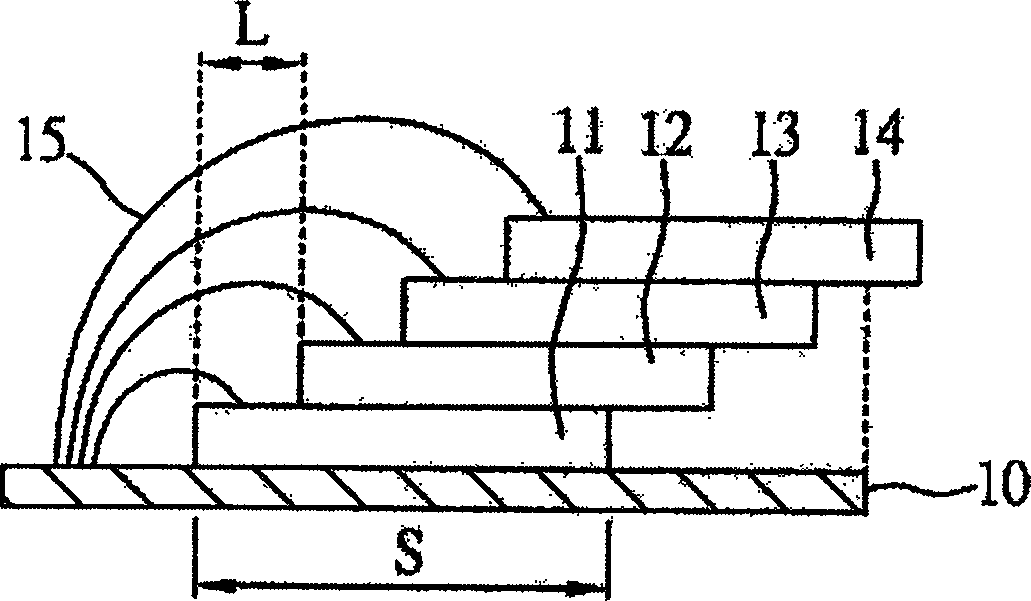

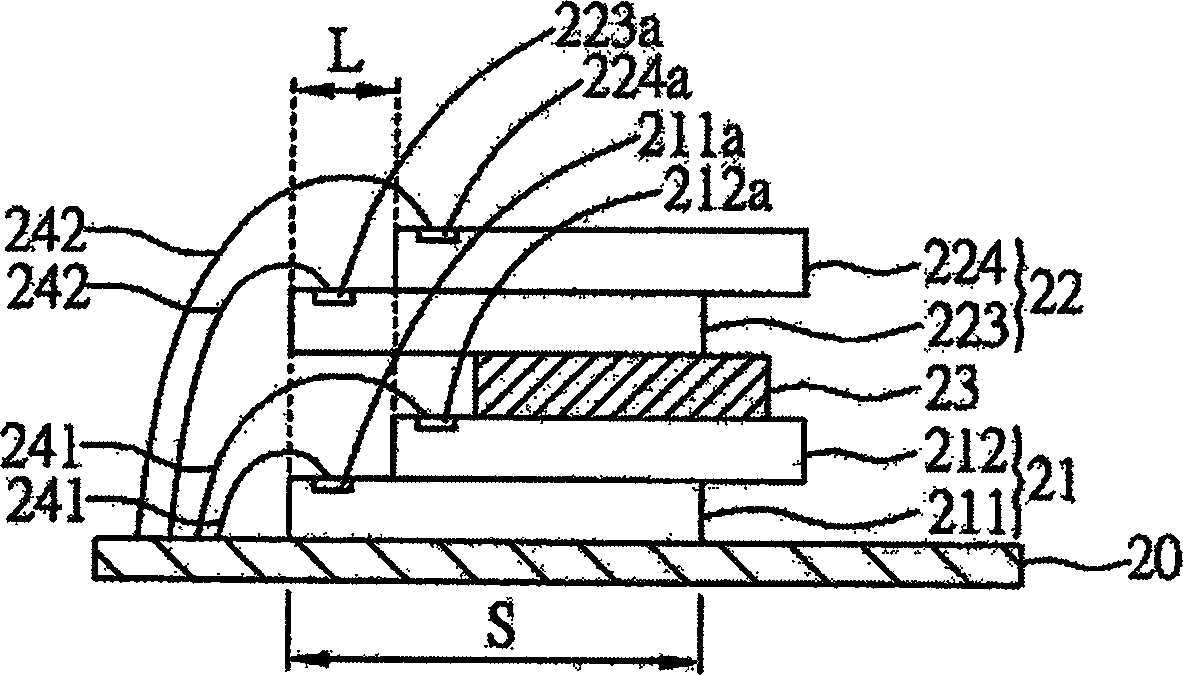

[0019] The implementation of the present invention will be described below through specific specific examples. The following drawings only show the components related to the present invention, and are not drawn according to the number, shape and size of the components in actual implementation. More complex.

[0020] figure 2 It is a schematic cross-sectional view of the multi-chip stack structure of the present invention.

[0021] The multi-chip stack structure includes: a chip carrier 20 , a first chip set 21 , a buffer 23 and a second chip set 22 . Wherein, the first chipset 21 has a plurality of chips, and these chips have single side pads and are stacked on the chip carrier 20 in a ladder shape, and the pads are exposed; the buffer member 23 is connected to the first chip on the group 21; the second chip group 22 has a plurality of chips, these chips have single-side pads and are stacked on the buffer member 23 in a ladder shape, and the bottom chip of the second chip ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More