Automated overlay metrology system

a metrology system and overlay technology, applied in semiconductor/solid-state device testing/measurement, semiconductor/solid-state device details, instruments, etc., can solve the problems of reducing the minimum feature size, reducing the manufacturing yield, and expensive sem or afm tools

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

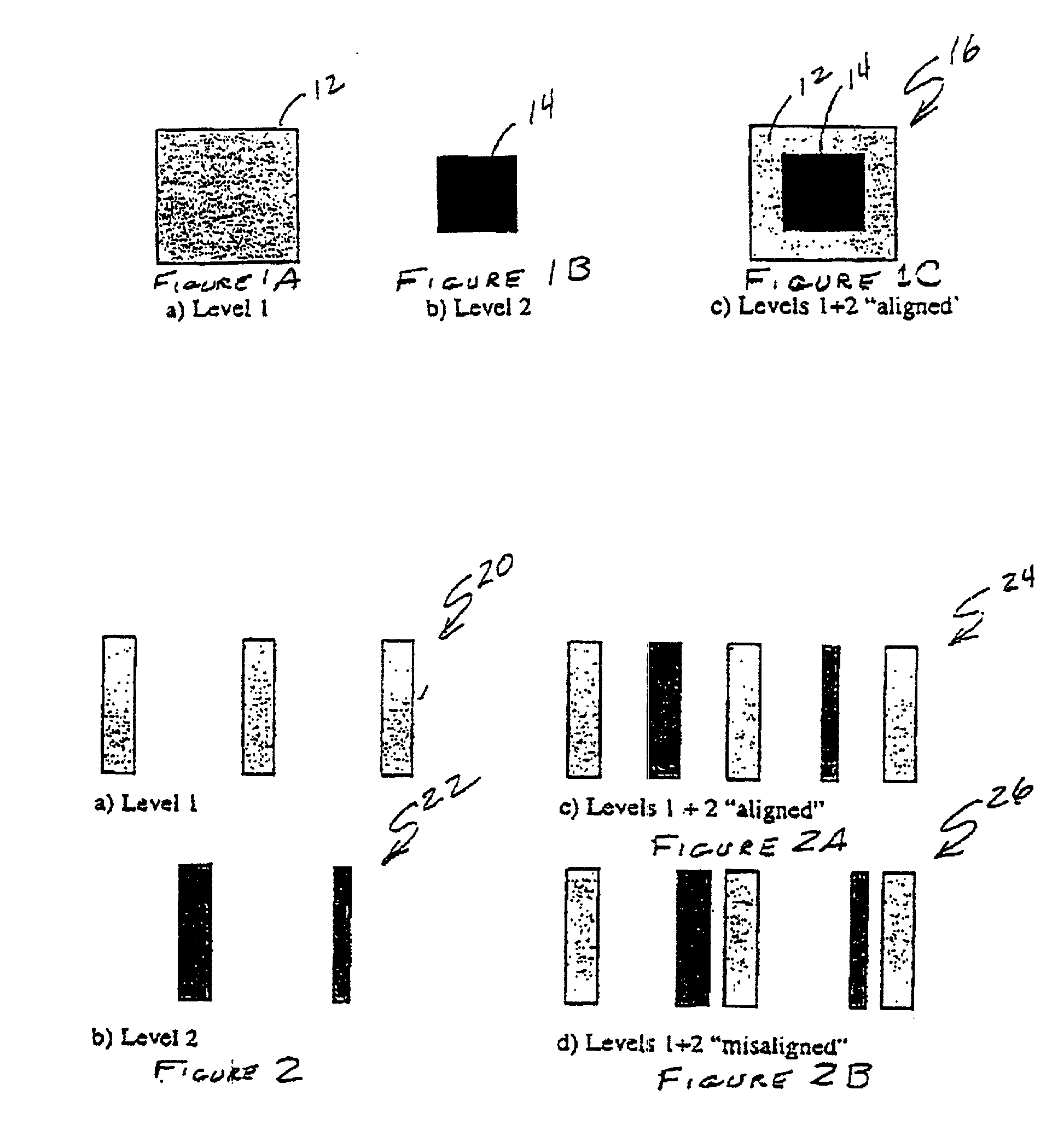

[0028] Referring now to the drawings, and more particularly to FIGS. 1A, 1B and 1C, there is shown a typical box-in-box metrology feature exemplary of features for such purposes known and used in the art. The box-in-box feature 16 shown in FIG. 1C is a composite feature formed by two overlaid lithographic exposures corresponding respectively to features 12 and 24 of FIGS. 1A and 1B, respectively, which are generally sequentially performed and each preceded by deposition of a layer of resist and followed by development of resist layer and possibly including etching or material deposition processes between the lithographic exposures. One feature will be larger than the other and the smaller feature should be of dimensions which, ideally, closely approach the minimum feature size of interest.

[0029] At the present state of the art, however, the smaller and larger features are generally produced with a transverse dimension of the order of a few microns. Such dimensions are about an order...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More