Apparatus for variable word length computing in an array processor

an array processor and variable word technology, applied in the direction of program control, multi-processor architecture, instruments, etc., can solve the problems of complex design of modern microprocessors, one task, and tasks to which they are not well suited, so as to achieve dynamically alter the effect of effective arrangement of processing elements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

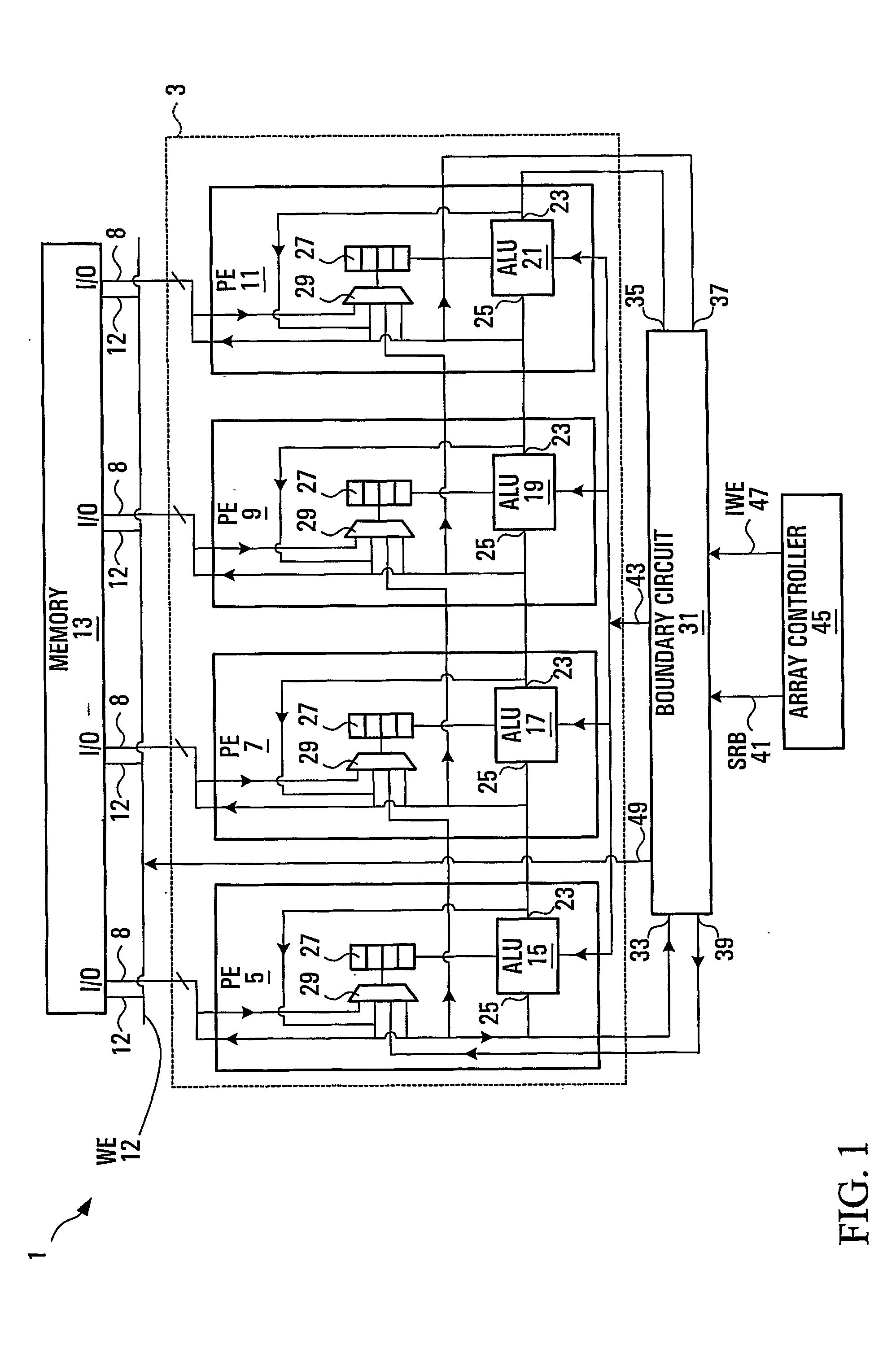

[0027] FIG. 1 shows a data processor according to an embodiment of the present invention. The data processor 1 comprises a computational unit 3 having a plurality of SIMD based processing elements 5, 7, 9, 11, each of which has access to a memory 13. Each processor element 5, 7, 9, 11 has an arithmetic logic unit (ALU) 15, 17, 19, 21 each having an input port 23 and an output port 25. The input port 23 of each ALU is directly coupled to the output port of the neighboring ALU to its right to enable data (e.g. a bit) to propagate from the output 25 to the input 23 of adjacent ALUs. Each processor element further comprises one or more registers 27 and a multiplexer 29 for switchably coupling one or more of a plurality of inputs to a register. In this embodiment, inputs to the multiplexer include the output from its local ALU, the outputs from its neighboring ALUs to its left and right, and an output from the memory 13.

[0028] The data processor 1 has a control circuit 31 (which is also ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More