Semiconductor nano-rod devices

a technology of semiconductors and nanorods, applied in the direction of transistors, solid-state devices, nanoinformatics, etc., can solve the problems of parasitic off-state leakage, gate oxide thickness, gate oxide thickness, etc., and achieve the effect of reducing the number of transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The use of presently preferred embodiments are discussed in detail below. It should be appreciated, however, that the present invention provides many applicable inventive concepts that can be embodied in a wide variety of specific contexts. The specific embodiments discussed are merely illustrative of specific ways to make and use the invention, and do not limit the scope of the invention.

[0018] Example embodiments of the present invention will be described herein in a specific context of making semiconductor devices, such as transistors. In other embodiments not shown, embodiments of the present invention also may include nano-wires or quantum-wires formed in accordance with the present invention. The present invention may also be applied, however, to other situations.

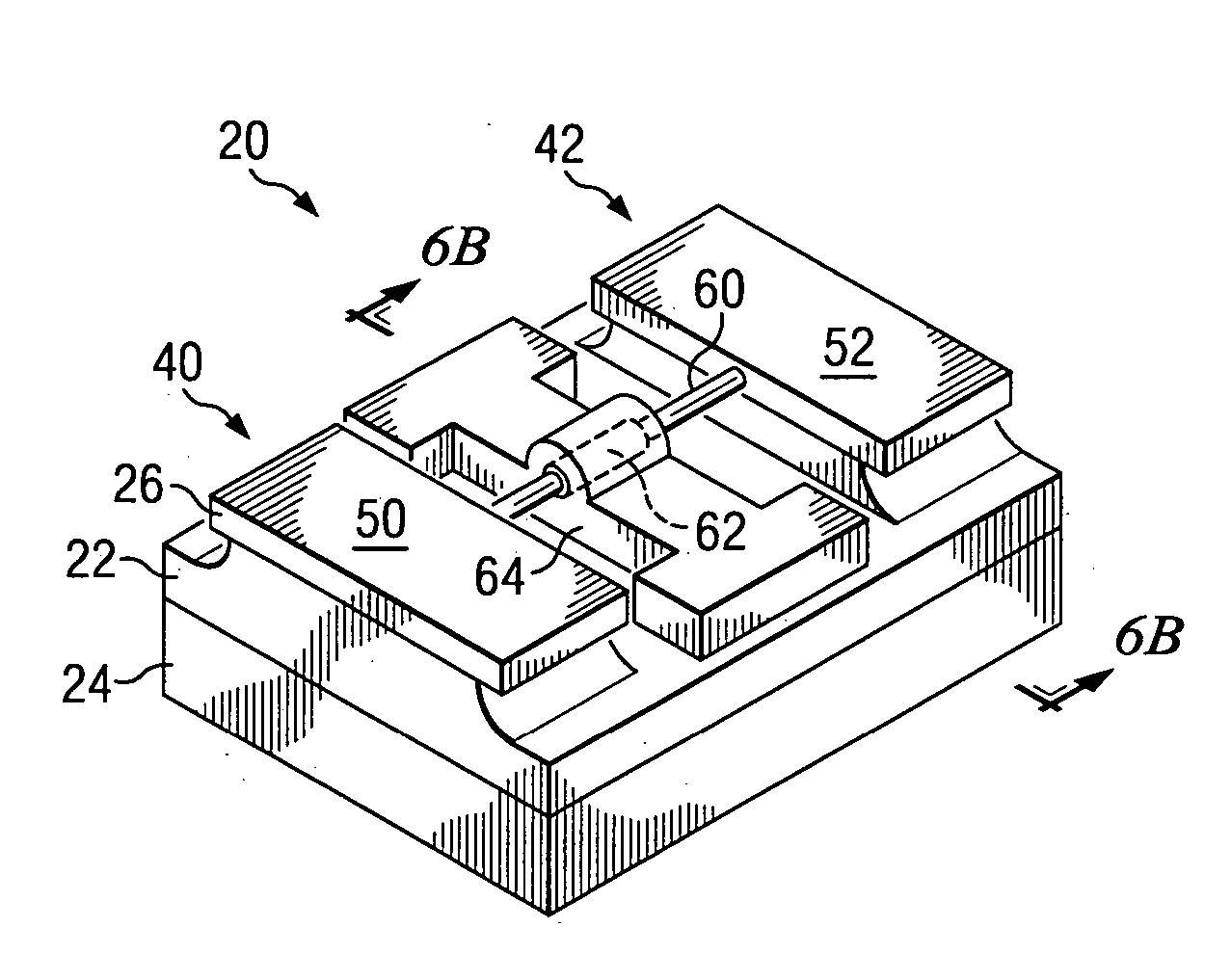

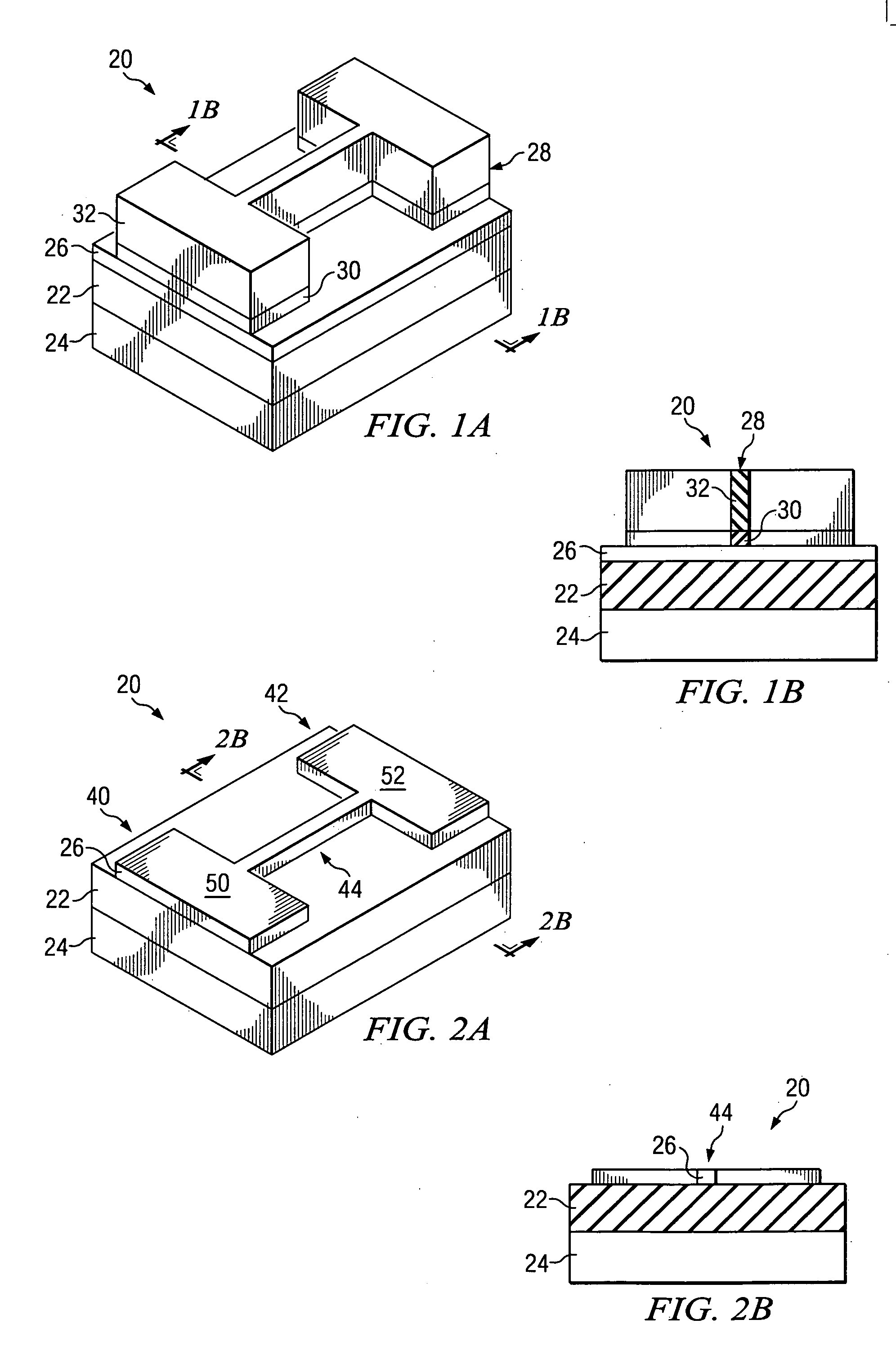

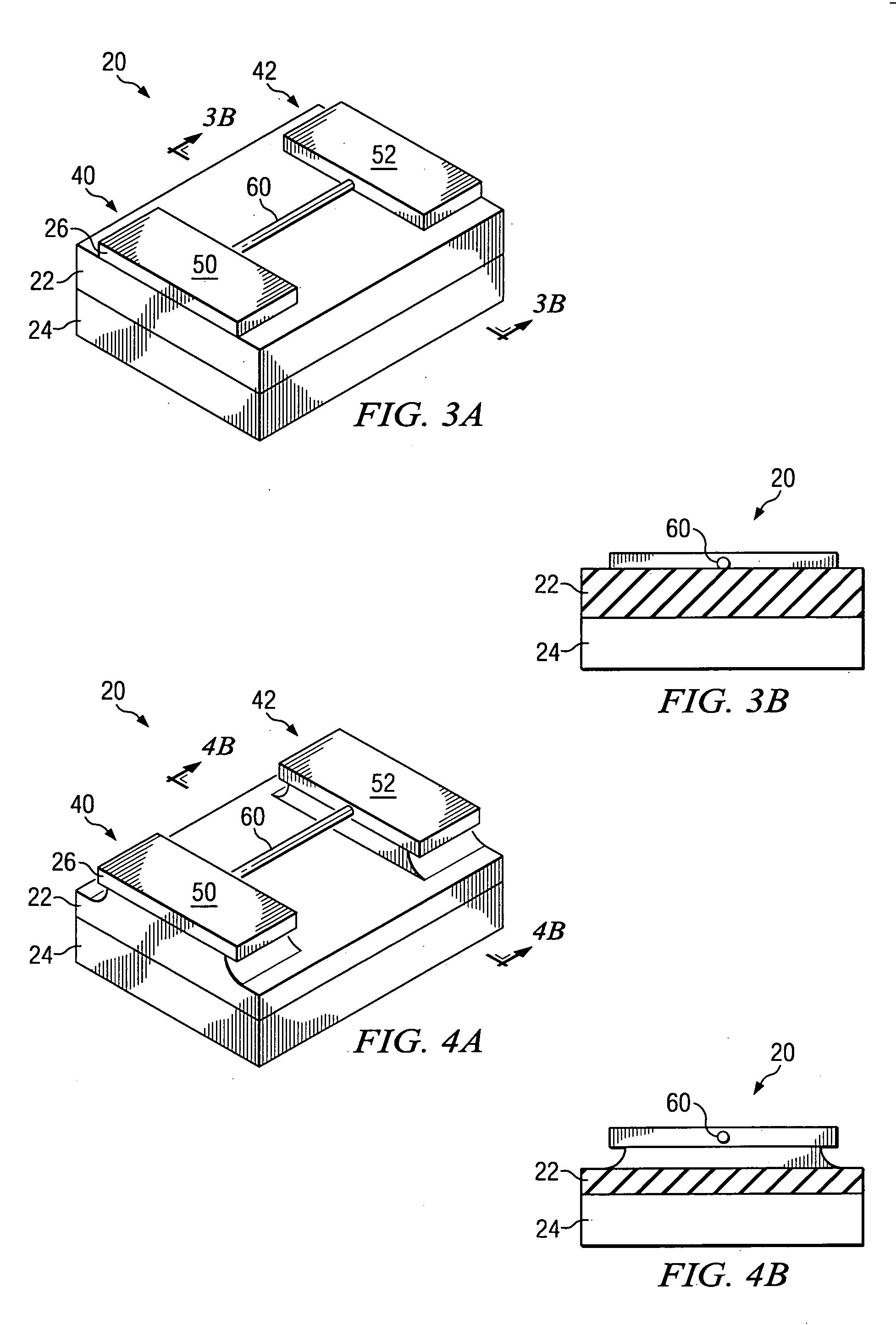

[0019] A preferred manufacturing process in accordance with the present invention may be used to make a transistor device. Some of the manufacturing steps of this preferred embodiment being used to make a tra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More