Semiconductor device having vertical metal insulator semiconductor transistors having plural spatially overlapping regions of different conductivity type

a technology of vertical metal insulator and semiconductor transistor, which is applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical equipment, etc., can solve the problems of reducing on resistance, forming fine structures, and depleting the pillar layers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

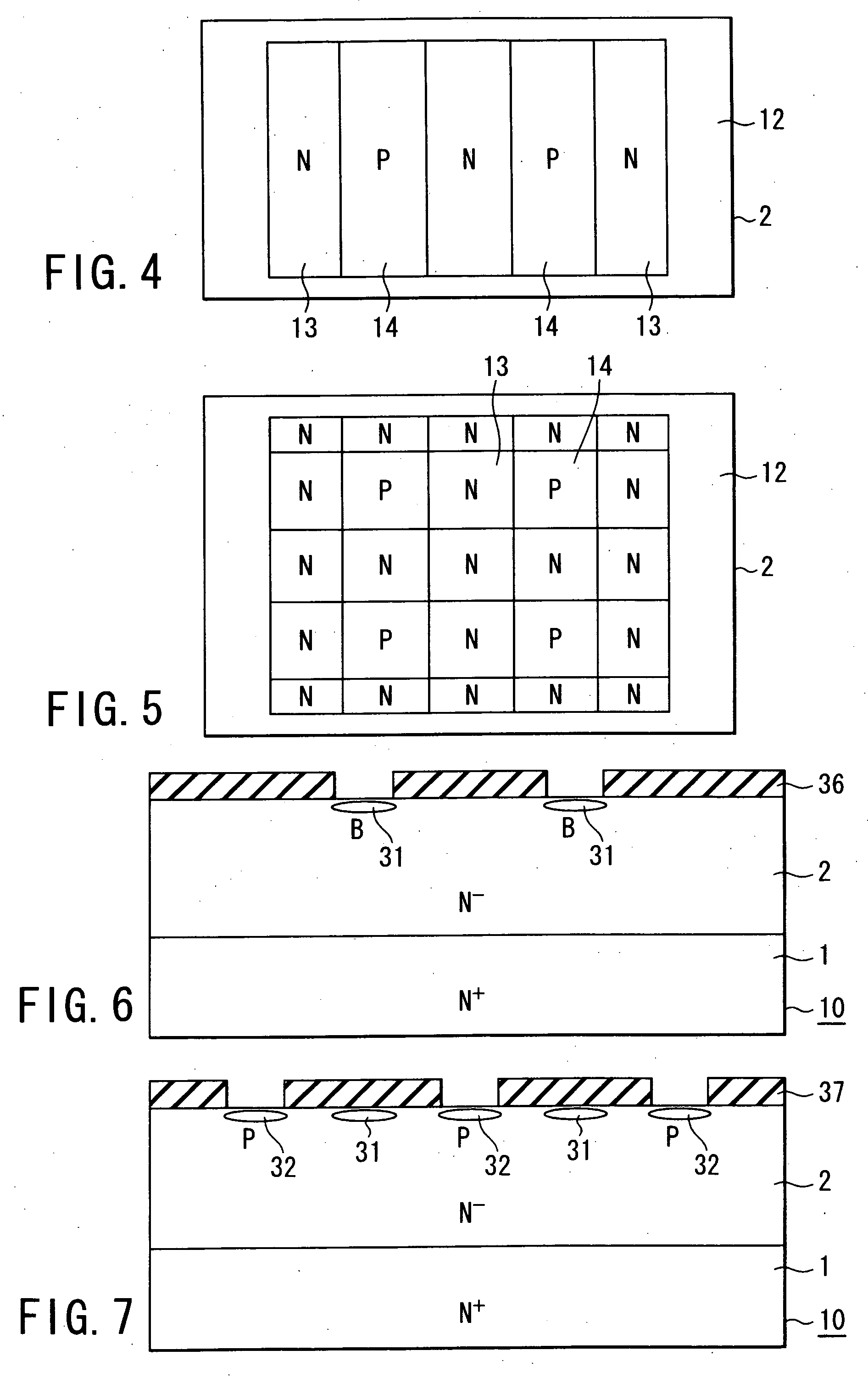

[0044] A first embodiment will be described with reference to FIGS. 1 to 12.

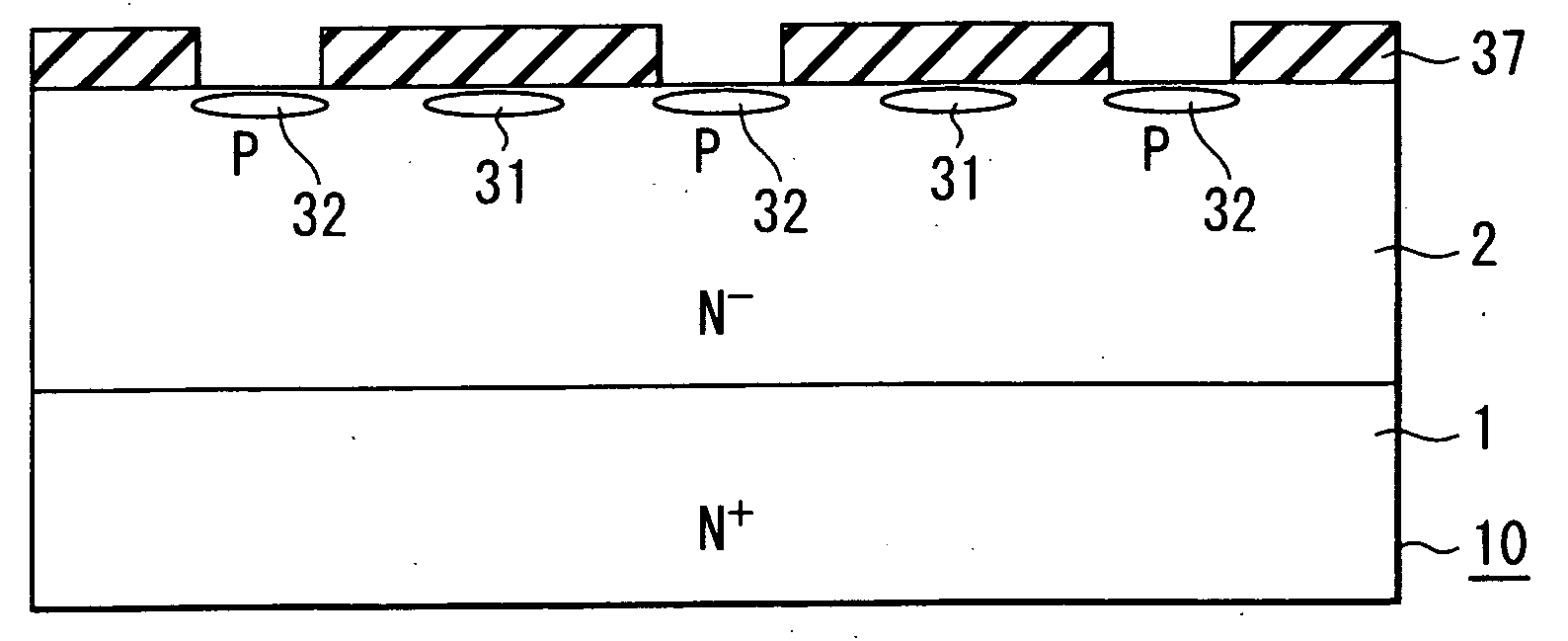

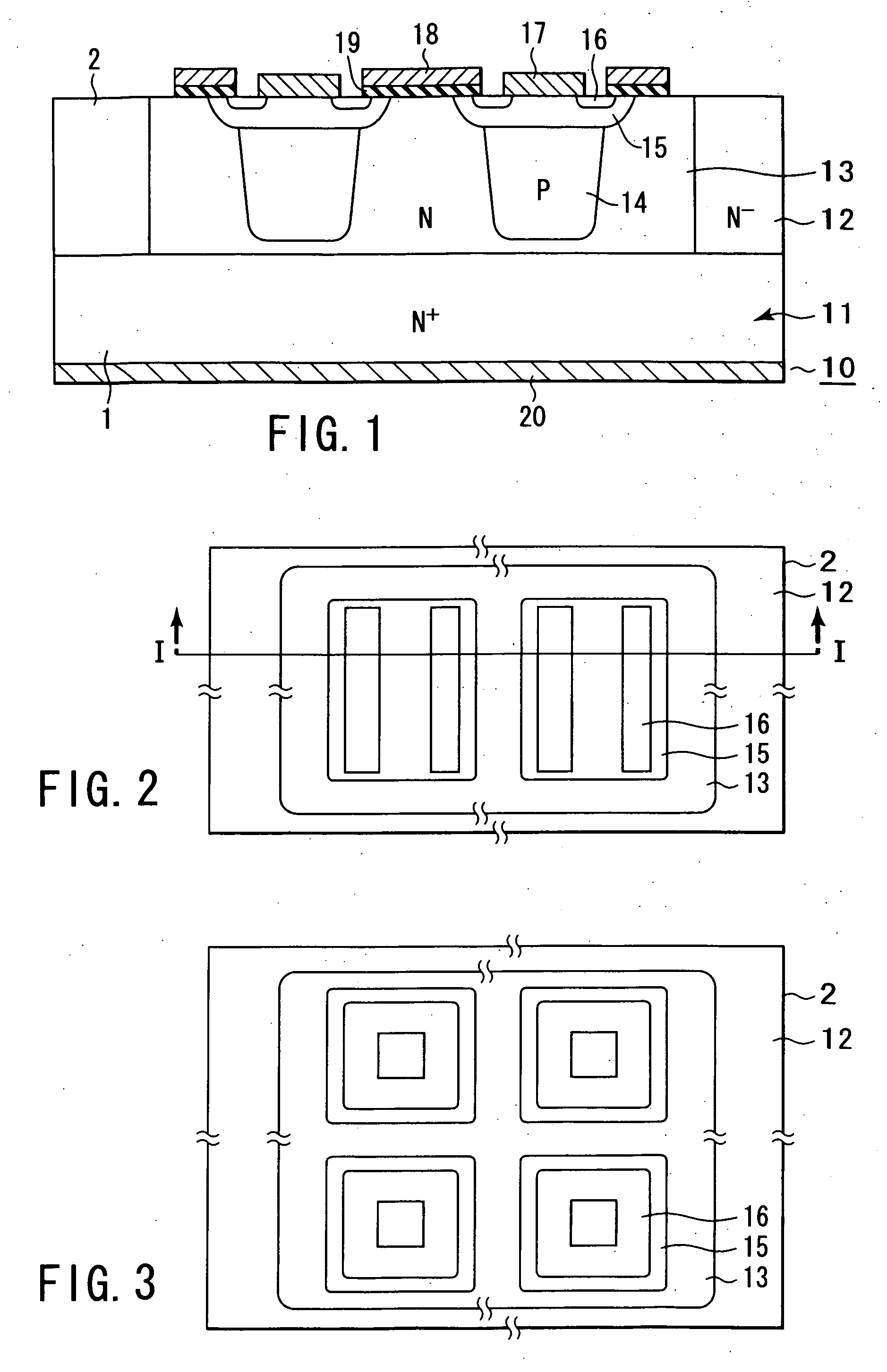

[0045]FIG. 1 is a diagram showing the sectional structure of a semiconductor device according to the first embodiment of the present invention. This semiconductor device is a vertical MISFET in which PN junctions are formed to extend in a depth direction. In each of the embodiments described below, for example, a first conductive type is N and, whereas a second conductive type is P.

[0046] As shown in FIG. 1, a semiconductor substrate (layer) 10 consisting of, for example, silicon is composed of a first semiconductor substrate 1 and a second semiconductor substrate 2. The first semiconductor substrate 1 has impurities of a high concentration and an N type conductivity. The second semiconductor substrate 2 is formed on the first semiconductor substrate 1 and has an N type conductivity with an impurity concentration lower than that of the first semiconductor substrate 1. The second semiconductor substrate 2 m...

second embodiment

[0067] A second embodiment will be described with reference to FIGS. 13 to 20. In the first embodiment, the second semiconductor substrate 2 is composed of, for example, a single epitaxial growth layer or the like. In contrast, a semiconductor device according to the second embodiment has a structure in which the second semiconductor substrate 2 has a plurality of layers and in which PN junctions are formed to be deeper by repeating the manufacturing method of the first embodiment.

[0068]FIG. 13 shows the sectional structure of the semiconductor device according to the second embodiment of the present invention. This semiconductor device is a vertical MISFET in which PN junctions are formed to extend in the depth direction. In the second embodiment, the second semiconductor substrate 2 is composed of a plurality of epitaxial growth layers consisting of, for example, silicon. The first and second diffusion areas 13 and 14 are formed by forming a plurality of different impurity diffus...

third embodiment

[0082] A third embodiment will be described with reference to FIGS. 22 to 24. In addition the structure of the second embodiment, the third embodiment has a structure in which diffusion areas are further repeatedly formed breadthwise.

[0083]FIG. 22 shows the sectional structure of a semiconductor device according to the third embodiment of the present invention, i.e. the sectional structure of a semiconductor substrate provided with vertical MISFET elements. As shown in FIG. 22, for example, three second diffusion areas (P type areas) 14 are formed inside the semiconductor substrate 2 so as to be each sandwiched between the first diffusion areas (N type areas) 13. It is possible to further increase the number of second diffusion areas 14.

[0084]FIG. 23 shows an impurity concentration profile of a portion of the semiconductor device taken along the line XXIII-XXIII in FIG. 22. FIG. 24 shows a NET concentration profile indicating the total concentration distribution of the same portio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More