Semiconductor power device with insulated gate formed in a trench, and manufacturing process thereof

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

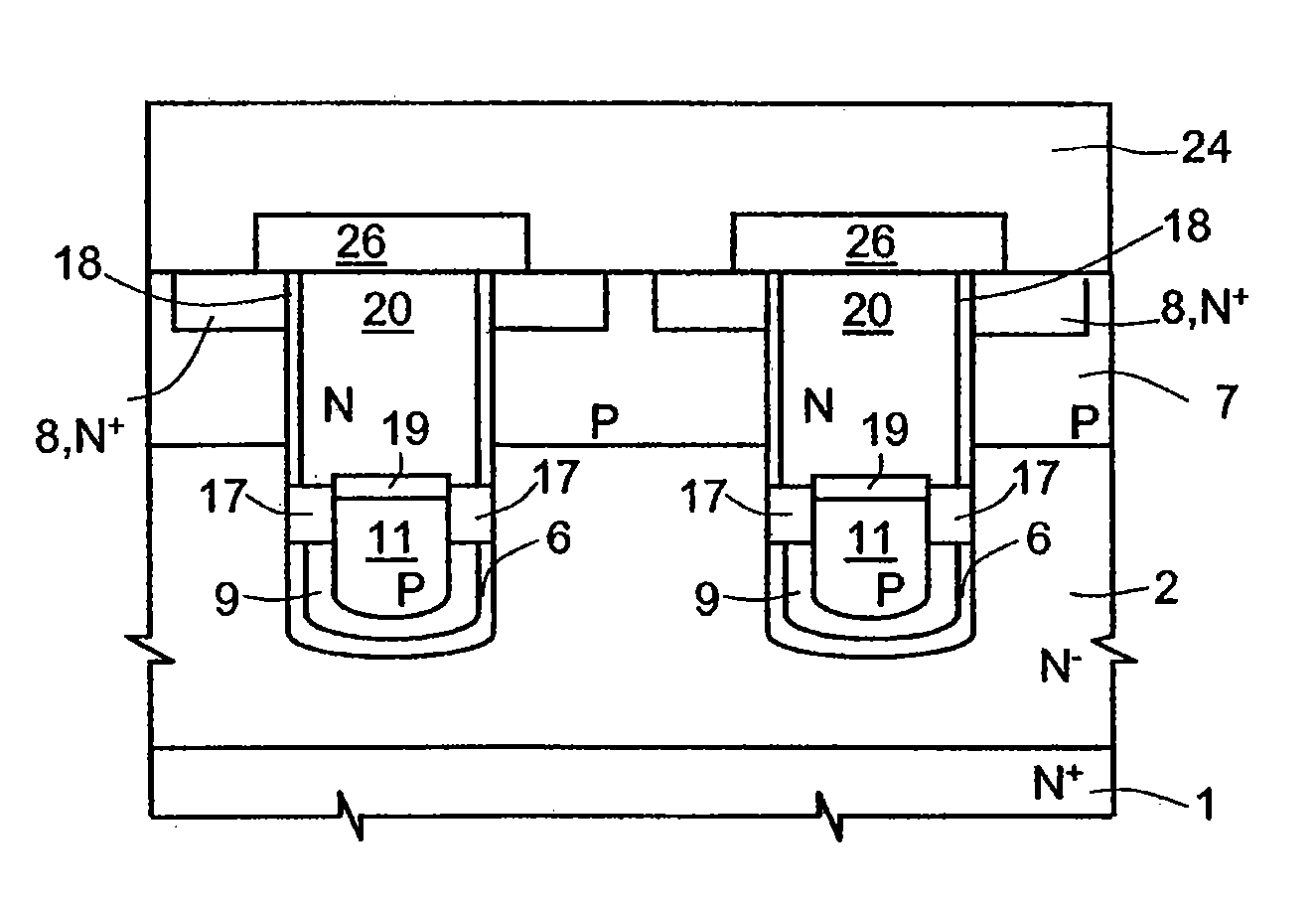

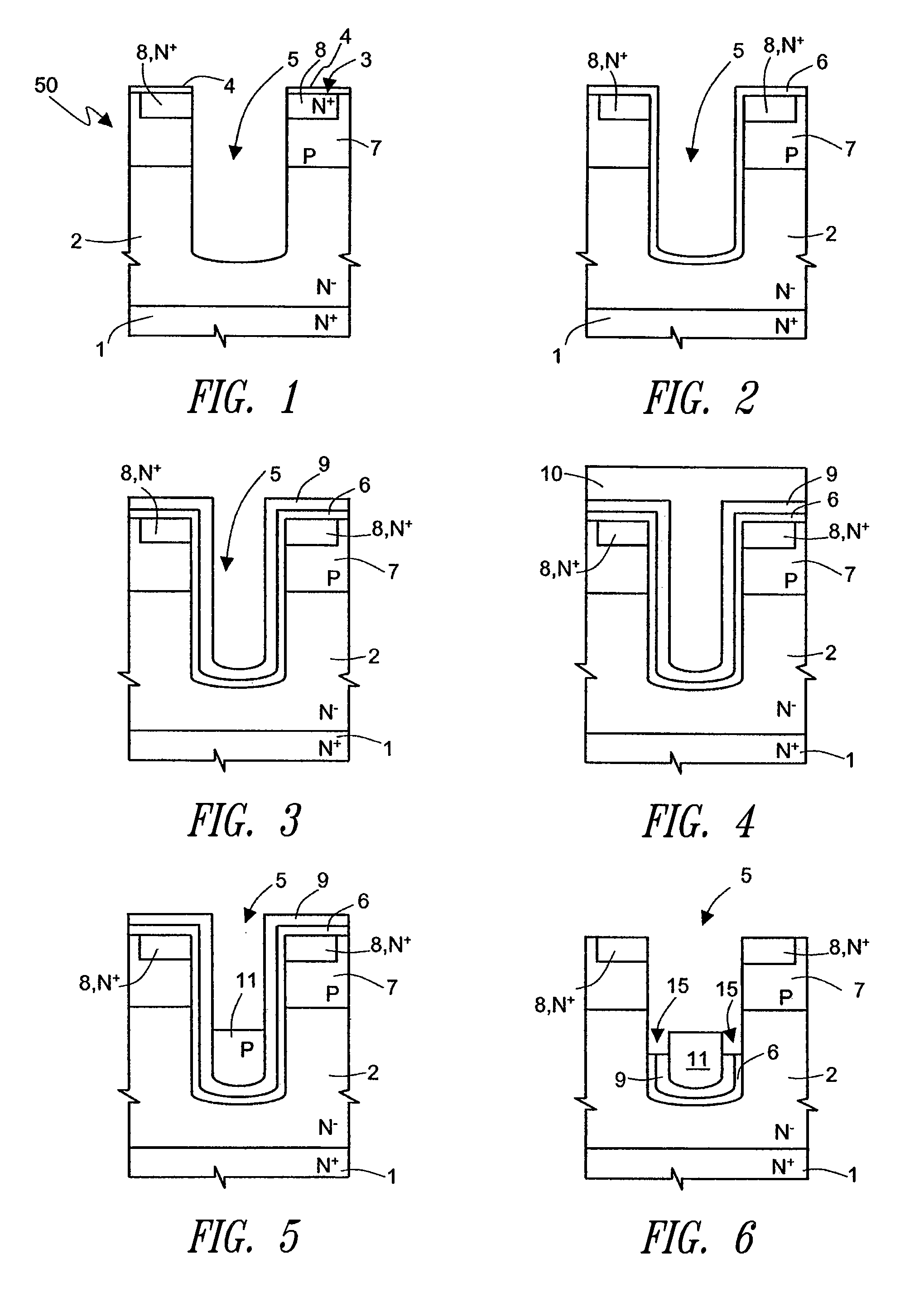

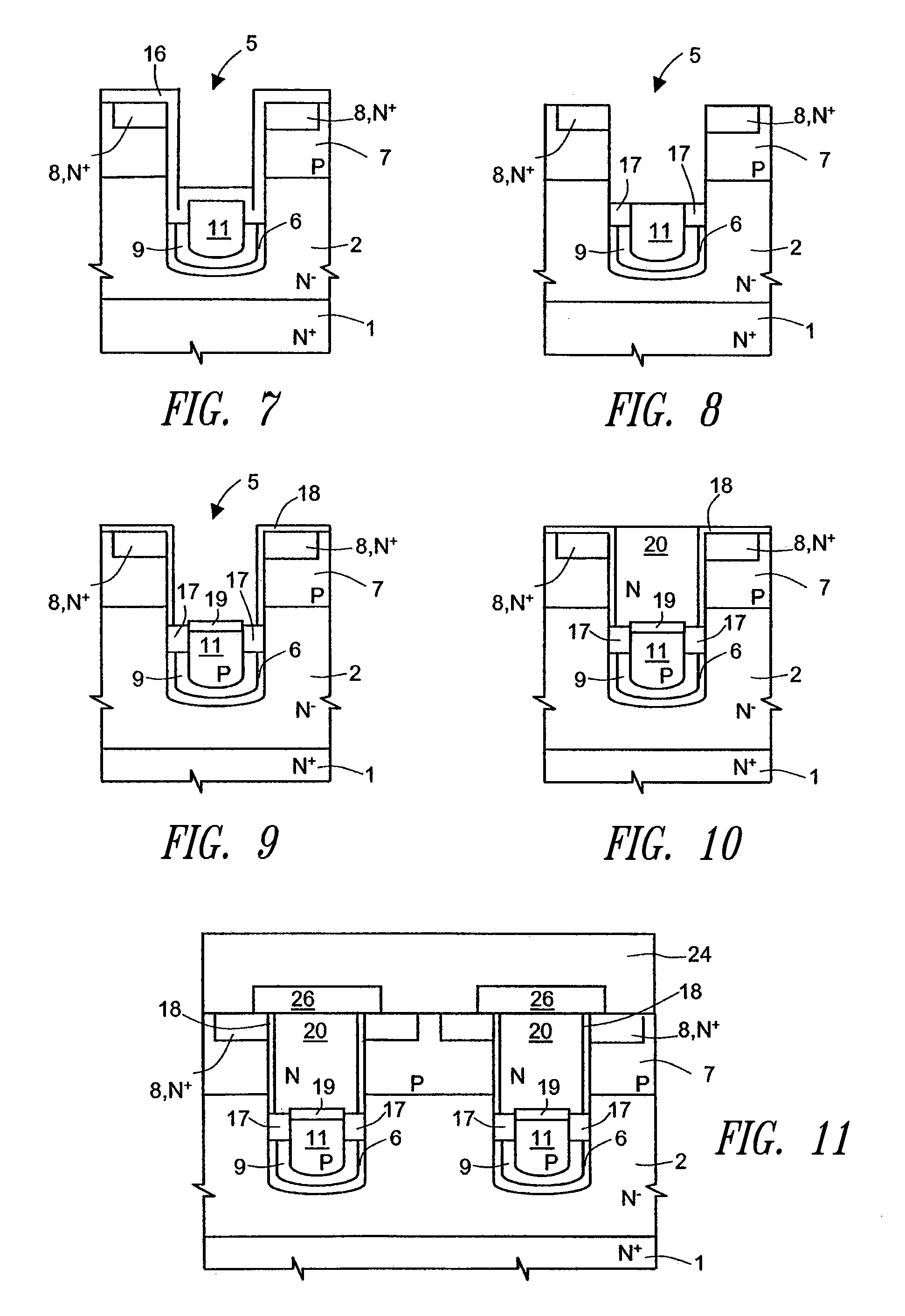

[0025]FIG. 1 shows a wafer 50 of semiconductor material that comprises a substrate 1, which is heavily doped (for example, of an N+ type for forming a power MOS or P+ type for forming an IGBT), and a semiconductor layer, which is less doped (in the example, of an N-type) and is, for example, grown epitaxially on top of the substrate 1 (epitaxial layer 2 forming a drift region). The epitaxial layer has a top surface 3, and a buffer layer, for example of an N+ type, can extend between the substrate 1 and the epitaxial layer 2.

[0026] After manufacturing edge structures and opening the active area, body regions 7 of P-type are blanket-implanted, for example, by doping the silicon with B, BF2, Al, or In. In a way not shown, a deep enrichment of the body regions (deep body) is possibly effected in accordance with the prior art, by implanting dopants of P+ type using a resist mask; then, using another resist mask, source regions 8 of N+ type are implanted, for example, by doping silicon w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More