Platform storage hierarchy with non-volatile random access memory with configurable partitions

a platform storage and random access memory technology, applied in the field of computer systems, can solve the problems of data loss, dram-based memory consumes power, and limiting factors of computer innovation today, and achieve the effect of reducing the cost of dram memory

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

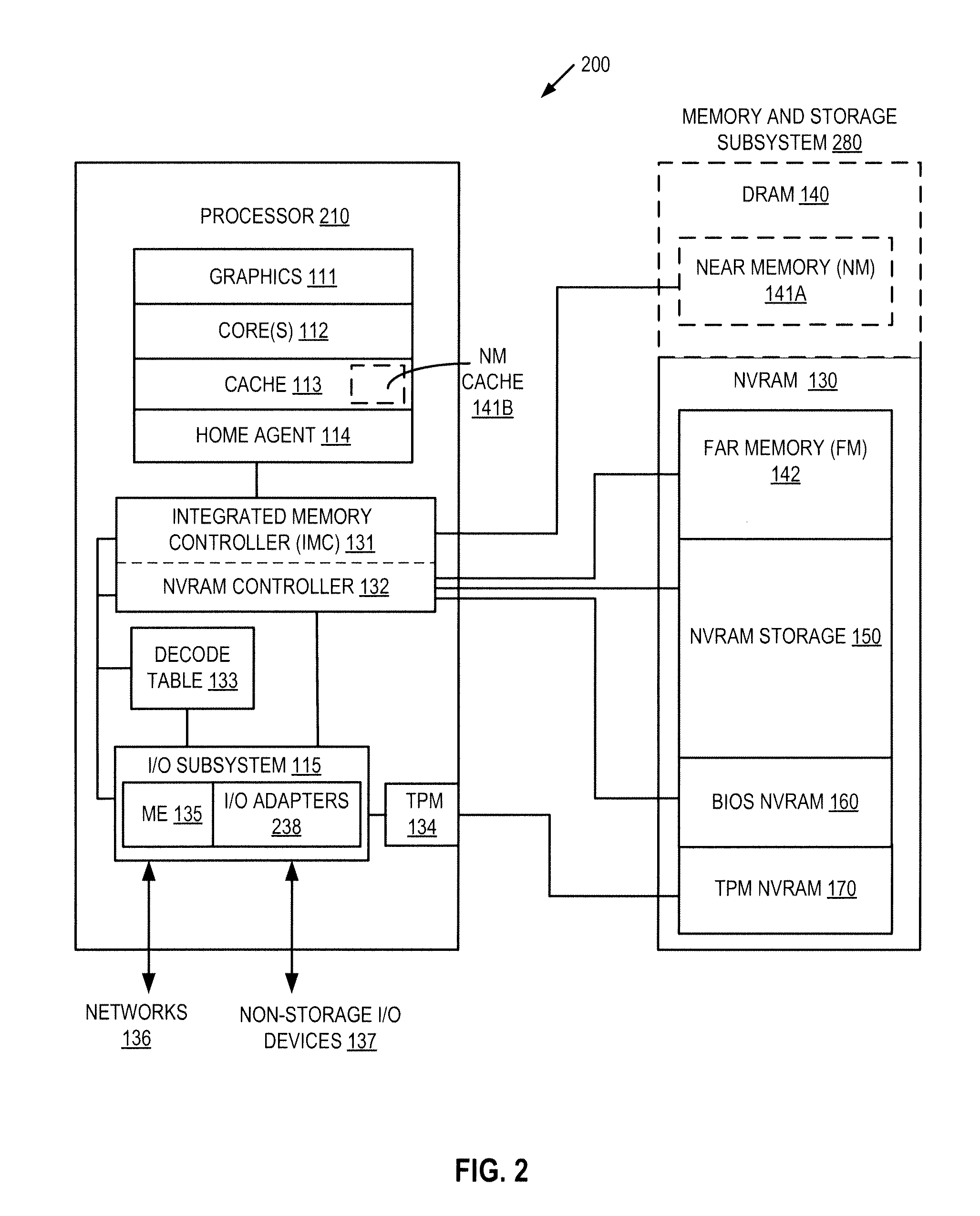

[0088]FIG. 5 illustrates an interface between software and storage provided by NVRAM 130 of FIG. 2 according to the invention. In this embodiment, IMC 131 has the additional capability of abstracting NVRAM 130 as traditional non-volatile mass storage (e.g., disks or flash memory) for the software. IMC 131 is coupled to a storage driver 513, which can be implemented in software. To storage driver 513, IMC 131 serves as traditional non-volatile mass storage that is block-addressable. Computer system 200 uses this storage driver 513 as the lowest-level disk driver. In this embodiment, software (OS 512 and applications) can utilize data in NVRAM 130 without modification to the software. That is, data access to a non-resident page (a page not in the system memory) will trigger a page fault and a disk I / O will be performed.

[0089]In the embodiment shown in FIG. 5, when OS 512 initiates a storage I / O (e.g., in response to a page fault to bring in a page that is not resident in the system me...

third embodiment

[0095]FIGS. 8A and 8B illustrate an interface between software and storage provided by NVRAM 130 with the reference to FIG. 6B according to one embodiment of the invention. FIG. 6B illustrates a memory and storage subsystem 682 according to one embodiment of the invention. In the embodiment shown in FIG. 6B, there is no distinction between mass storage and system memory within NVRAM 130. The OS (OS 850 of FIG. 8B) creates a memory-mapped file system, where FM 142 serves as storage for file system 660. It is understood that NVRAM 130 may include more or fewer partitions than what is shown in FIG. 6B (e.g., BIOS NVRAM 160 and / or TPM NVRAM 170 may be absent).

[0096]In a memory-mapped file system, the files used by an application 810 (and are, therefore, in a virtual address space 820 allocated to application 810) can be directly mapped to NVRAM device address space 840. Each address location in NVRAM device address space 840 is directly-addressable by the processor, and is, therefore, “...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More