Power array with staggered arrangement for improving on-resistance and safe operating area

a power array and staggered arrangement technology, applied in the field of power arrays, can solve the problems of low on-resistance and reliability of the device, and achieve the effects of suppressing heat accumulation in the device, widening the safe operating area, and low on-resistan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016]In the following detailed description of the invention, reference is made to the accompanying drawings which form a part hereof, and in which is shown, by way of illustration, specific embodiments in which the invention may be practiced. These embodiments are described in sufficient detail to enable those skilled in the art to practice the invention. Other embodiments may be utilized and structural, logical, and electrical changes may be made without departing from the scope of the present invention.

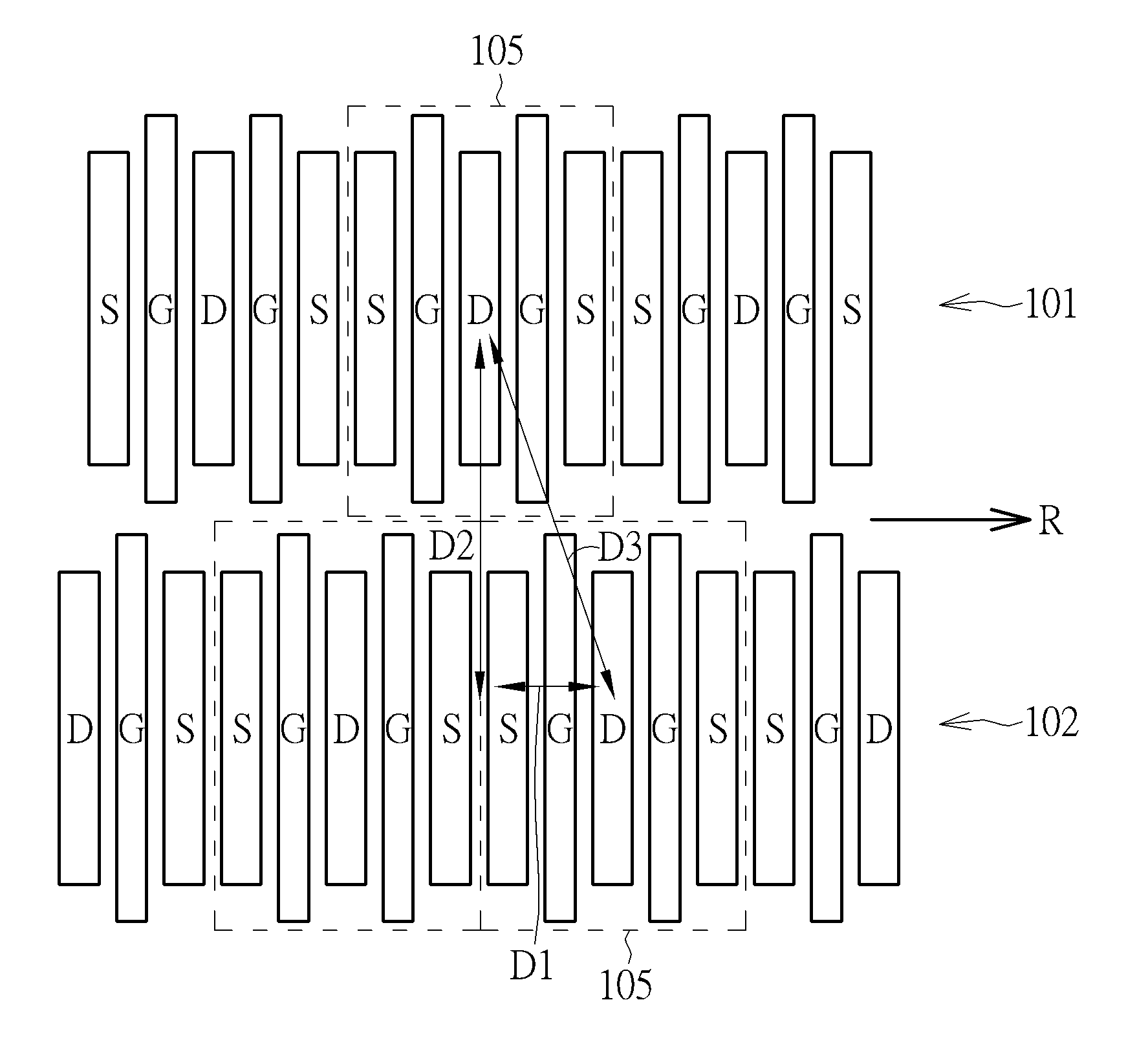

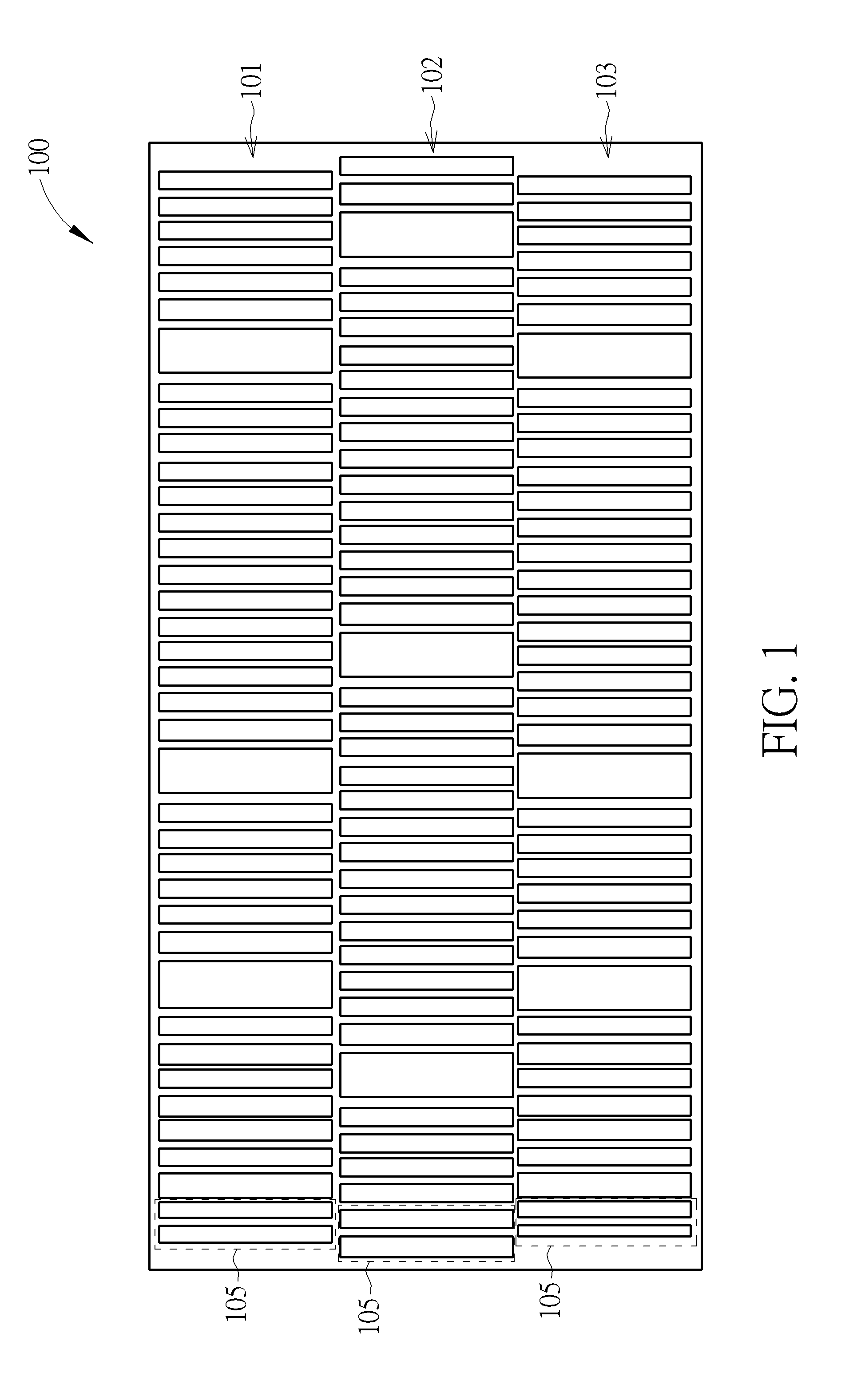

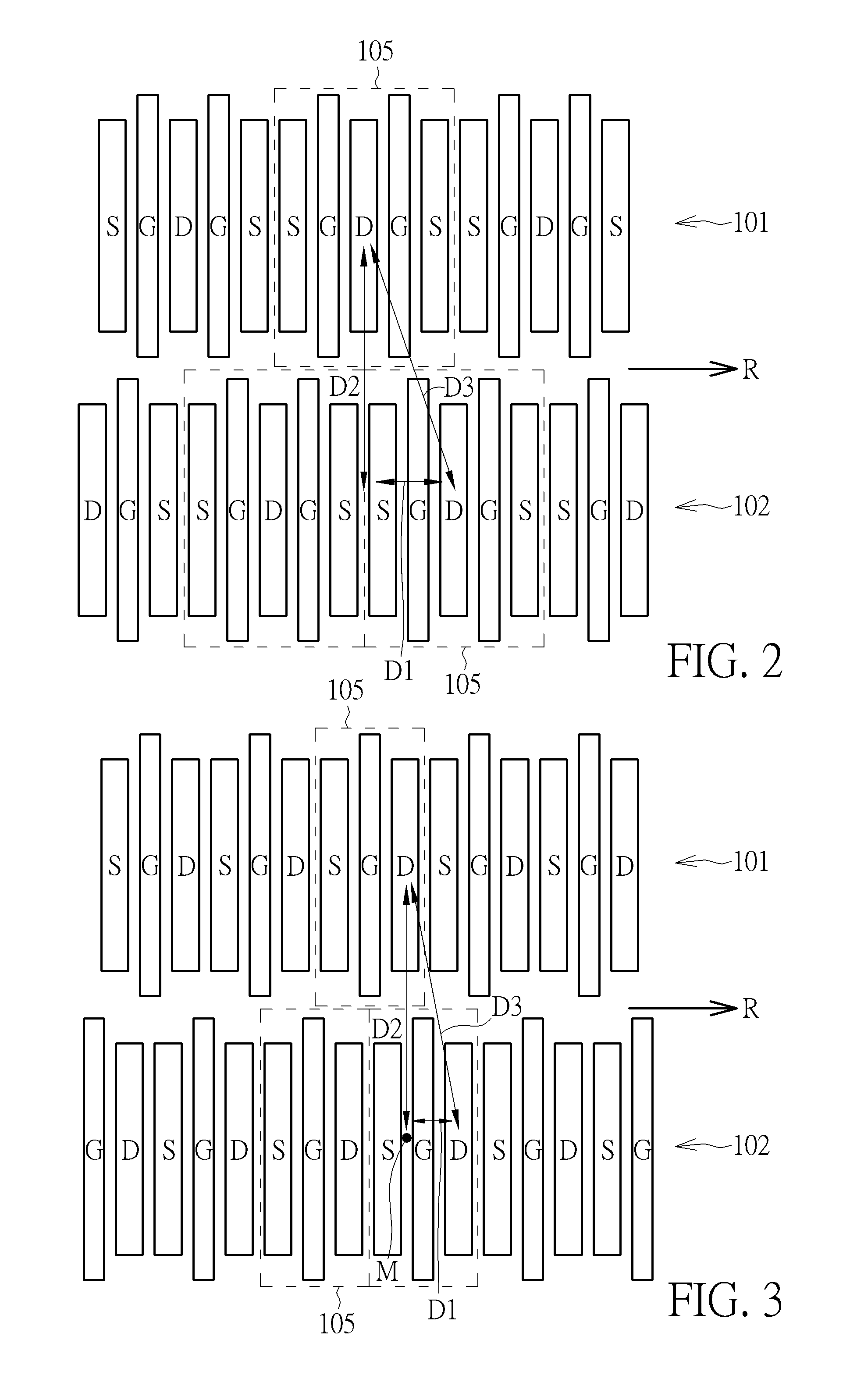

[0017]The embodiments will now be explained with reference to the accompanying drawings to provide a better understanding to the structure of the present invention. First, as shown in FIG. 1, a power array 100 is provided with at least two device rows in a staggered arrangement (in this embodiment, three device rows 101 / 102 / 103 are shown in FIG. 1). Each device row further includes a plurality of parallel device units 105, such as LDMOS, FDMOS, CMOS or DEMOS, arranged along the dev...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More