Comparator circuits with local ramp buffering for a column-parallel single-slope ADC

a comparator circuit and local ramp technology, applied in the field of comparator circuits, can solve the problems of adc non-linearity, variable capacitive load on vsub>ramp /sub>, and low comparator kickback, and achieve constant capacitive load and large input swing.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

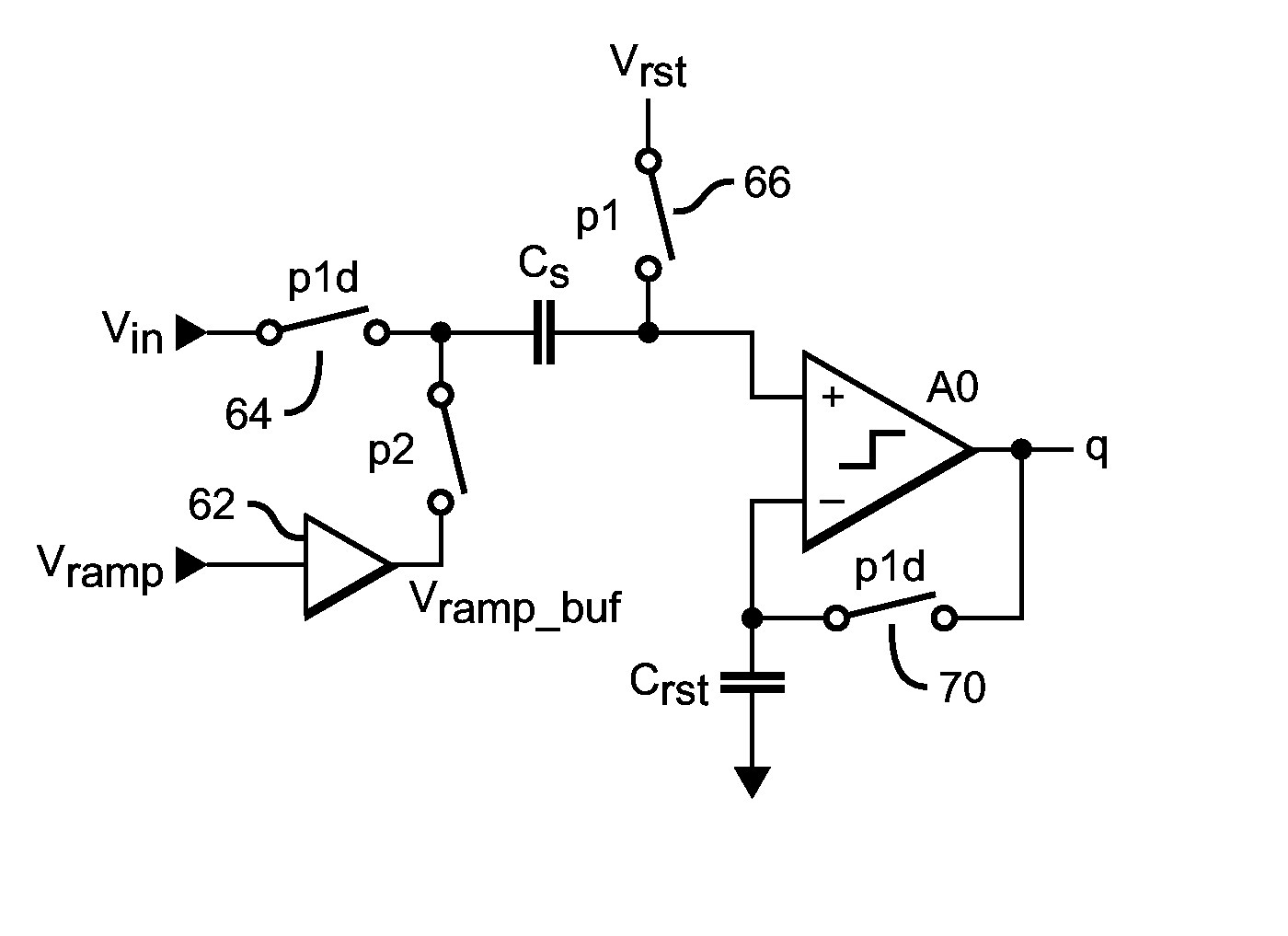

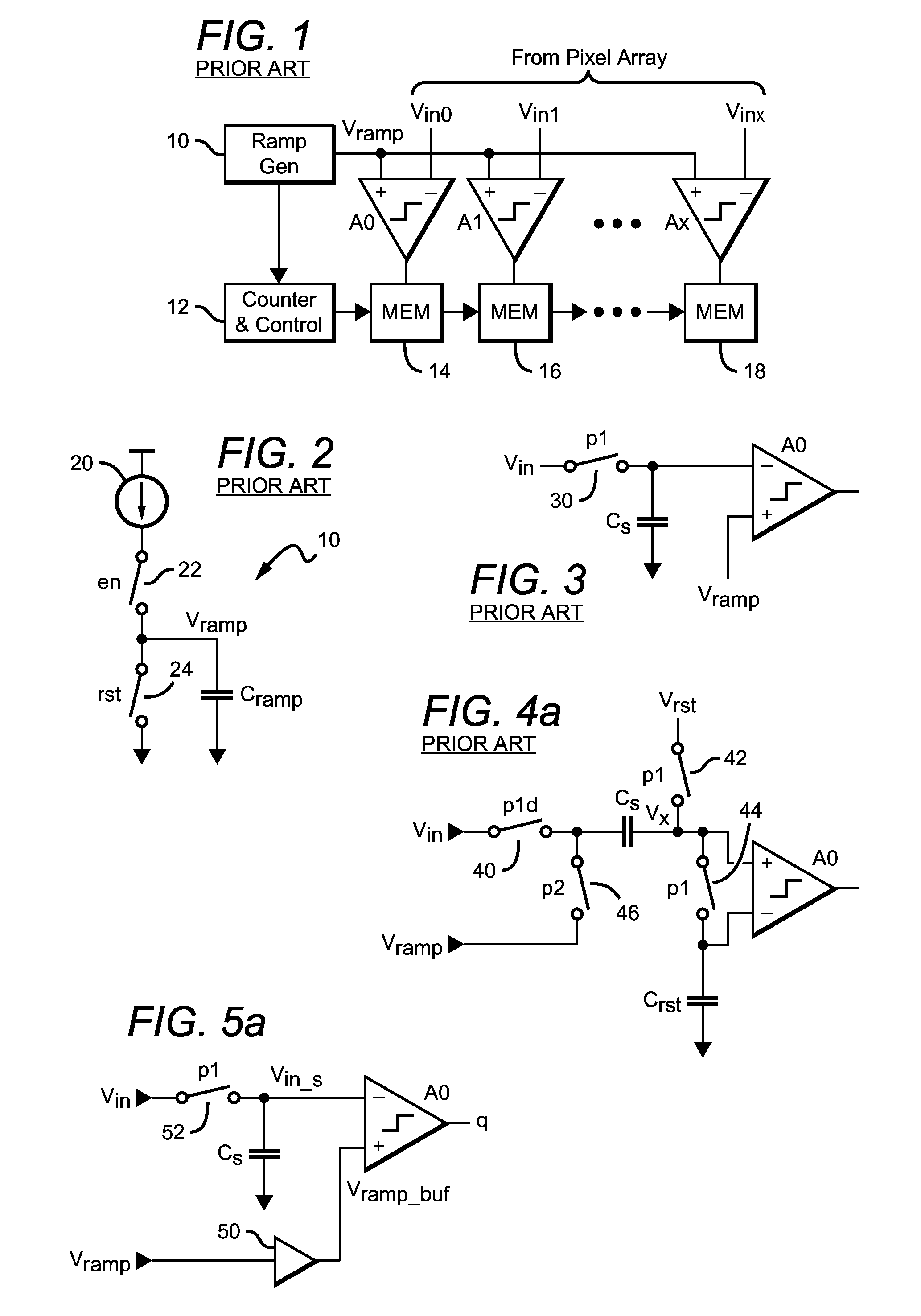

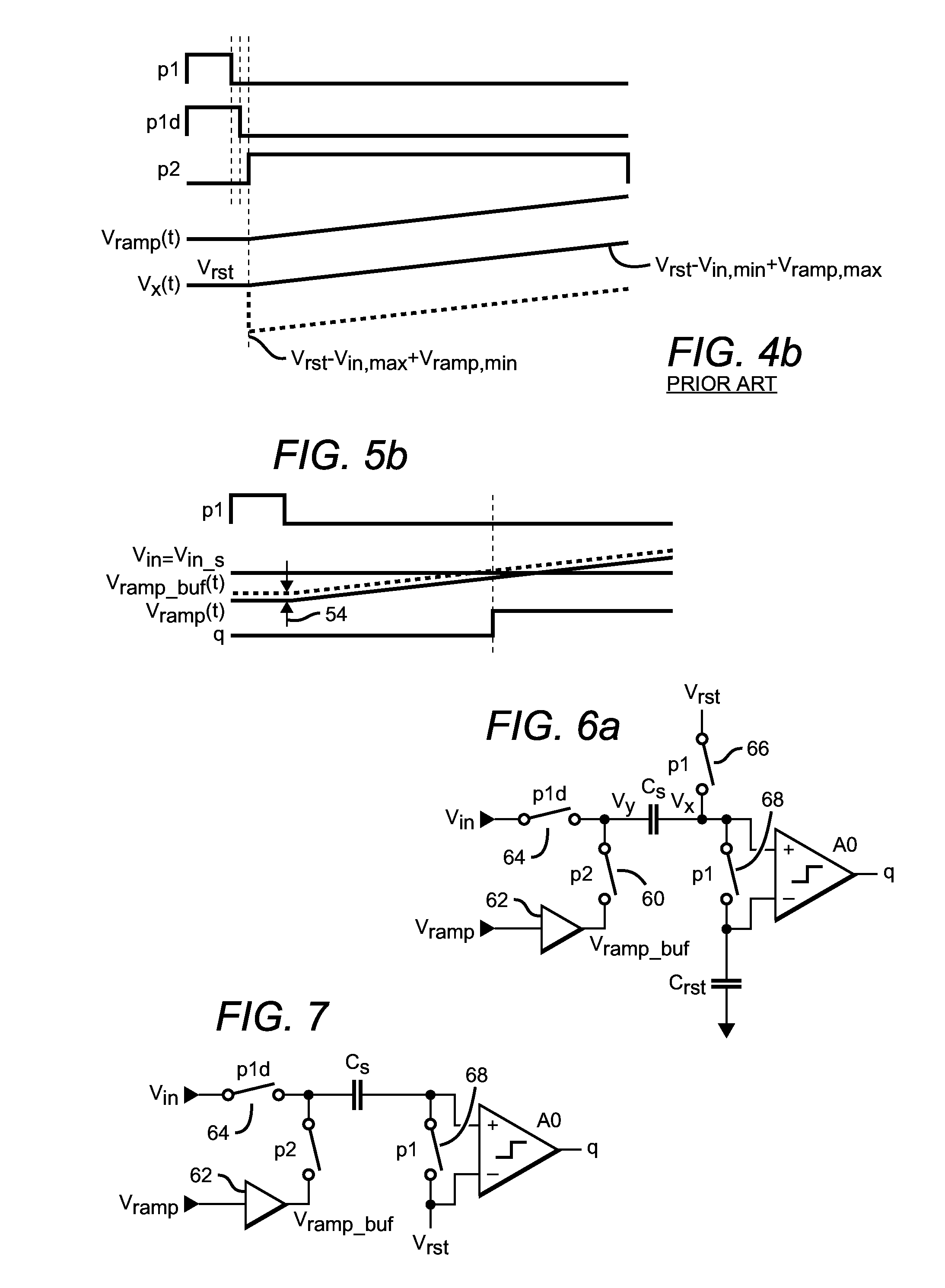

[0034]The present comparator circuit employs ‘local ramp buffering’. Each comparator circuit includes a local ramp buffer which receives the global voltage ramp as an input and outputs a buffered voltage ramp for use by the comparator circuit. The local ramp buffers serve to reduce the adverse effects on the global voltage ramp that might otherwise occur due to the operation of the individual comparator circuits.

[0035]One possible embodiment of the present comparator circuit is shown in FIG. 5a, with a corresponding timing diagram shown in FIG. 5b. A DC-coupled arrangement is shown, in which a voltage ramp signal is connected directly to an input of comparator A0. Here, however, rather than connecting global voltage ramp Vramp directly to the comparator, a local ramp buffer 50 is interposed between Vramp and A0: Vramp is connected to the input of buffer 50, and the buffer's output Vramp_buf is provided to the comparator input. Input voltage Vin is coupled to a sampling capacitor Cs ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More