Transistorless all-memristor neuromorphic circuits for in-memory computing

a neuromorphic circuit and all-memristor technology, applied in computing models, biological models, instruments, etc., can solve the problems of inability to multi-layer stackability, inconvenient multi-layer stacking, and large overheads

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0074]The detailed description set forth below in connection with the appended drawings are intended as a description of various embodiments of the present invention and are not intended to represent the only embodiments in which the present invention is to be practiced. Each embodiment described in this disclosure is provided merely as an example or illustration of the present invention, and should not necessarily be construed as preferred or advantageous over other embodiments. In some instances, well-known methods, procedures, objects, and circuits have not been described in detail so as to not unnecessarily obscure aspects of the present disclosure.

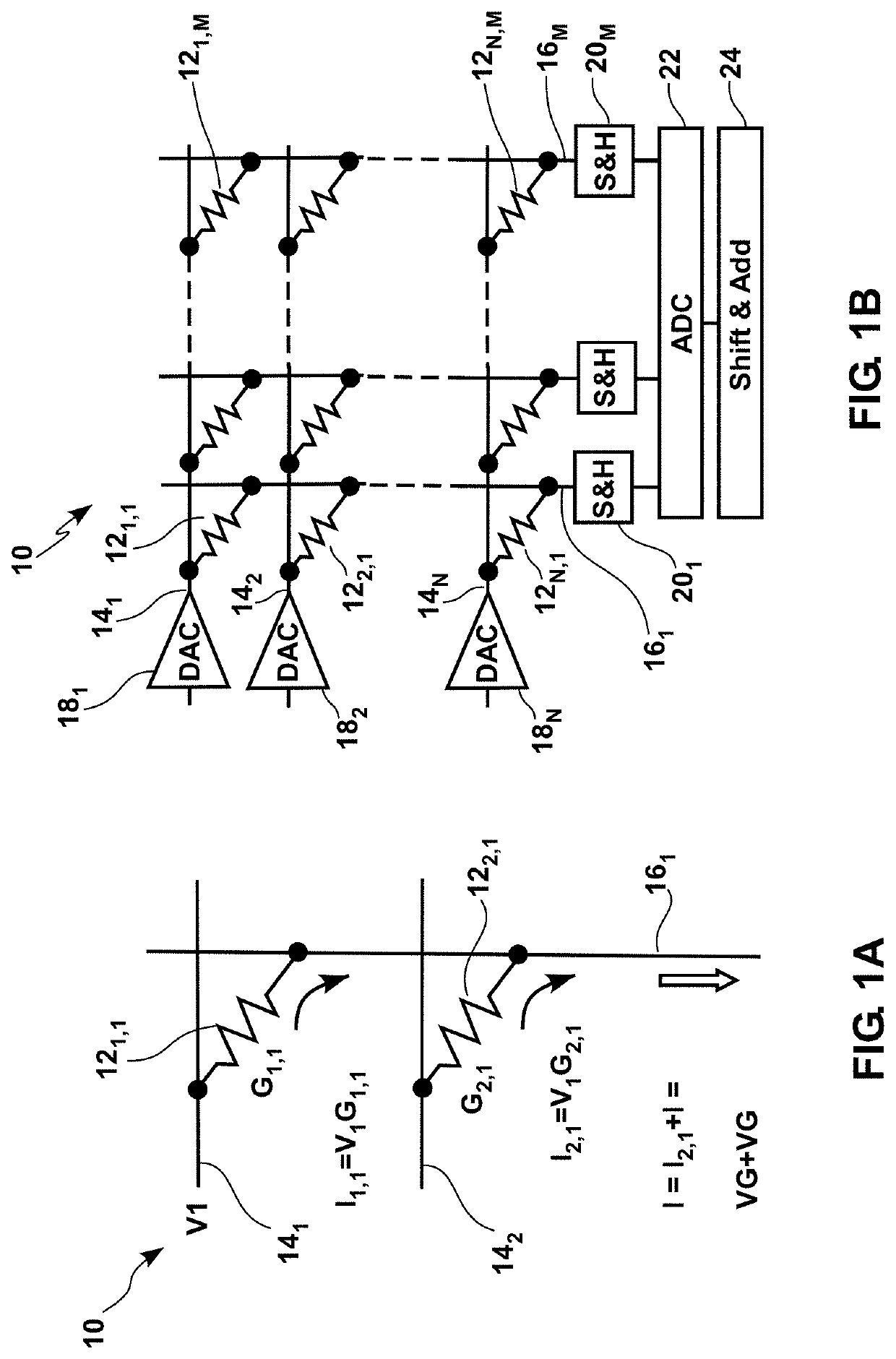

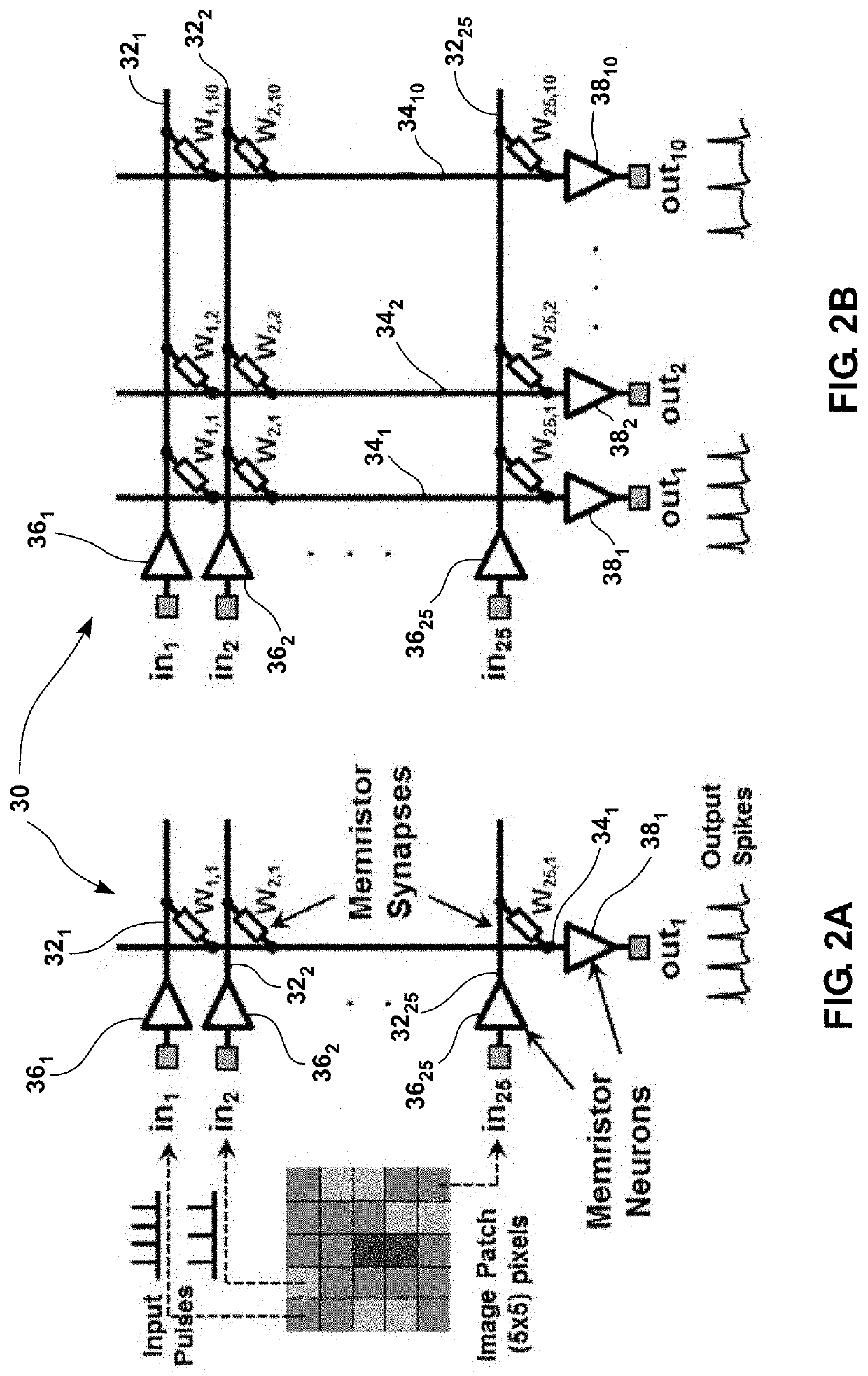

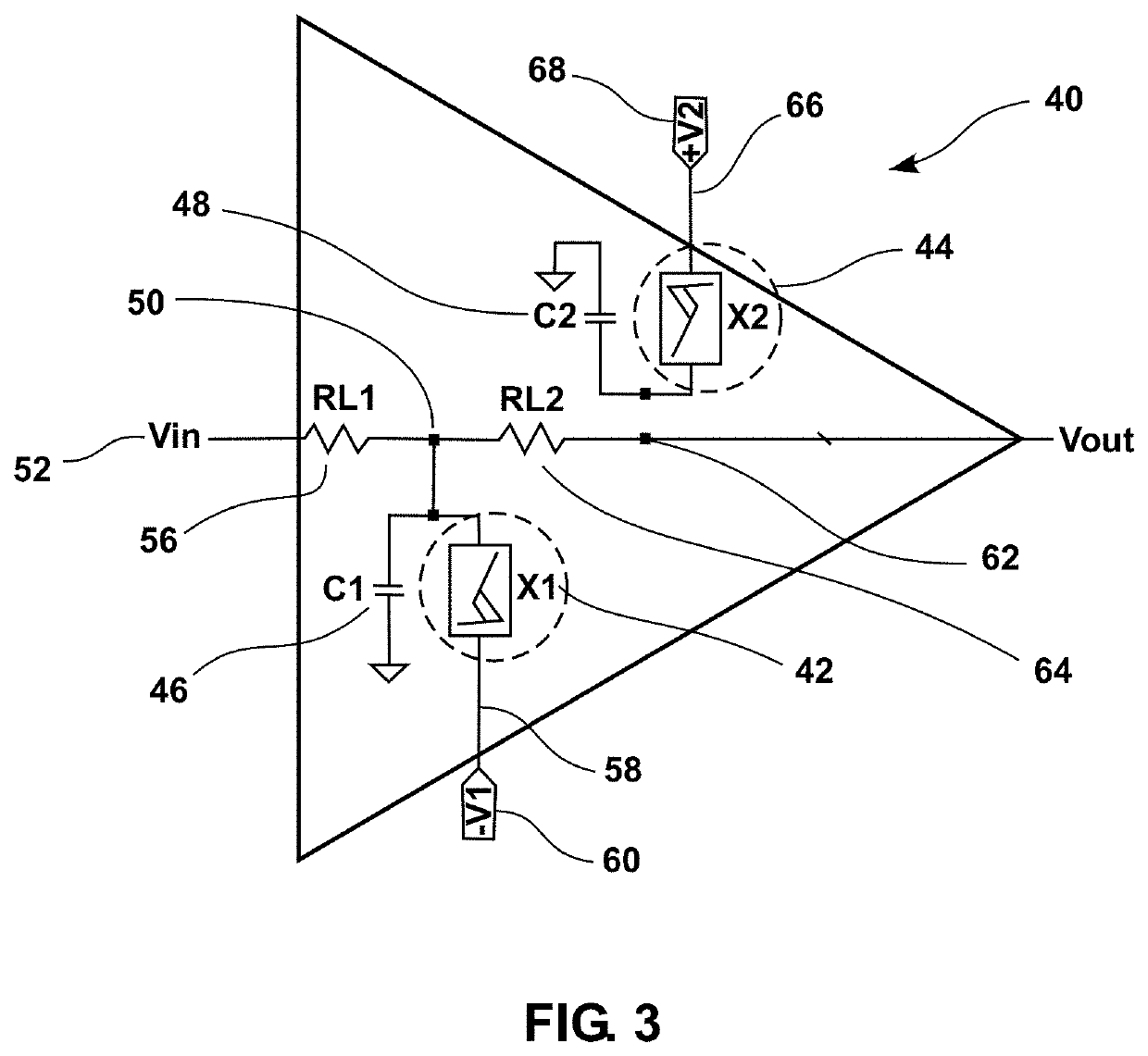

[0075]By contrast with the above-described prior art circuits, embodiments of this presentation relate to an all-memristor neuromorphic MAC accelerator that can be entirely analog, which can employ nonvolatile passive-memristor synapses for row-to-column coupling, and spiking active-memristor neurons for generating input and output si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More