Self correcting data re-timing circuit and method

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

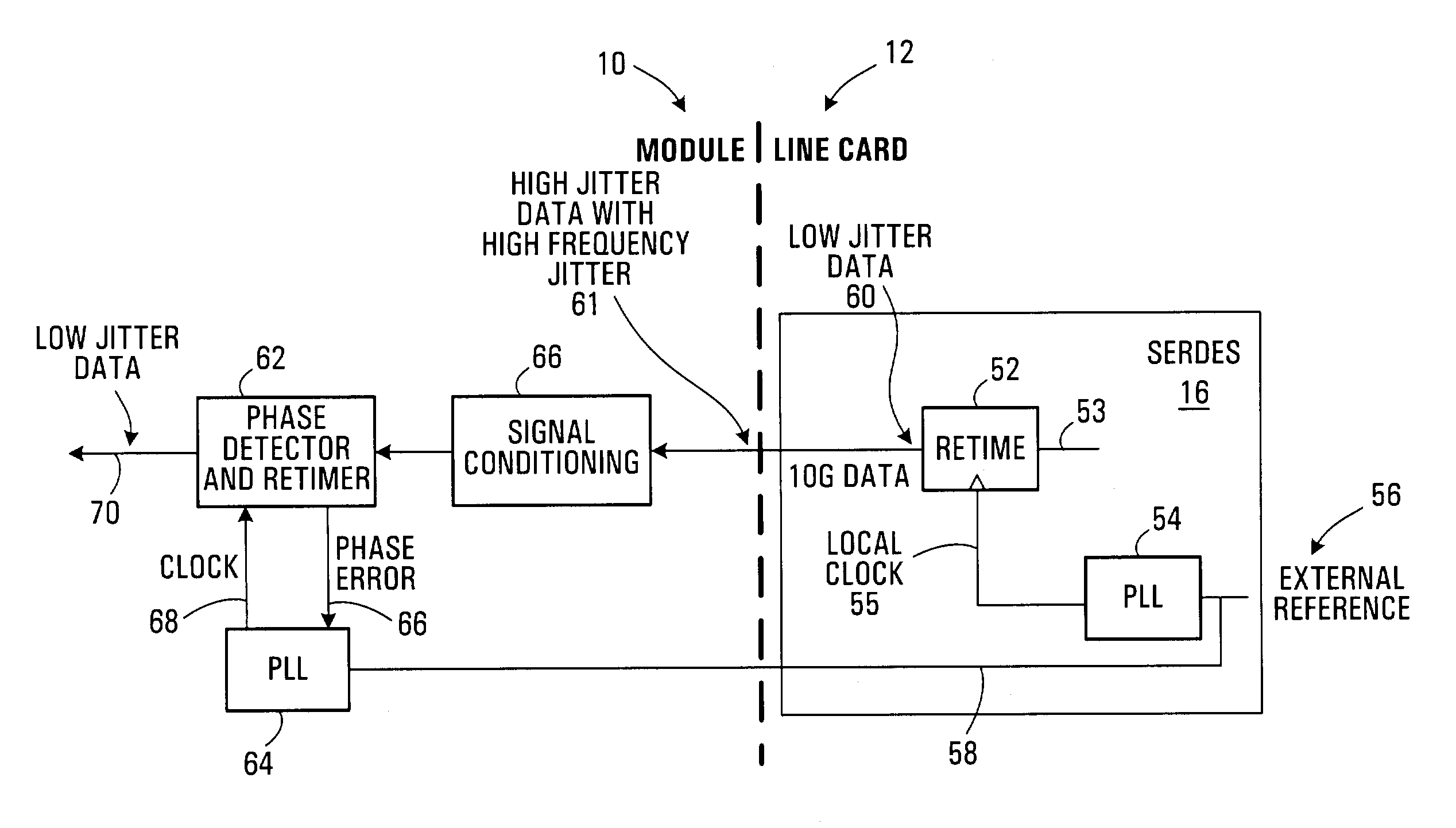

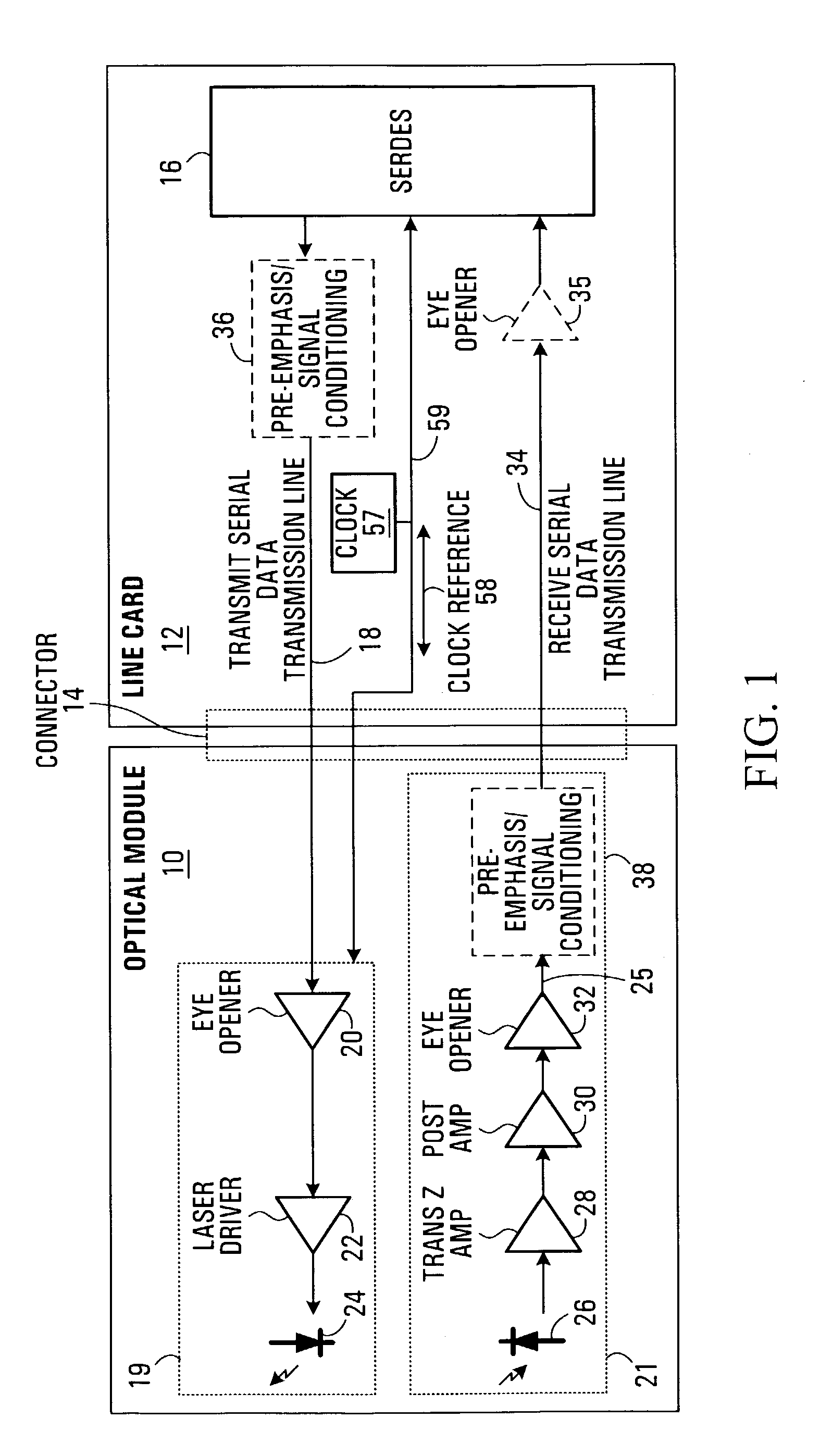

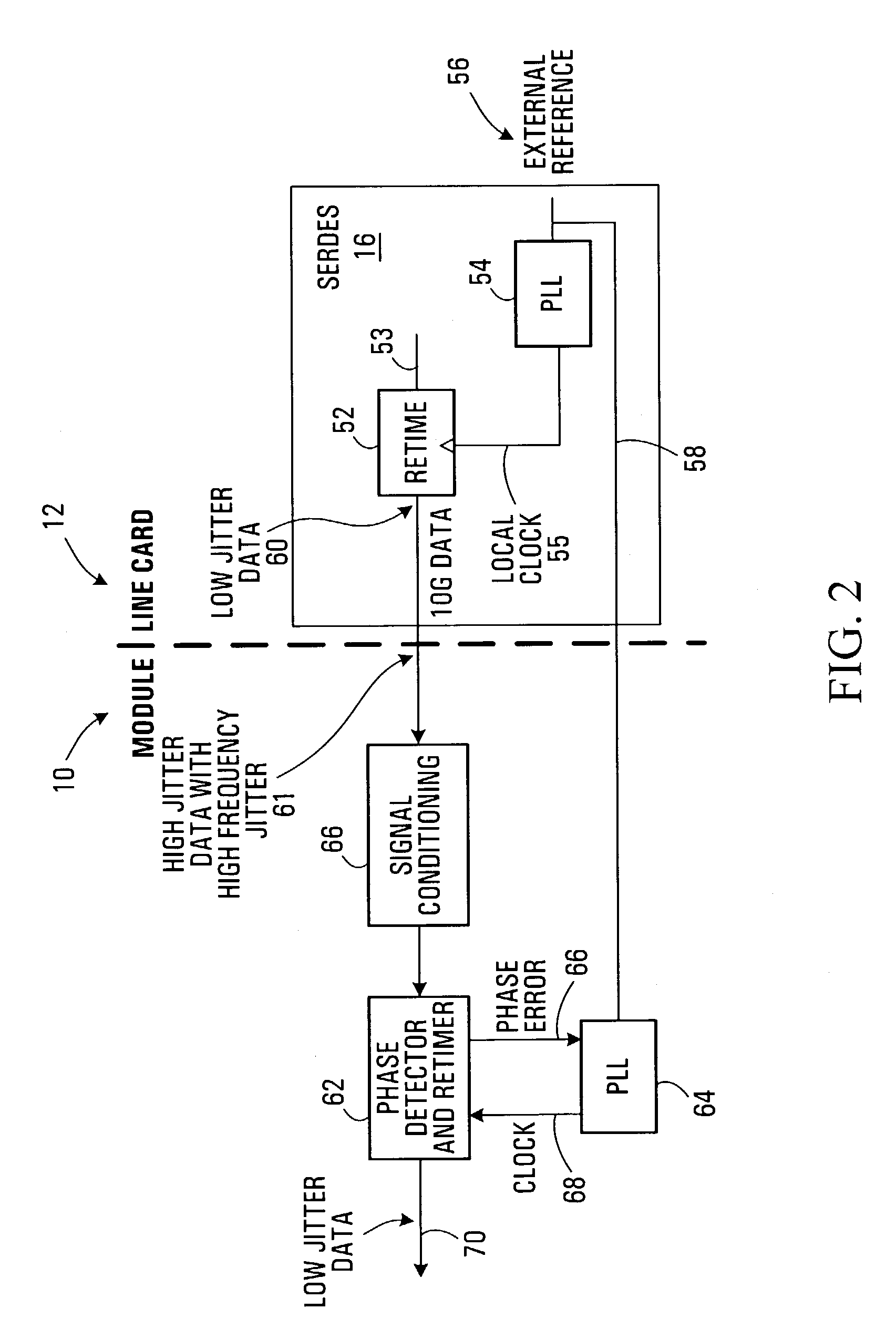

[0040]Referring to FIG. 1 an optical module 10 is shown connected to a line card 12 via a connector 14.

[0041]The electronic components of the line card 12 are placed atop a lossy PCB (Printed Circuit Board) substrate onto which conductive tracks are fabricated. For the purposes of the present description a SERDES device 16 is shown on the line card driven by a clock 57 which generates clock reference 58. Two conductive tracks 18, 34 from the SERDES 16 to the connector 14 are also shown. Also shown is a connection 59 through the connector 14 from the clock 57 providing the clock reference 58 to the optical module. An eye opener circuit 35 is shown on the receive path. Because standard specifications tend to be less stringent on the receive path, it is not necessary in all implementations to include this eye opener circuit 35. Some implementations might include a pre-emphasis / signal conditioning function 36. This would likely be implemented as part of the SERDES 16. More generally, it...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More