Gate drivers for stacked transistor amplifiers

a transistor amplifier and gate driver technology, applied in the field of amplifiers, can solve problems such as power consumption, and achieve the effect of reducing the overall leakage curren

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028]Throughout the present disclosure, embodiments and variations are described for the purpose of illustrating uses and implementations of inventive concepts of various embodiments. The illustrative description should be understood as presenting examples of the inventive concept, rather than as limiting the scope of the concept as disclosed herein.

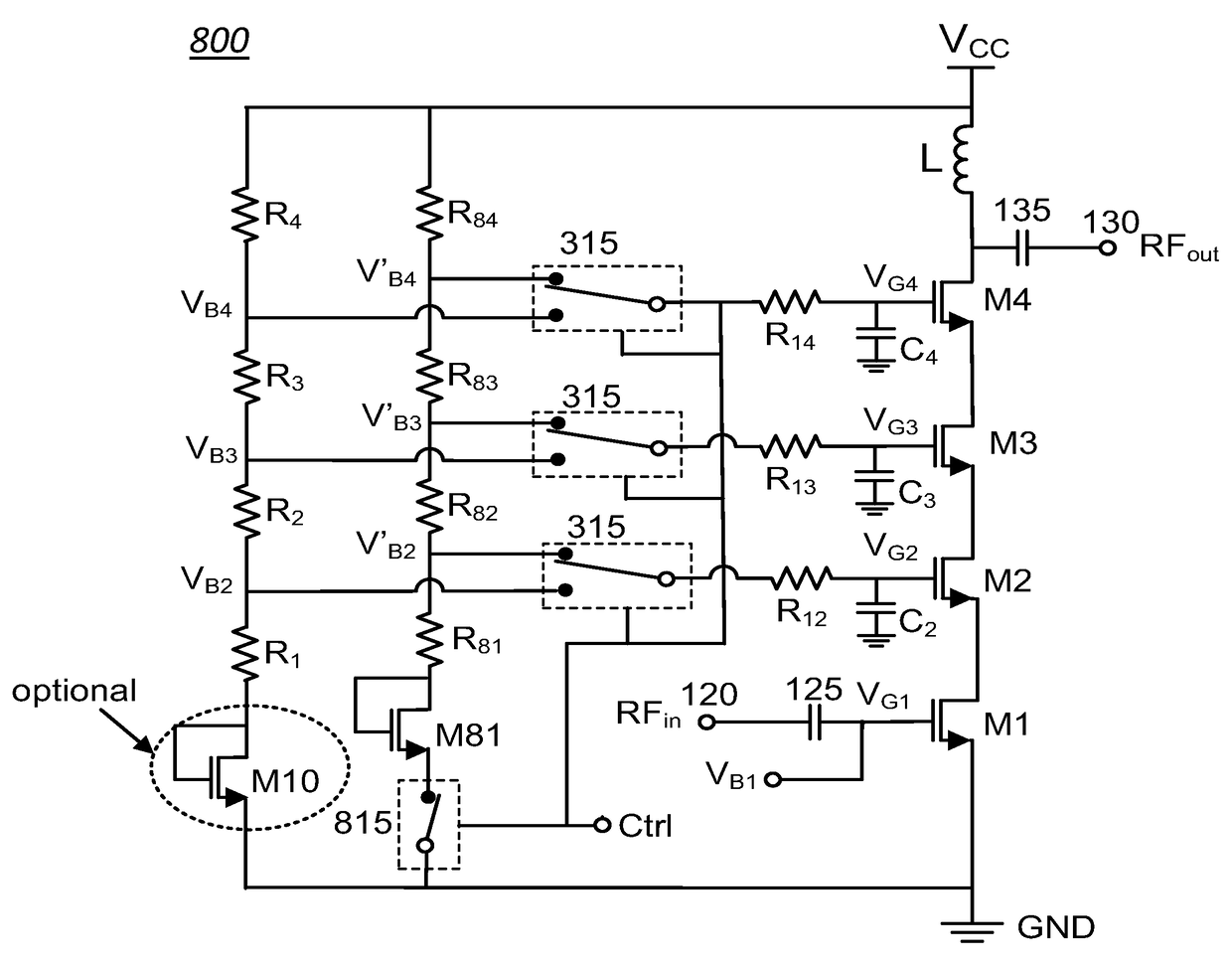

[0029]FIG. 1 shows a simplified schematic of a prior art stacked cascode (RF) amplifier (100). By way of example and not of limitation, the stacked cascode amplifier (100) can comprise a stack of FET transistors (M1, M2, M3, M4) that include an input transistor M1, cascode transistors (M4, M3, M2), and an output transistor M4. An input RF signal, RFin, provided at an input terminal (120) of the amplifier (100) is routed to a gate of the input transistor, M1, and is amplified by the amplifier (100). A corresponding amplified output RF signal, RFout, is provided at a drain of the output transistor, M4, and routed to an output terminal (13...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More