Pipelined instruction dispatch unit in a superscalar processor

a superscalar processor and instruction dispatch technology, applied in the field of computer architecture, can solve the problems of limiting the performance gain of additional parallelism, the need to recompile the programs of the vliw computer, and the inability to achieve the recompilation of the program, so as to avoid the complexity of the group logic circui

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

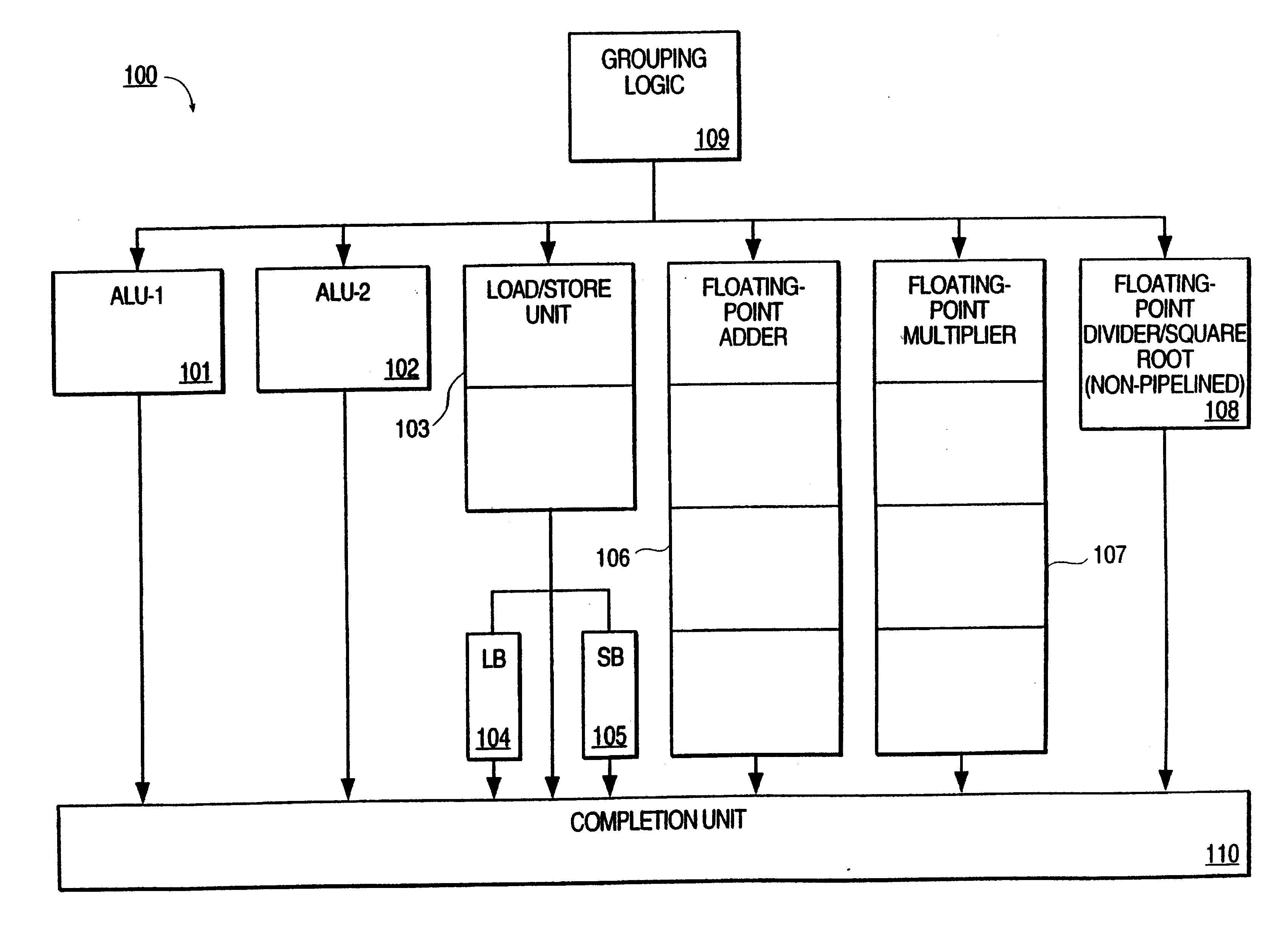

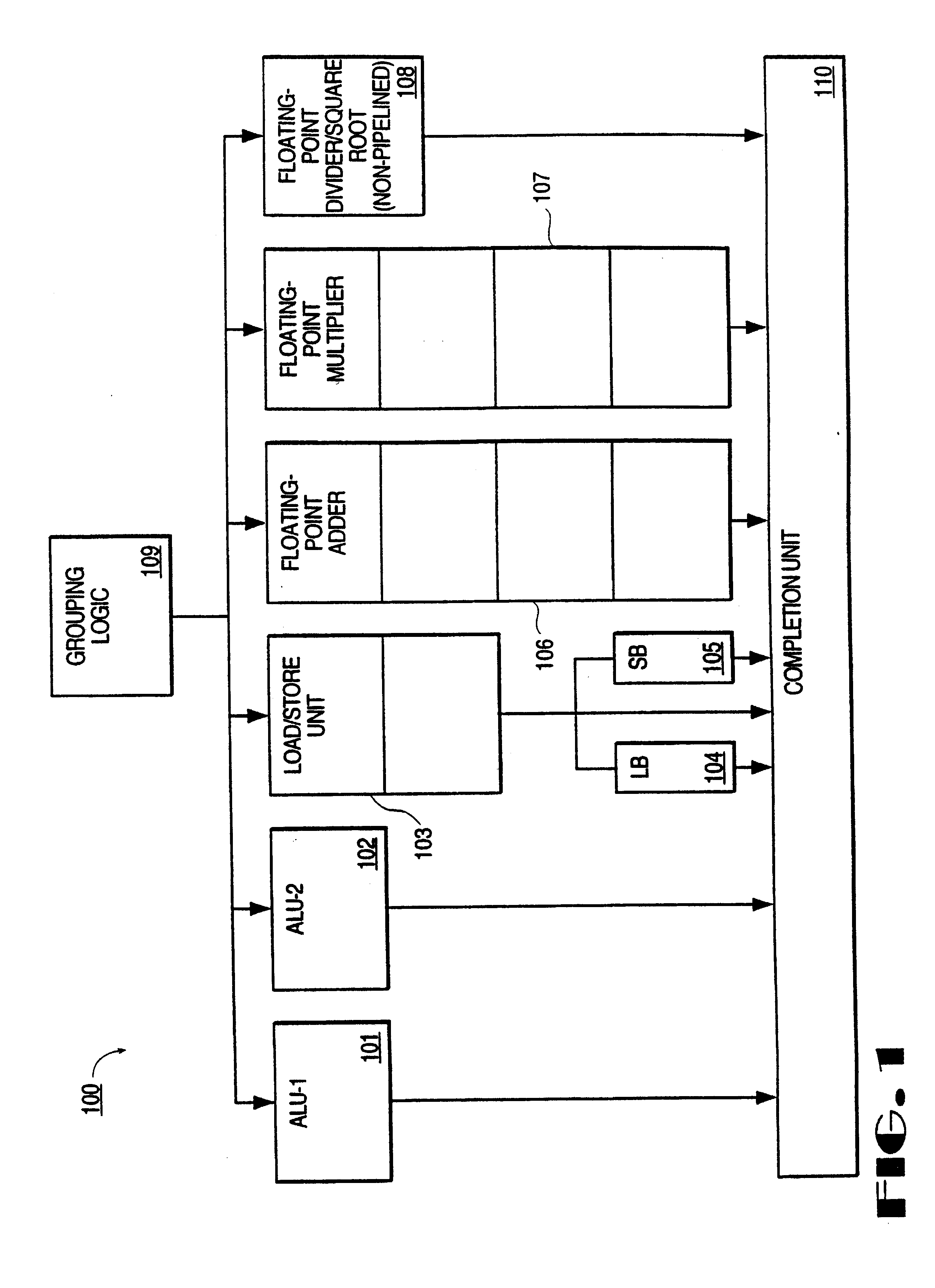

An embodiment of the present invention is illustrated by the block diagram of FIG. 1, which shows a central processing unit (CPU) 100 in an exemplary 4-way superscalar processor of the present invention. A 4-way superscalar processor fetches, dispatches, executes and retires up to four instructions per processor cycle. As shown in FIG. 1, central processing unit 100 includes two arithmetic logic units 101 and 102, a load / store unit 103, which includes a 9-deep load buffer 104 and an 8-deep store buffer 105, a floating point adder 106, a floating point multiplier 107, and a floating point divider 108. In this embodiment, a grouping logic circuit 109 dispatches up to four instructions per processor cycle. Completion unit 110 retires instructions upon completion. A register file (not shown), including numerous integer and float point registers, is provided with sufficient number of ports to prevent contention among functional units for access to this register file during operand fetch ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More