Programmable asynchronous triggering time delayer, and method of use

A technology of trigger and delay device, applied in the field of programmable asynchronous trigger delay device, to achieve the effect of simplifying circuit structure, eliminating burr phenomenon, and facilitating change or control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

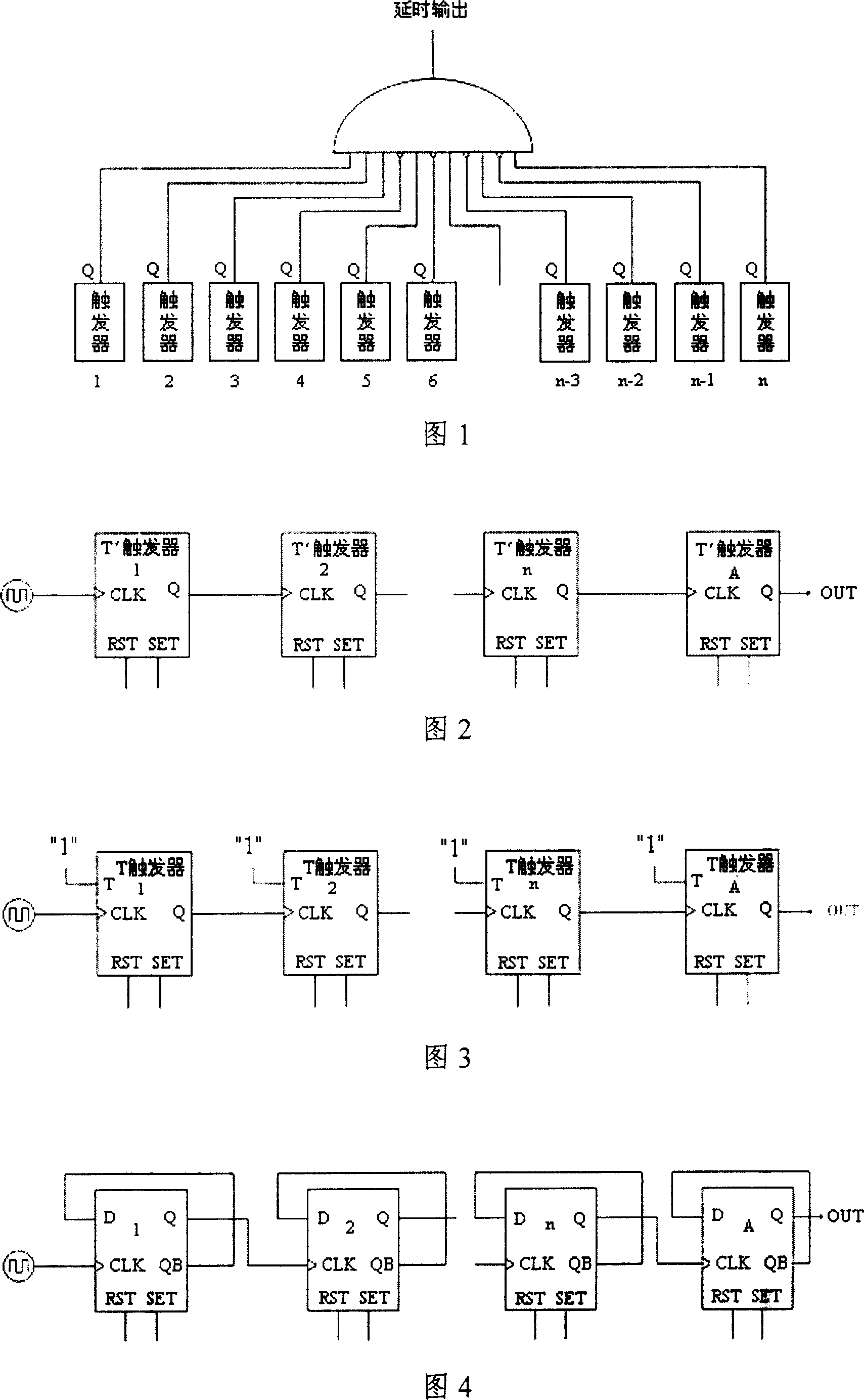

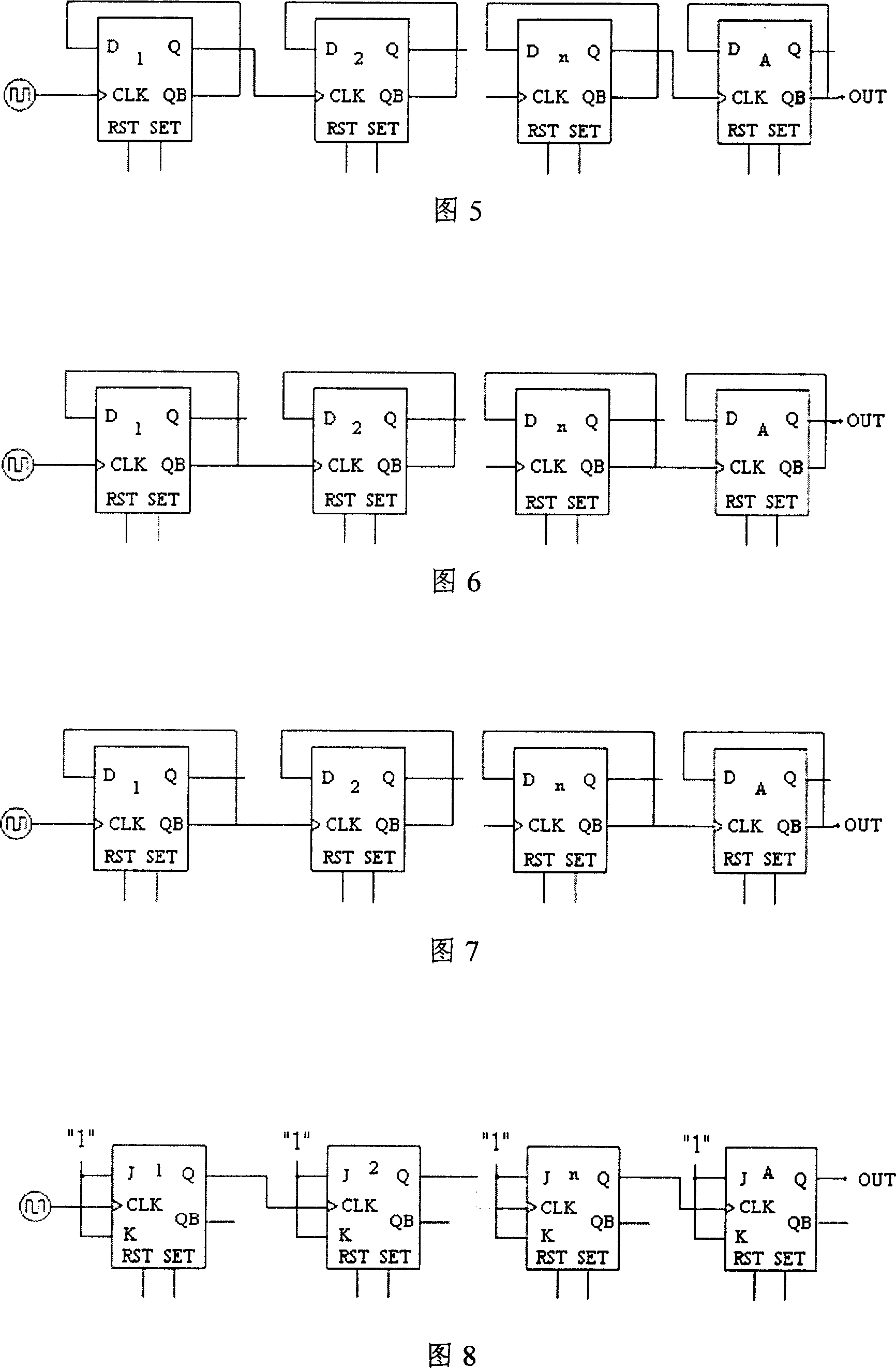

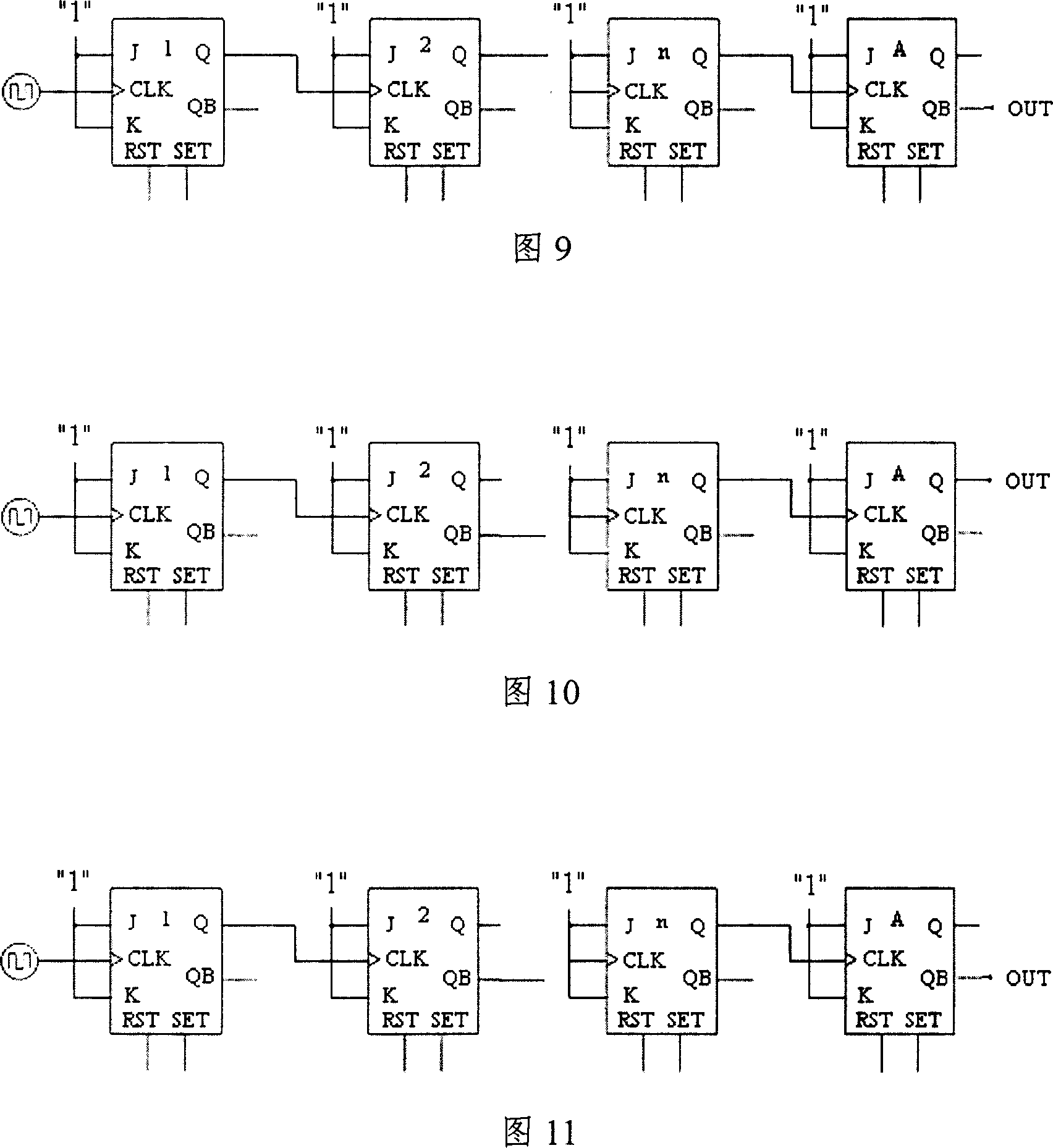

[0015] The circuit structure of the programmable asynchronous trigger delayer of the present invention is shown in Figure 2, comprises n T' flip-flops, and described n T' flip-flops are connected one by one in turn, and the output terminal of the previous T' flip-flop is connected to the next The CLK ends of the T' flip-flops are connected, and the CLK ends of the first T' flip-flops are connected to the external clock pulse. The SET and RST ends of these T' flip-flops are count value input ends, and the first T ' flip-flop to the nth T' flip-flop respectively corresponding to the lowest bit to the highest bit of the input binary data, the present invention also includes the n+1th T' flip-flop, the CLK terminal of the T' flip-flop is connected to the nth The output terminal of the T' trigger, the output terminal of the T' trigger is a delay signal output terminal, and the number n of the T' trigger is greater than or equal to the binary count obtained by dividing the delay time...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More