Direct calculation method of interface trap in MOS semiconductor field-effect rransistor

A technology of interface defects and measurement methods, applied in semiconductor/solid-state device testing/measurement, semiconductor characterization, single semiconductor device testing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

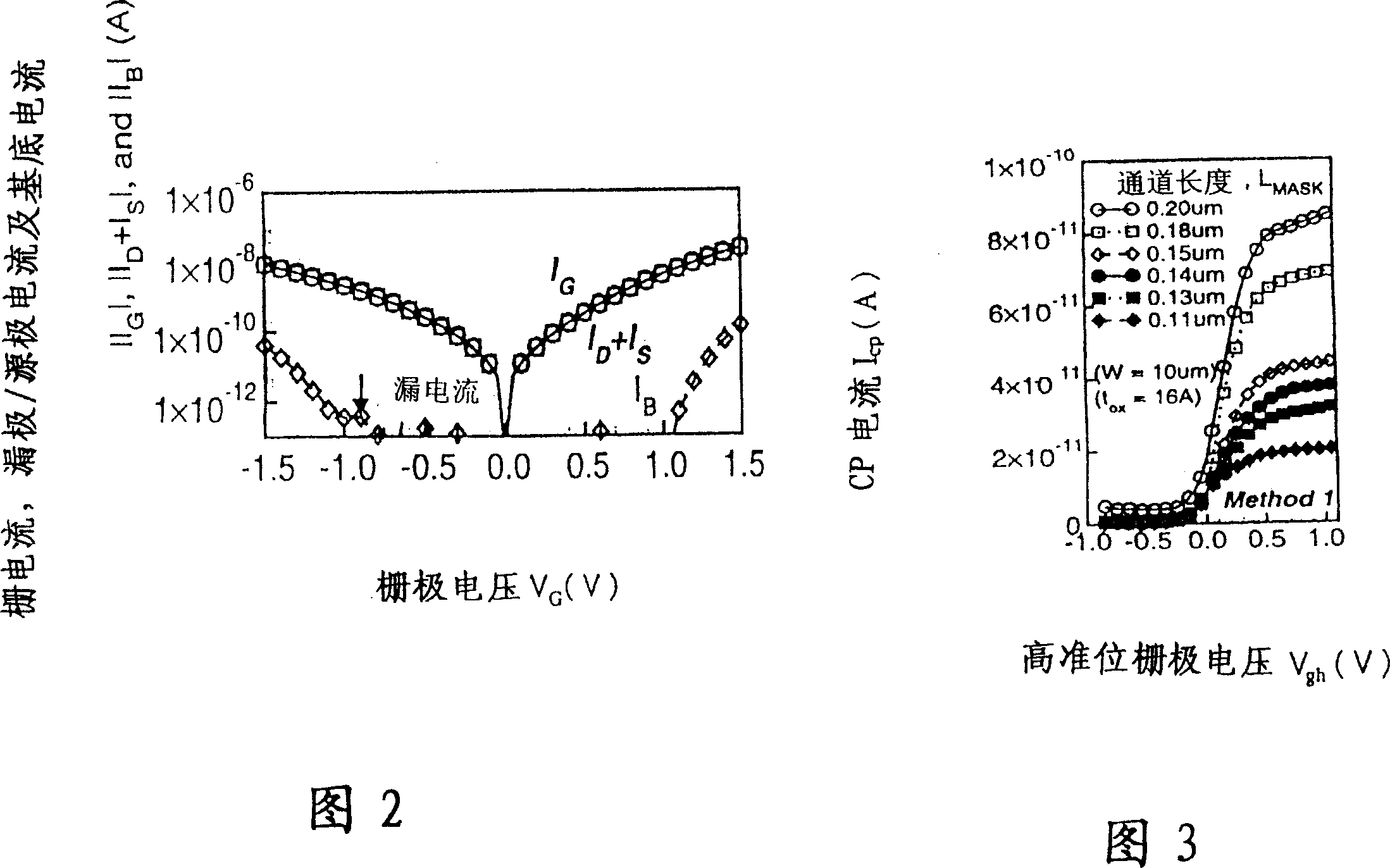

[0028] The present invention provides a method for directly and accurately calculating gate oxide layer interface defects (interface traps, hereinafter referred to as N for short) of advanced MOSFET components. it ) method of quantity. The so-called advanced MOSFET device generally refers to a very short channel length (e.g., actual gate length (L gate ) can be less than 1 micron) and an ultra-thin gate oxide layer with a tunneling leakage effect (e.g., t ox 2 -10 3 order of magnitude tunneling leakage current. In order to make this advanced nanoscale device, photoresist exposure and removal techniques are used, which makes the actual gate length (L gate ) will be longer than the mask exposure length (L mask ) is about 0.04 microns; the actual gate length is designed to be 0.07-0.18 microns. (Note: Of course, this method can also be applied to components whose actual gate length is greater than 1 micron.)

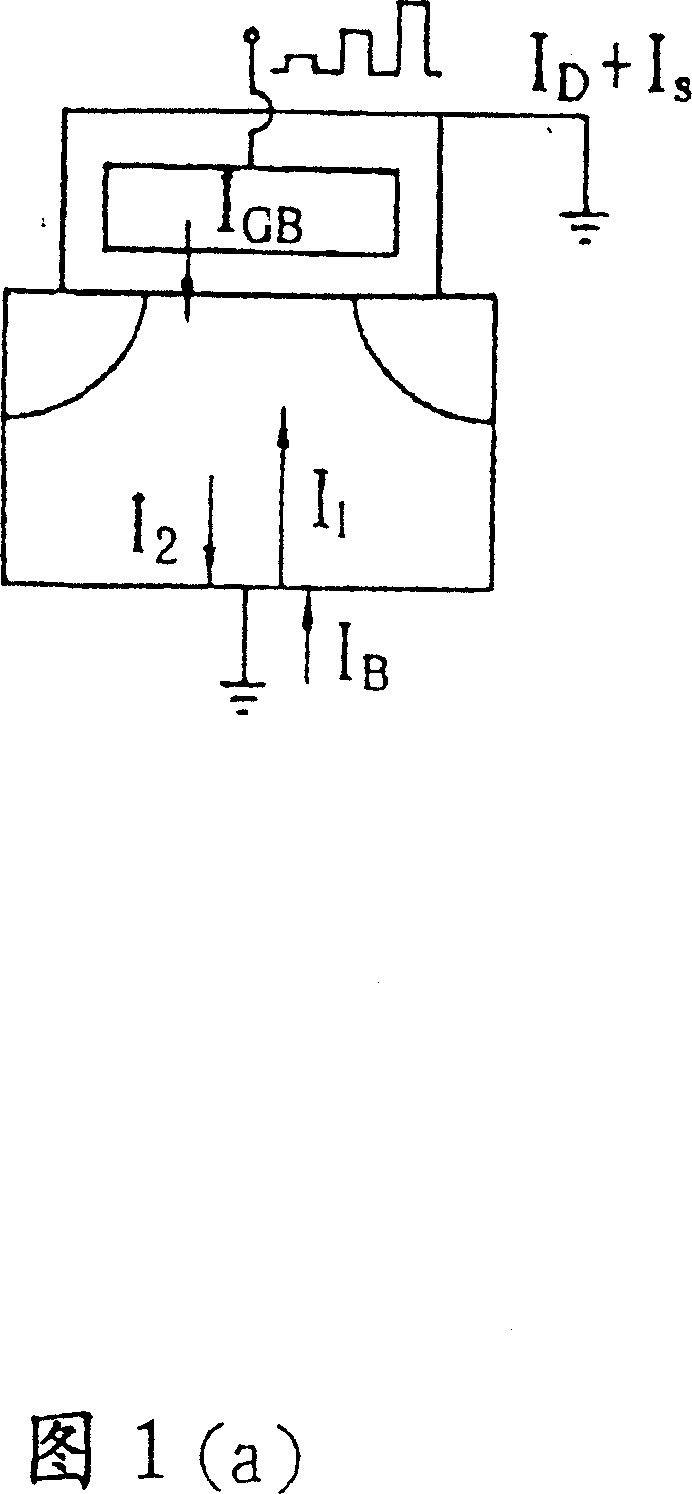

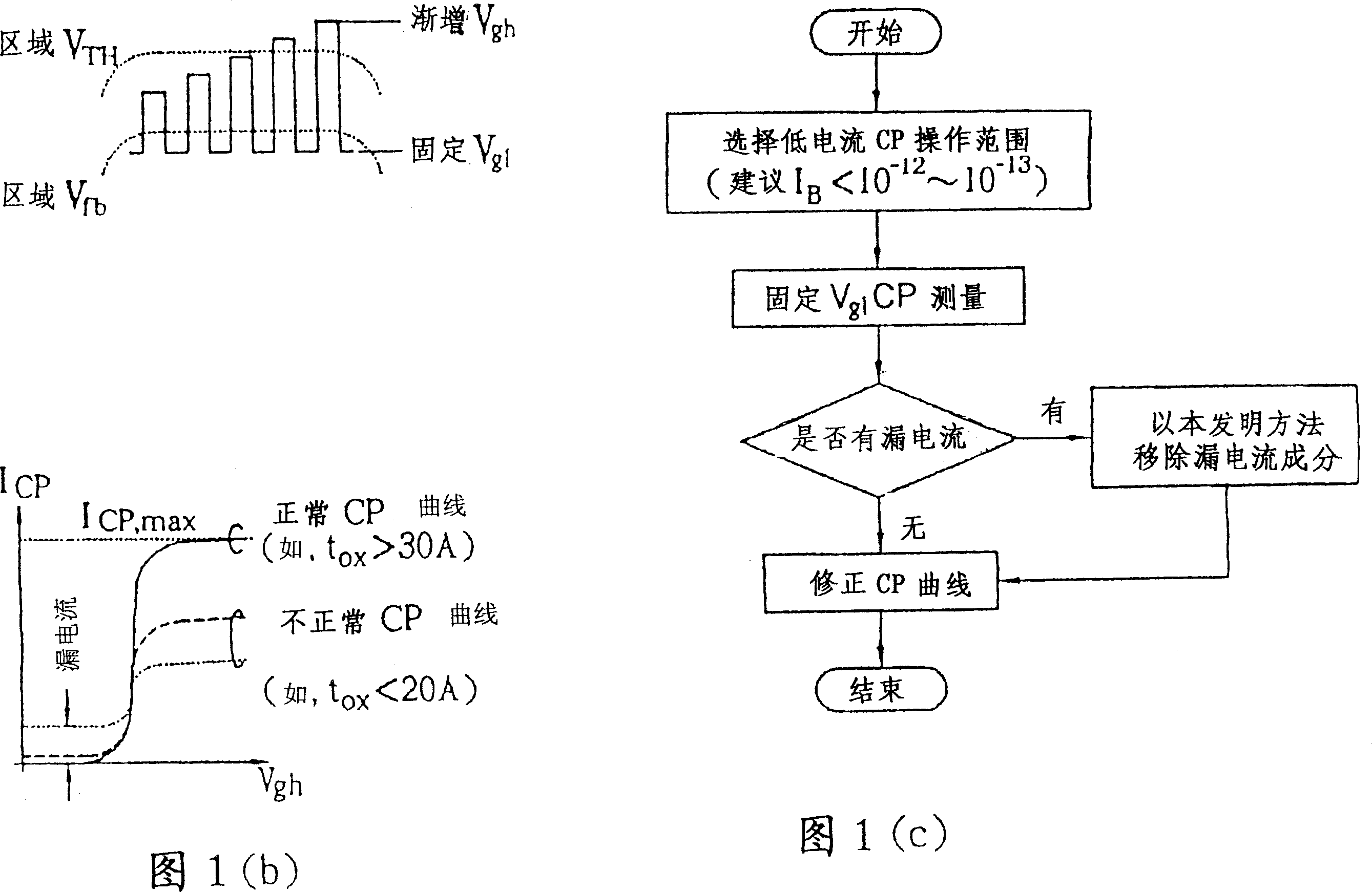

[0029] Please refer to Figure 1(a). This figure discusses the ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More