Semiconductor anti-static protection structure

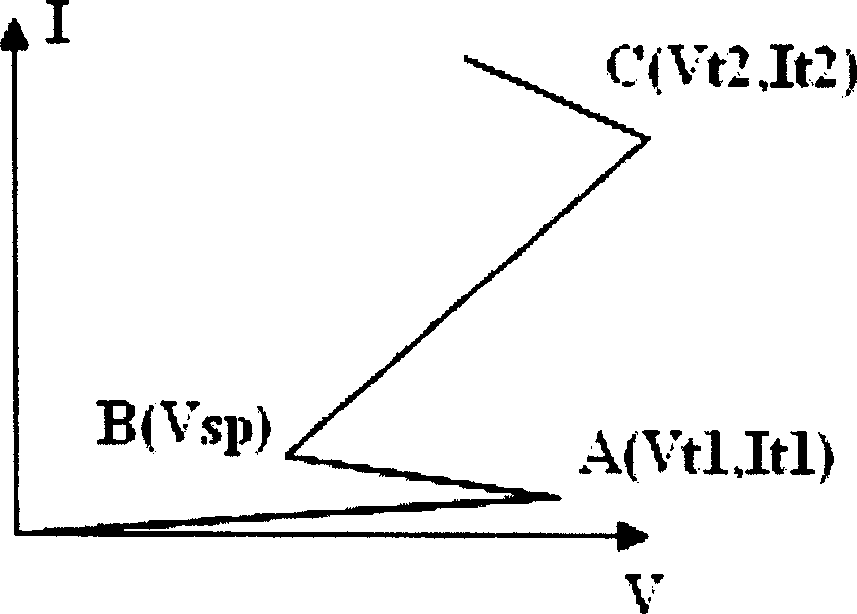

A protection structure and anti-static technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, circuits, etc., can solve the problems of high breakdown voltage and damage, and achieve the effect of reducing the turn-on voltage and making it easier to turn on.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

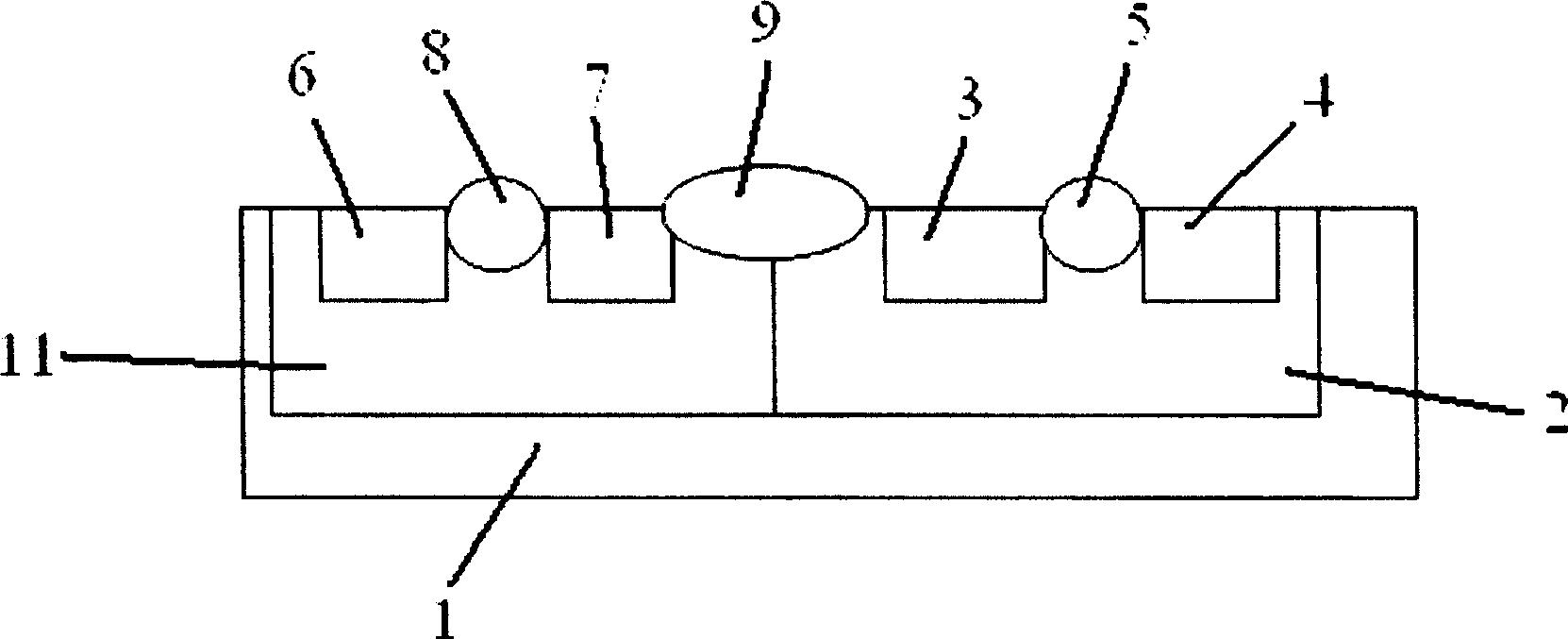

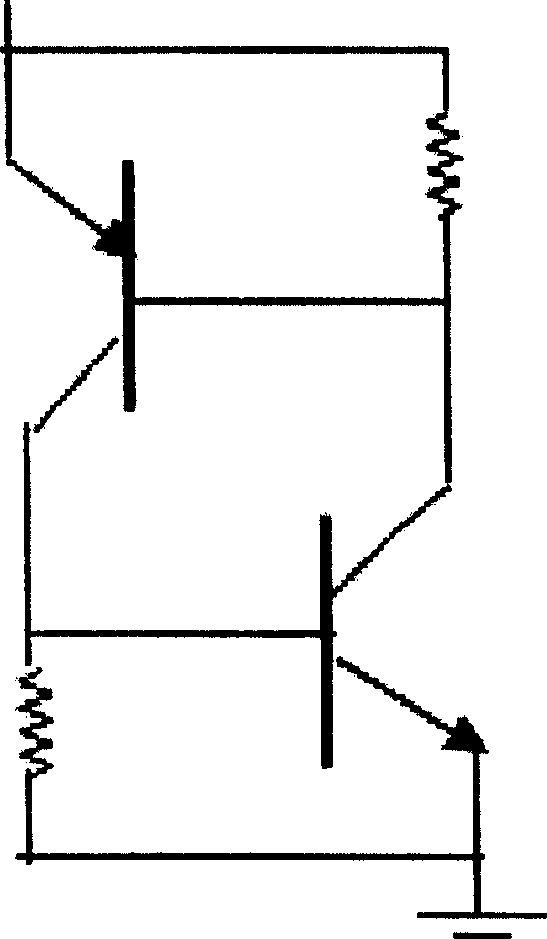

[0014] The semiconductor anti-static protection structure of the present invention can be found in Figure 4 As shown, a P-type substrate 1 is included, and an N-well implantation region 2 and a P-well implantation region 11 are included on the P-type substrate 1; a P-type implantation region 3 is included in the N-well implantation region 2 and an N-type implantation region 4, separated by an oxide layer isolation region 5 between the P-type implantation region 3 and the N-type implantation region 4 in the N-well implantation region 2; the P-well implantation region 11 also includes There is a P-type implanted region 6 and an N-type implanted region 7, and the P-type implanted region 11 of the P-well implanted region 11 is separated by another oxide layer 8 isolation region between the P-type implanted region 6 and the N-type implanted region 7; The P-type implant region 3 in the well implant region 2 is separated from the N-type implant region 7 of the P well implant region ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More