Lateral insulated gate bipolar transistor

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

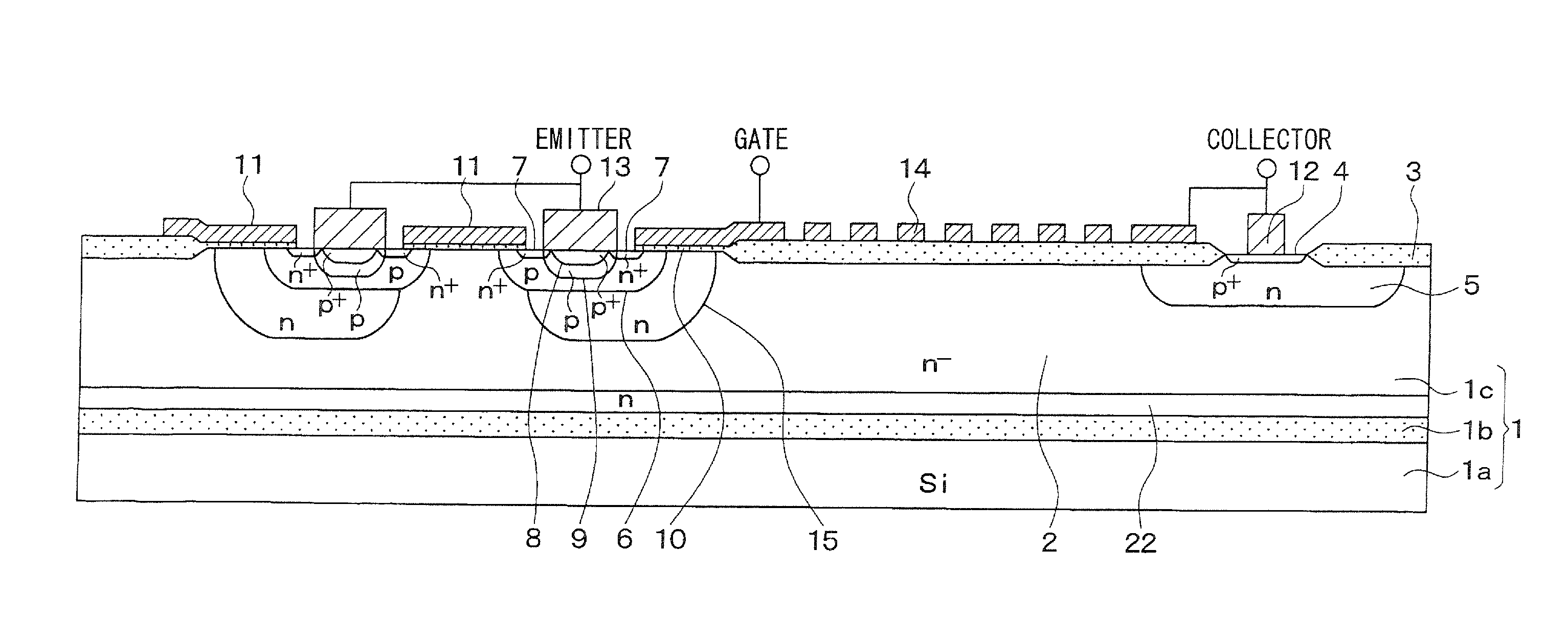

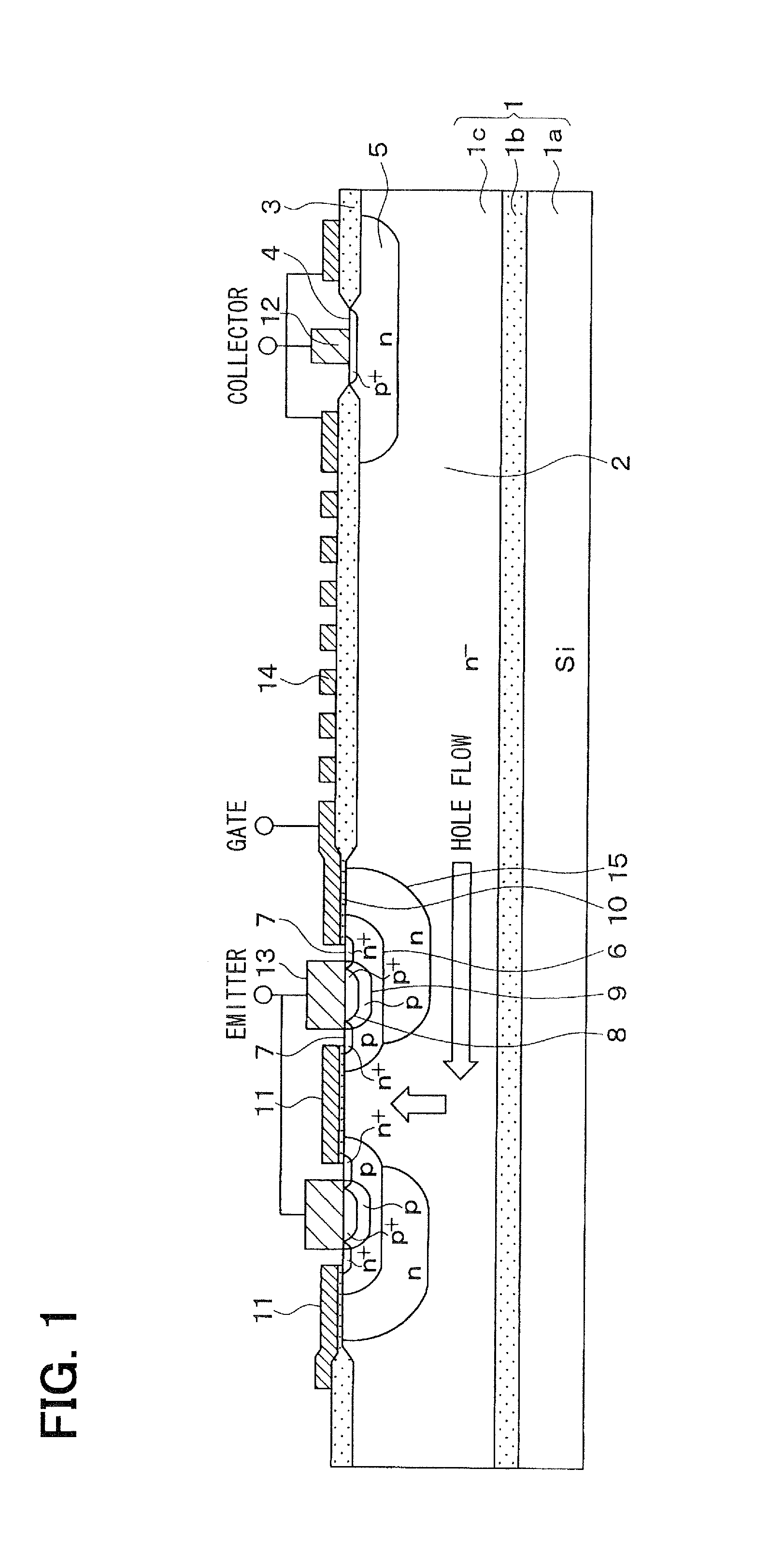

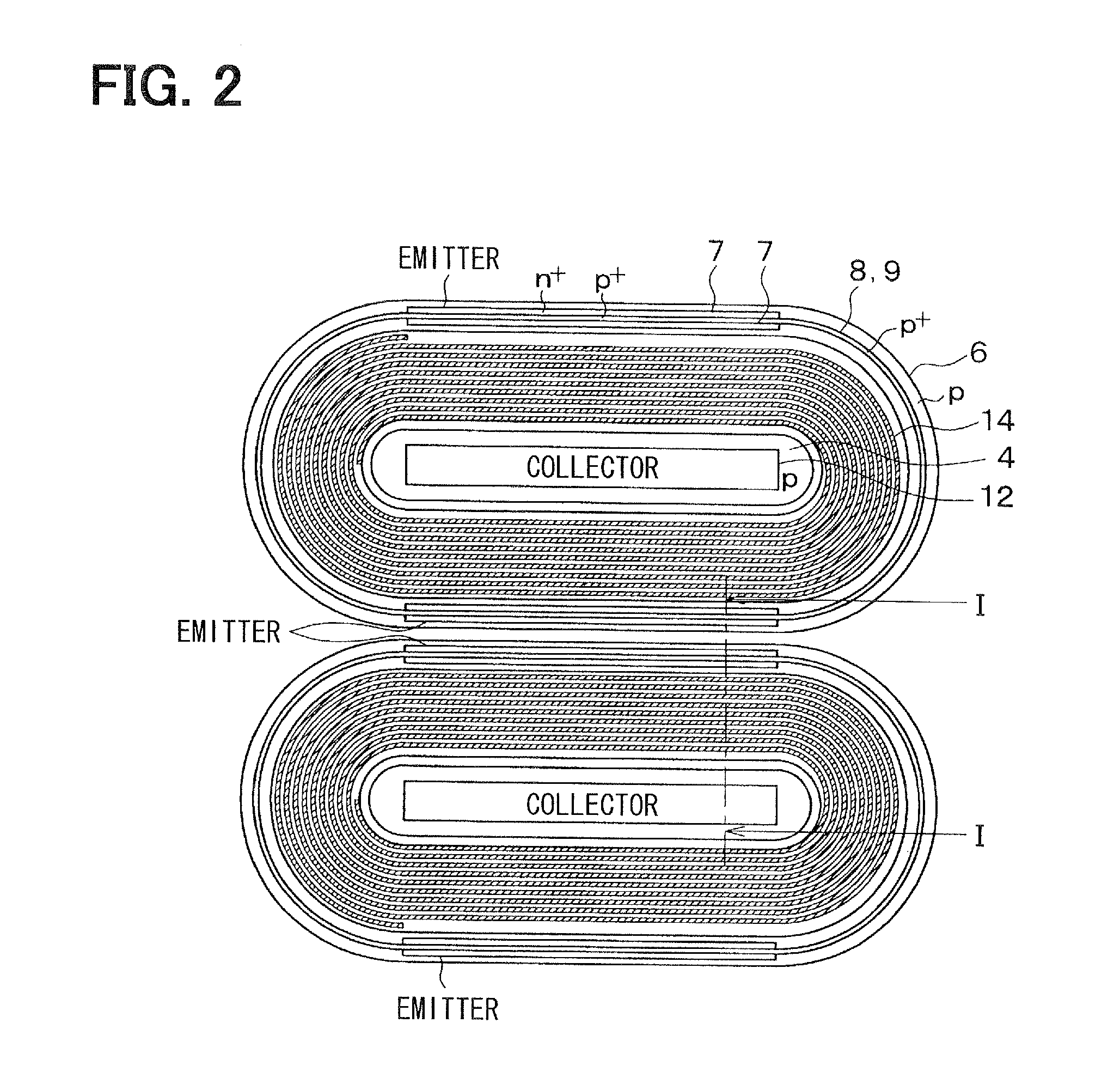

[0047]A lateral IGBT according to a first embodiment of the present invention will be described with reference to FIG. 1 and FIG. 2. FIG. 1 is a cross-sectional view of a semiconductor device including the lateral IGBT according to the present embodiment. FIG. 1 corresponds to a cross-sectional view of the semiconductor device taken along line I-I in FIG. 2.

[0048]As shown in FIG. 1, in the present embodiment, the lateral IGBT is formed using a silicon-on-insulator (SOI) substrate 1. The SOI substrate 1 includes a support substrate 1a made of, for example, silicon, a buried oxide layer 1b disposed on the support substrate 1a, and an active layer 1c made of silicon and disposed on the buried oxide layer 1b. The active layer 1c operates as an n− type drift layer 2. Each component in the lateral IGBT is disposed at a surface portion of the n− type drift layer 2.

[0049]In the SOI substrate 1, the buried oxide layer 1b can have any thickness and the active layer 1c (the n− type drift layer...

second embodiment

[0073]A semiconductor device including a lateral IGBT according to a second embodiment of the present invention will be described with reference to FIG. 7.

[0074]As shown in FIG. 7, in the present embodiment, the n type barrier layer 15 is disposed also between adjacent emitters, that is, between adjacent channel p well layers 6. If the n type barrier layer 15 has an impurity concentration same as the first embodiment, the structure of the lateral IGBT is similar to a structure of a lateral IGBT according to the prior art and the turning-off time increases. Thus, in the present embodiment, an n type impurity peak concentration of the n type barrier layer 15 is set to be within a range from 2×1015 cm−3 to 1.5×1016 cm−3.

[0075]FIG. 8 is a graph showing a relationship between the n type impurity peak concentration of the n type barrier layer 15 and an on-voltage (Von) of the lateral IGBT and a relationship between the impurity concentration of the n type barrier layer 15 and a switching ...

third embodiment

Modifications of Third Embodiment

[0085]The n type barrier layer 15 may be provided in the lateral IGBT according to the third embodiment.

[0086]For example, as shown in FIG. 12, the n type barrier layer 15 may be disposed to a depth deeper than the channel p well layer 6 so as to cover the channel p well layer 6, that is, to couple adjacent trenches 16. As shown in FIG. 13, the n type barrier layer 15 may also be formed so as to extend across the trench 16 located between adjacent cells, that is, to cover the two channel p well layers 6 in the adjacent cells.

[0087]By combining the trench 16 and the n type barrier layer 15, the n type barrier layer 15 can function as a barrier of holes, the carrier concentration of the n− type drift layer 2 in the vicinity of the emitter can be further increased, and the on-voltage can be further reduced. Furthermore, because a parasitic npn transistor provided in the vicinity of the emitter does not operate, an increase in the switching time can be r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More