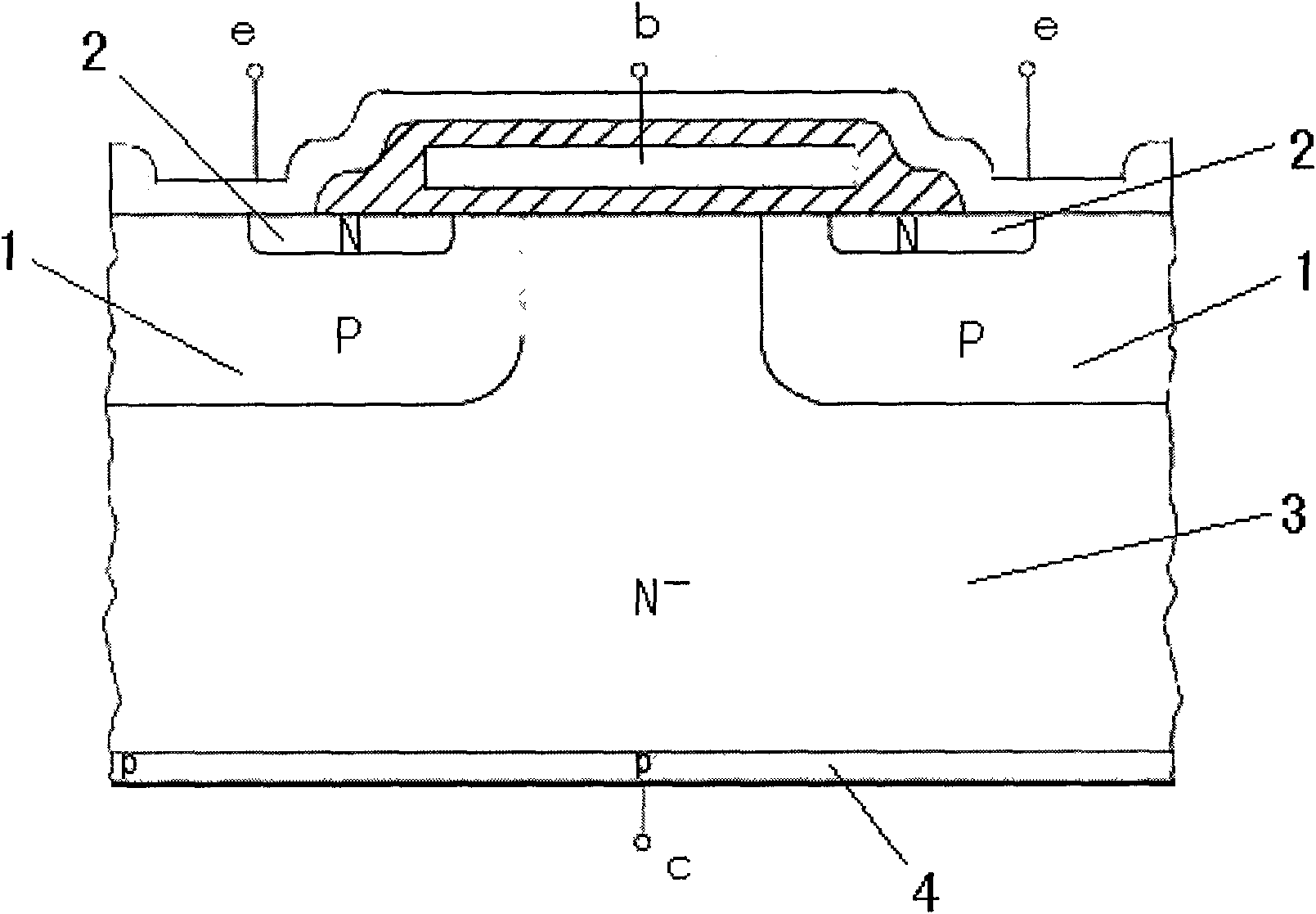

Technique for manufacturing back of non-through insulated-gate bipolar transistor chip

A bipolar transistor, non-punch-through technology, used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of weakening the conductance modulation effect, high on-voltage, and high on-resistance, so as to enhance the conductance modulation effect. , the effect of reducing the on-resistance and on-voltage, and increasing the number of holes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

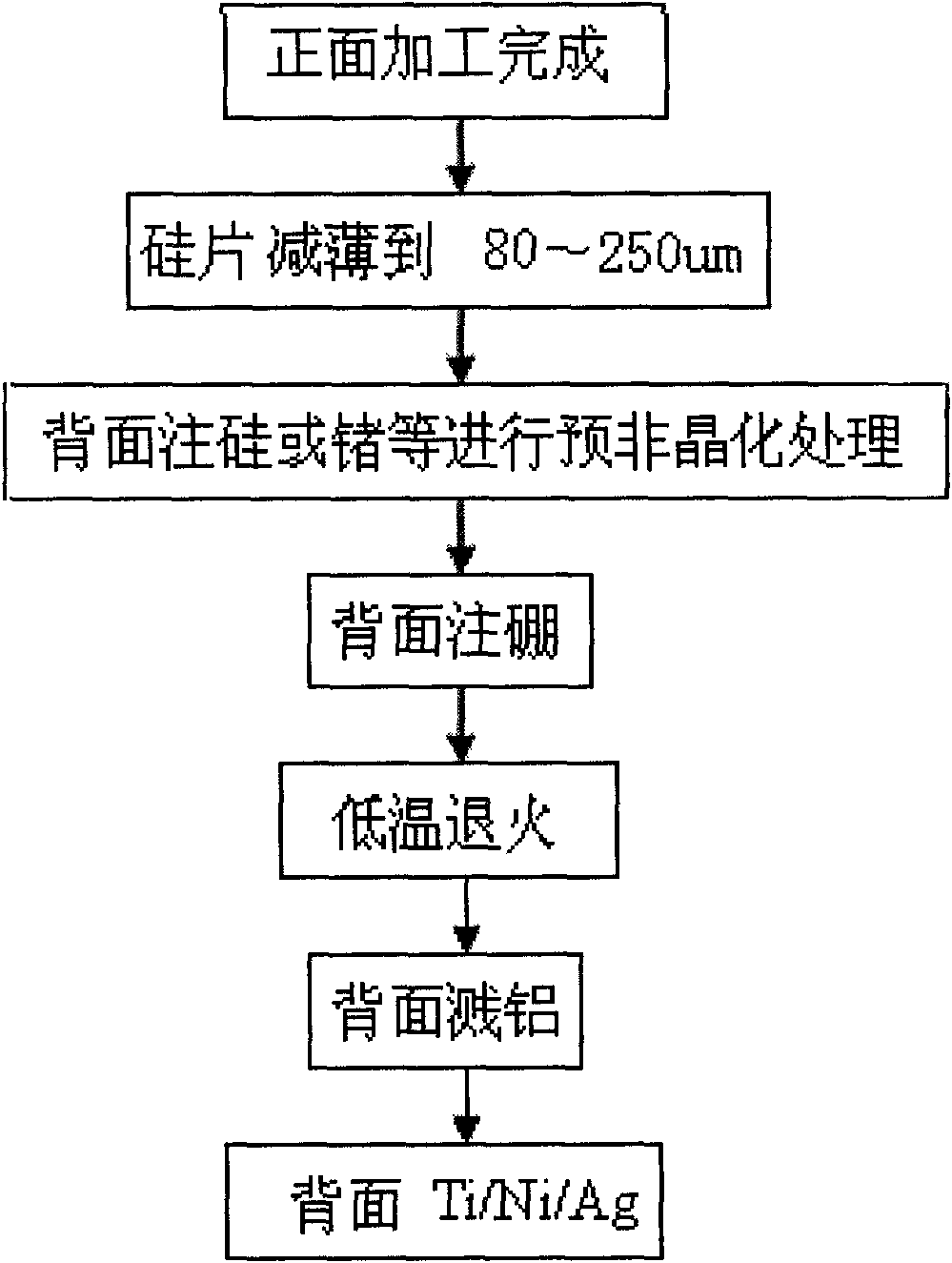

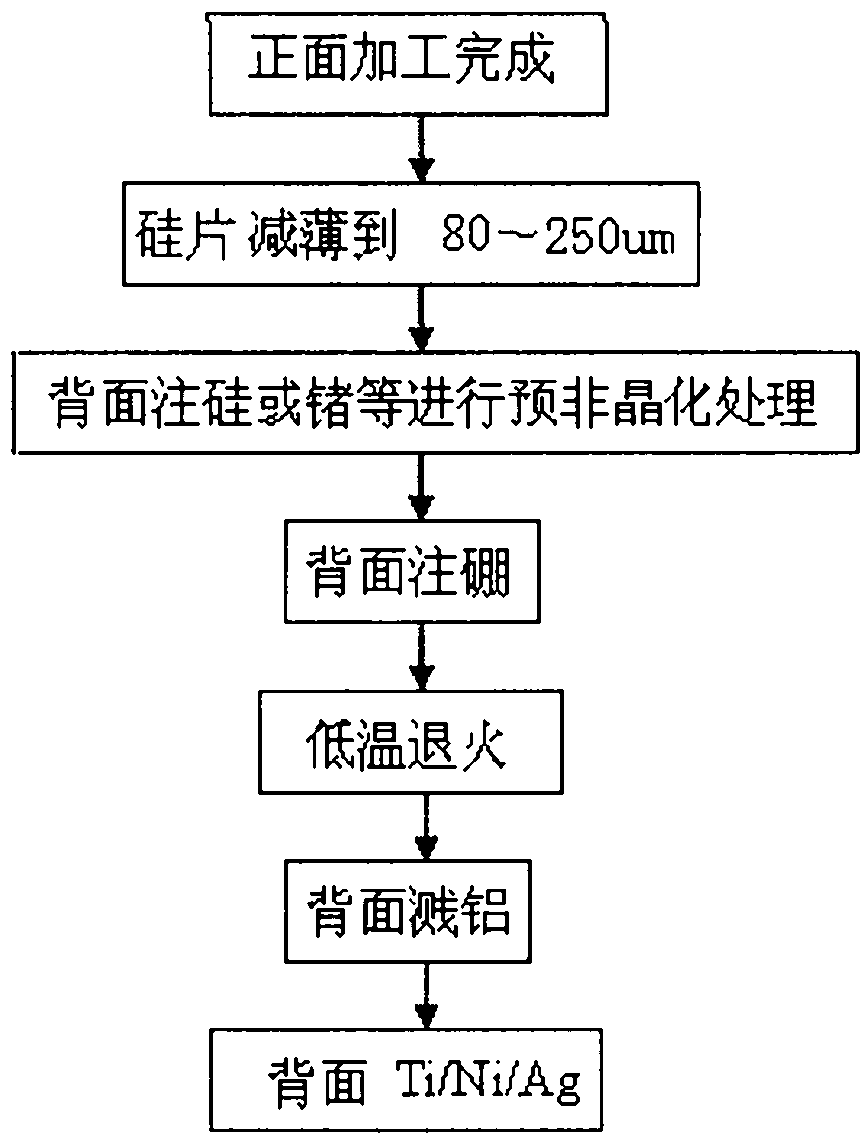

[0013] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

[0014] like figure 2 As shown, the present invention adopts the method of pre-amorphization treatment on the crystal back surface of the insulated gate bipolar transistor (IGBT) and low-temperature heat treatment to improve the boron ion activation of the crystal back of the non-punch-through insulated gate bipolar transistor (NPT IGBT). Rate. The steps are as follows:

[0015] 1) Complete the front-side process of the non-punch-through insulated gate bipolar transistor silicon wafer;

[0016] 2) Using grinding wheel grinding method, from the back of the silicon wafer of the non-punch-through insulated gate bipolar transistor, the silicon wafer is thinned to a thickness of 80-250um, and the necessary stress relief treatment is carried out;

[0017] 3) Implanting silicon ions, germanium ions or boron difluoride ions on the back of the silicon wafer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More