Wafer surface planarization method

A surface planarization and wafer technology, applied in chemical instruments and methods, crystal growth, electrical components, etc., can solve the problem that the wafer edge cannot meet the planarization requirements, and achieve the effect of improving the degree of planarization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

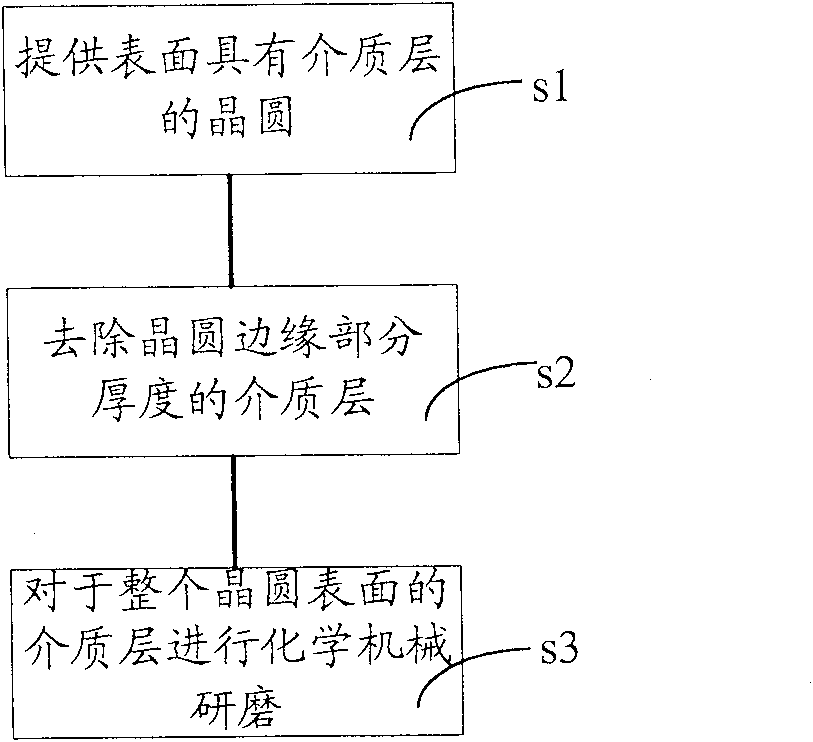

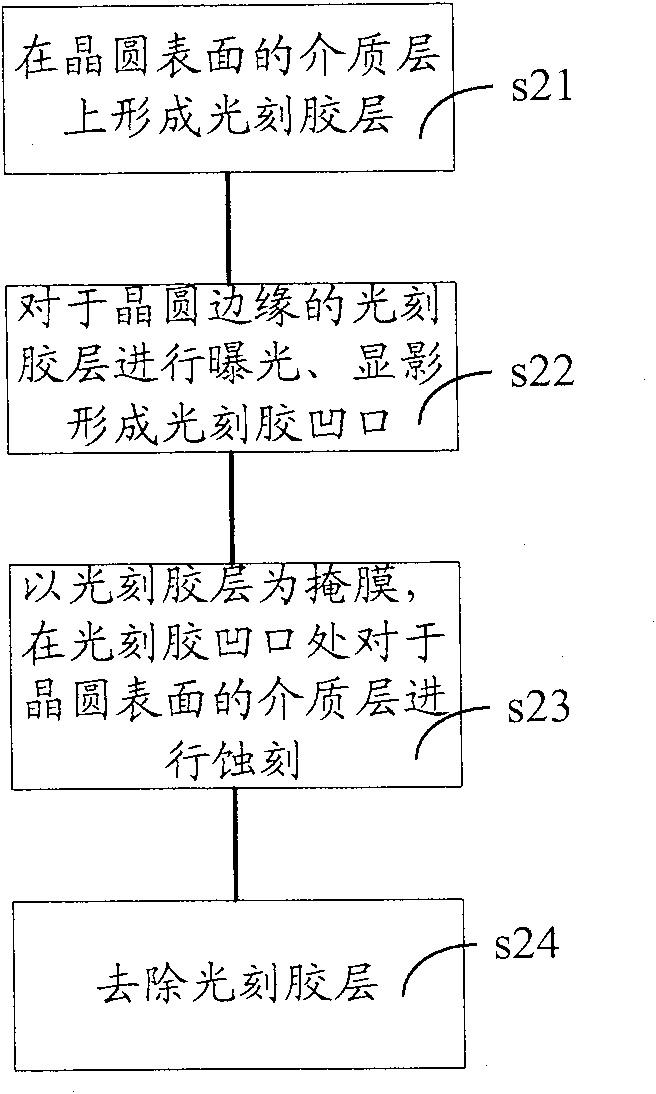

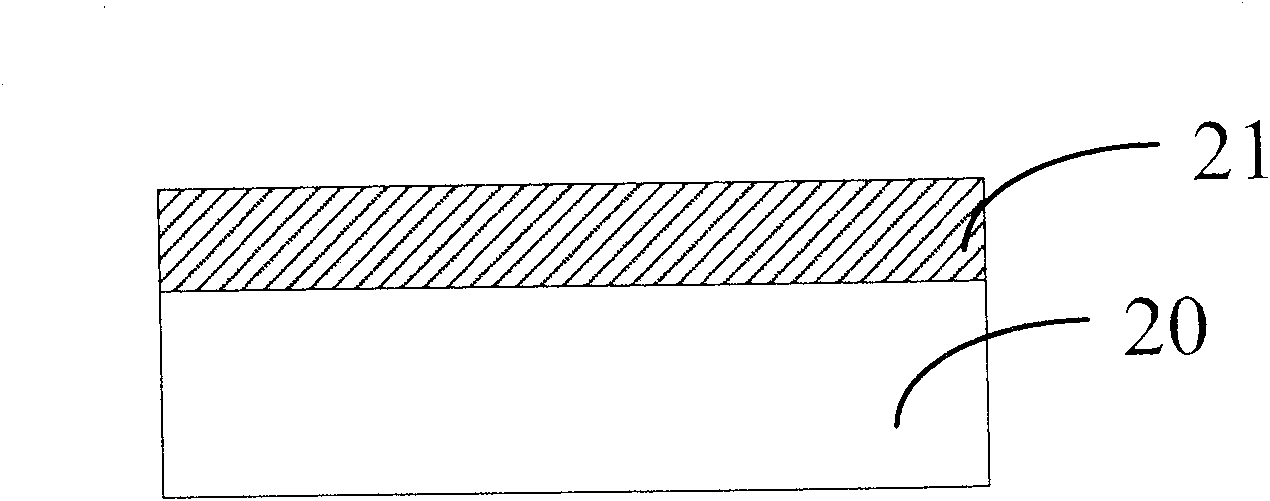

[0018] The essence of the method for planarizing the wafer surface of the present invention is to etch the dielectric layer in the edge region of the wafer to remove a part of the thickness of the dielectric layer before chemically mechanically grinding the dielectric layer on the wafer surface, so as to achieve the desired effect on the wafer after grinding. The purpose of correcting the thickness difference between the dielectric layer in the edge area and the dielectric layer in the center area of the wafer, wherein the edge area is the dielectric layer area where the thickness of the dielectric layer is greater than the depth of the etched through hole after the test piece is ground, and the removal thickness of the dielectric layer is greater than or It is equal to the average thickness difference between the dielectric layer in the central area of the wafer and the dielectric layer in the edge area of the wafer measured by the test piece.

[0019] The method for fla...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More